EE-612: Lecture 24: CMOS Circuits: Part 1 Mark Lundstrom - PowerPoint PPT Presentation

EE-612: Lecture 24: CMOS Circuits: Part 1 Mark Lundstrom Electrical and Computer Engineering Purdue University West Lafayette, IN USA Fall 2006 NCN www.nanohub.org Lundstrom EE-612 F06 1 Outline 1) Review 2) CMOS circuits 3) The CMOS

EE-612: Lecture 24: CMOS Circuits: Part 1 Mark Lundstrom Electrical and Computer Engineering Purdue University West Lafayette, IN USA Fall 2006 NCN www.nanohub.org Lundstrom EE-612 F06 1

Outline 1) Review 2) CMOS circuits 3) The CMOS inverter 4) Speed Lundstrom EE-612 F06 2

MOSFETs PMOS NMOS I D V GS − V GS V DS Lundstrom EE-612 F06 3

output conductance ( ) − 1 o = ∂ I D / ∂ V DS r ( ) I D = I DSAT 1 + λ V DS I D channel length modulation ‘DIBL above threshold’ V DS Lundstrom EE-612 F06 4

small signal gain V DD R D V OUT + A V υ S sin ω t ( ) A V = − g m R D || r V BIAS + υ S sin ω t o N r o g m = ∂ I D ∂ V GS V DS Lundstrom EE-612 F06 5

Outline 1) Review 2) CMOS circuits 3) The CMOS inverter 4) Speed 5) Power 6) Circuit performance Lundstrom EE-612 F06 6

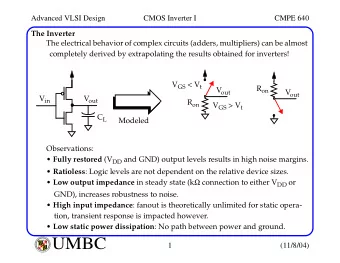

ideal CMOS inverter transfer characteristic V DD S B V DD PMOS V OUT --> D V IN V OUT D NMOS V DD V DD /2 S B V IN --> Lundstrom EE-612 F06 7

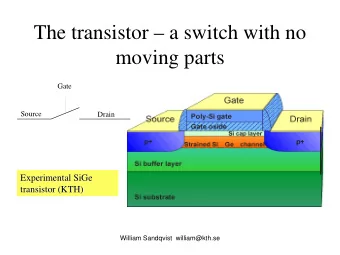

CMOS inverter (cross-section) Courtesy of Dr. Lynn Fuller of Rochester Institute of Technology. http://www.rit.edu/~lffeee/AdvCmos2003.pdf Lundstrom EE-612 F06 8

CMOS inverter (top view) Lundstrom EE-612 F06 9

technology-independent design rules alignment 2 λ Resolution 2 λ λ λ minimum gate length = 2 λ W min = 4 λ minimum linewidth = 2-3 λ 2 λ × 2 λ (for this layout) minimum line spacing = 2-3 λ λ Lundstrom EE-612 F06 10

2-input NAND gate V AND dd A B C 0 0 0 0 1 0 P1 P2 1 0 0 V C 1 1 1 out V A N1 in1 NAND A B C 0 0 1 V B N2 0 1 1 in2 1 0 1 1 1 0 Lundstrom EE-612 F06 11

dynamic logic: NOR gate V DD A B C OUT 0 0 0 1 φ precharge 0 1 0 0 V out V IN C L A C B φ eval eval V DD φ evaluate pre pre Lundstrom EE-612 F06 12

dynamic logic V DD • M-input logic needs M+2 transistors (2M for CMOS) φ precharge V out • ‘no’ standby power C L • minimum frequency Logic function φ evaluate Lundstrom EE-612 F06 13

transmission gates C C A A B B C C Lundstrom EE-612 F06 14

transmission gates: high to low C = 0 V G D S A = 0 V V DD → 0 V B : S D G C = V DD V NMOS can discharge the output all the way to 0V; PMOS can’t. Lundstrom EE-612 F06 15

transmission gates: low to high C = 0 V G S D A = V DD V 0 → V DD V B : D S G C = V DD V PMOS can charge the output all the way to V DD V; NMOS can’t. Lundstrom EE-612 F06 16

multiplexer with transmission gates S A S F = AS + BS B From Hodges, Jackson, and Saleh, Analysis and Design of Digital Integrated Circuits, 3rd Ed., McGraw-Hill, 2004. Lundstrom EE-612 F06 17

memories memory array bit lines SRAM row decoder word lines DRAM Flash, etc. memory cell column decoder sense amp write driver Lundstrom EE-612 F06 18

SRAM cell wordline 1 0 2 0 1 0 1 1 0 1 access transistors bitline bitline Lundstrom EE-612 F06 19

6 transistor SRAM cell V DD bitline bitline wordline Lundstrom EE-612 F06 20

6 transistor SRAM cell (ii) • SRAM consumes most of the area on a CPU chip • steady state power determined by leakage (use high V T ) • small area with optimized layout • minimum W / L - sensitive to variations Lundstrom EE-612 F06 21

for more information on CMOS circuits Hodges, Jackson, and Saleh, Analysis and Design of Digital Integrated Circuits, 3rd Ed., McGraw-Hill, 2004. Lundstrom EE-612 F06 22

Outline 1) Review 2) CMOS circuits 3) The CMOS inverter 4) Speed Lundstrom EE-612 F06 23

CMOS inverter transfer characteristic V DD S B V DD PMOS V OUT --> D V DD /2 V IN V OUT D NMOS V DD V DD /2 S B V IN --> Lundstrom EE-612 F06 24

CMOS inverter: voltages V DD S B V gs = V in − V DD PMOS V ds = V out − V DD D V IN V OUT D V gs = V in NMOS V ds = V out S B Lundstrom EE-612 F06 25

CMOS inverter: transfer characteristric V gs = V in V gs = V in − V DD 0 → V DD V in : V ds = V out V ds = V out − V DD V gs = V DD I D V gs = − V DD V gs = 0 V gs = 0 V DS V out Lundstrom EE-612 F06 26

sizing the P-MOSFET 130 nm technology (L G = 60 nm) PMOS NMOS W P ≈ 2 W N I-V curves for low V T device Intel Technical J., Vol. 6, May 16, 2002. Lundstrom EE-612 F06 27

CMOS inverter: V out vs. V in V DD = 1.0 V V TN = − V TP = 0.15 V I D V in = 1.0 V in = 0 V in = 0.8 V in = 0.2 V in = 0.6 V in = 0.4 V in = 0.4 V in = 0.6 4 3 V in = 0.8 V in = 0.2 2 5 V in = 0 V in = 1.0 V out 6 1 V DD Lundstrom EE-612 F06 28

CMOS VTC V out NMOS OFF PMOS LIN V DD NMOS SAT V DD PMOS LIN 1 2 3 S B NMOS SAT D PMOS SAT V OUT V DD 2 V IN D NMOS LIN PMOS SAT NMOS LIN 4 PMOS OFF S B 5 6 V T V DD 2 V DD V in Lundstrom EE-612 F06 29

CMOS inverter: current V out I D NMOS OFF PMOS LIN NMOS SAT V DD PMOS LIN cross-over current NMOS SAT PMOS SAT V DD 2 NMOS LIN PMOS SAT NMOS LIN PMOS OFF V T V DD 2 V DD V T V DD 2 V DD V in V in Lundstrom EE-612 F06 30

CMOS inverter: noise margins V out V DD slope = -1 V DD S B NM L D V OUT V DD 2 V IN D NM H S B slope = -1 V in V DD Lundstrom EE-612 F06 31

importance of gain V out dV out ( ) r ( ) V DD = A υ = − g mn + g mp on || r op dV in V DD 2 must have gain to A υ = 1 have noise margins V in V DD Lundstrom EE-612 F06 32

approximate noise margins V out NM L V DD dV out ( ) r ( ) = A υ = − g mn + g mp on || r op dV in V DD 2 NM L ≈ NM H ≈ V DD 1 − 1 2 A υ V in V DD V DD 2 Lundstrom EE-612 F06 33

CMOS inverter: summary ‘pull up’ 1) little current flow (power dissipation) transistor V DD unless switching S B 2) good noise margins if device has high R OUT (high gain) D V OUT V IN D next: understand speed and power S B ‘pull down’ transistor Lundstrom EE-612 F06 34

Outline 1) Review 2) CMOS circuits 3) The CMOS inverter 4) Speed Lundstrom EE-612 F06 35

CMOS inverter input voltage ( ) V in t V DD V DD S B t 0 t D V OUT V IN output voltage ( ) V out t + D ( ) V DD V DD − C t − t 0 - S B ~ e − t / τ t 1 t 0 t Lundstrom EE-612 F06 36

discharging time ( ) quasi-static assumption I D t simplified I D - V DS I N + ( ) t 1 D I N on ( ) t 0 C TOT V out t - V IN S B V DSAT V DS ( ) dV out t τ = R CH C TOT R CH = V DSAT / I N (on) I d ( t ) = − C TOT dt ( ) = V out ( t 1 ) e − t / τ ( ) = V DD − I N (on) V out t ( ) t − t 0 V out t C T t 0 < t < t 1 t 0 < t < t 1 Lundstrom EE-612 F06 37

propagation delay (H-L) ( ) I D t output voltage ( ) V out t + D ( ) C TOT ( ) V out t V DD V DD − C t − t 0 - V IN V DD / 2 S B ~ e − t / τ t 1 t 0 t τ n τ n = C TOT V DD ( ) = V DD − I N (on) ( ) 2 I N (on) ≡ R swn C TOT t − t 0 t 0 < t < t 1 V out t C T V DD / 2 = V DD − I N (on) τ n V DD k n = 1 R swn = k n C TOT I N (on) 2 Lundstrom EE-612 F06 38

loaded propagation delay ( ) R swn + R swp τ = τ n + τ p V DD = C TOT 2 2 C in C out C wire C in V IN C in C TOT C TOT = C out + C L + FO × C in interconnect C Lundstrom EE-612 F06 39

use of buffers V DD ( ) τ = R sw C out + C L V IN Can we do better? C TOT >> C in Lundstrom EE-612 F06 40

delay with buffers ( ) τ = R sw C out + C L V DD τ buf = τ 1 + τ 2 ( ) τ 1 = R sw C out + kC in 2 W P kW P τ 2 = R sw ( ) kC out + C L k V IN C TOT >> C in kW N W N Lundstrom EE-612 F06 41

delay with buffers (ii) ) + R sw ( ) ( ( ) τ = R sw C out + C L τ buf = R sw C out + kC in kC out + C L k τ buf = τ 1 + τ 2 τ buf = R sw 2 C out + kC in + C L ( ) τ 1 = R sw C out + kC in 2 k τ 2 = R sw ( ) d τ buf kC out + C L C L = 0 ⇒ k min = k dk C in ( ) τ buf (min) = R sw 2 C out + 2 C in C L C L >> C in , C out For very heavy loads, use multi-stage buffers. See Taur and Ning, HW probs. 5.7 - 5.10 τ buf τ = 2 C in / C L << 1 Lundstrom EE-612 F06 42

delay vs. load C ( ) R swn + R swp ( ) τ = C TOT = R sw C out + FO × C in + C wire 2 FO = 3 FO = 2 FO = 1 τ see Fig. 5.29 Taur and Ning ( ) τ int = R sw C out + C in C wire Lundstrom EE-612 F06 43

C in and C out C OV C OV V D 0 n+ n+ p-Si [ ] [ ] C in = C G + C OV + C OV N + C G + C OV + C OV P C GN = C OX W N L [ ] [ ] C out = C J + C OV N + C J + C OV P Lundstrom EE-612 F06 44

Miller C C OV C OV - + V D 0 n+ n+ p-Si capacitors connected between input and output require a special treatment Lundstrom EE-612 F06 45

Outline 1) Review 2) CMOS cirsuits 3) The CMOS inverter 4) Speed to be continued…… Lundstrom EE-612 F06 46

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.