EE-612: Lecture 25: CMOS Circuits: Part 2 Mark Lundstrom - PowerPoint PPT Presentation

EE-612: Lecture 25: CMOS Circuits: Part 2 Mark Lundstrom Electrical and Computer Engineering Purdue University West Lafayette, IN USA Fall 2006 NCN www.nanohub.org Lundstrom EE-612 F06 1 Outline 1) Review 2) Speed (continued) 3) Power

EE-612: Lecture 25: CMOS Circuits: Part 2 Mark Lundstrom Electrical and Computer Engineering Purdue University West Lafayette, IN USA Fall 2006 NCN www.nanohub.org Lundstrom EE-612 F06 1

Outline 1) Review 2) Speed (continued) 3) Power 4) Circuit performance Lundstrom EE-612 F06 2

CMOS inverter transfer characteristic V DD noise margins S B V DD PMOS --> D OUT V DD /2 V IN V OUT V D NMOS V DD V DD /2 S B V IN --> Lundstrom EE-612 F06 3

importance of gain V out ( ) r ( ) > 1 dV out = A υ = g mn + g mp V DD on || r op dV in V DD 2 must have gain to A υ = 1 have noise margins V in V DD Lundstrom EE-612 F06 4

outline 1) Review 2) Speed (continued) 3) Power 4) Circuit performance Lundstrom EE-612 F06 5

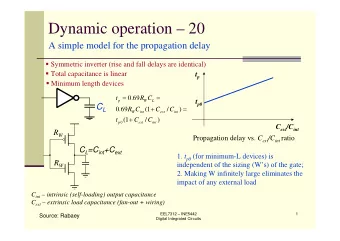

CMOS inverter speed ⎛ ⎞ V DD τ = 1 C TOT V DD 2 I N (on) + C TOT V DD ⎜ ⎟ ⎝ ⎠ 2 2 I P (on) S ( ) τ = R swN + R swP C TOT 2 D V OUT τ = R sw C TOT V IN + D k n > 1 V DD C TOT R swn = k n 2 - I N (on) S Lundstrom EE-612 F06 6

loaded propagation delay V DD C TOT = C out + C L + FO × C in C in C out C wire C in V IN C in C TOT Lundstrom EE-612 F06 7

Miller C C OV “feed forward” C OV - + V D 0 V DD n+ n+ 0 C M = 2 C OV V DD p-Si 0 V c ( t << 0) = − V DD Δ V c = 2 V DD Δ Q c = Δ V c C OV = 2 V DD C OV = C M V DD V c ( t >> 0) = + V DD Lundstrom EE-612 F06 8

on-current determines circuit speed τ = R sw C TOT R sw ~ V DD / I D (ON) V DD S I N ( ) I N on D V OUT V IN + D V DSAT C TOT V DS - S 1) quasi-static assumption 2) simplified I D - V DS Lundstrom EE-612 F06 9

metrics for circuit speed K.K. Ng, et al., “Effective On-Current of MOSFETs for Large-Signal Speed Consideration,” IEDM, Dec., 2001. M.H. Na, et al., “The Effective Drive Current in CMOS Inverters,” IEDM, Dec., 2002. J. Deng and H.S.P. Wong, “Metrics for Performance Benchmarking of Nanoscale Si and Carbon Nanotube FETs Including Device Nonidealities,” IEEE Trans. Electron Dev ., 53 , pp. 1317-1366, 2006. R. Venugopal, et al., “Design of CMOS Transistors to Maximize Circuit FOM Using a Coupled Process and Mixed Mode Simulation Methodology,” IEEE Electron Dev . Lett., 53 , pp. 1317-1366, 2006. Lundstrom EE-612 F06 10

11 Lundstrom EE-612 F06 outline 4) Circuit performance 1) Review 3) Power 2) Speed

12 2 C TOT V DD 2 1 + - C TOT Lundstrom EE-612 F06 power V DD V IN t T V in ( t ) V DD 0

discharge cycle E C (0) = 1 2 + 2 C TOT V DD 1 2 C TOT 2 C TOT V DD V in ( t ) - E C ( T / 2) = 0 dynamic = Δ E 2 T / 2 = C TOT V DD P T V in ( t ) T / 2 V DD dynamic = α f C TOT V DD 2 P 0 t switching activity Lundstrom EE-612 F06 13

discharge through a resistor R - + V C ( t ) = V c (0) e − t / RC TOT = V DD e − t / τ + C TOT R ( t ) = V C V c ( t ) 2 ( t ) R P V in ( t ) - T /2 ∫ R ( t ) dt P AVE = 0 P T / 2 V in ( t ) T /2 2 T / 2 = 2 V DD ∫ e − 2 t / τ dt V DD T R 0 0 = f C TOT V DD 2 t Lundstrom EE-612 F06 14

charging cycle V DD does it take power to put energy in the capacitor? V IN + 1 2 C TOT 2 C TOT V DD - Lundstrom EE-612 F06 15

charging cycle (ii) E C (0) = 0 E C ( T / 2) = 1 2 + 2 C TOT V DD C TOT V c ( t ) V ( t ) - T /2 ∫ E B = i ( t ) dt V DD 0 T /2 ∫ E B = V DD dt = V DD Q V ( t ) i ( t ) T / 2 0 V DD E B = V DD Q = C TOT V DD 2 0 E diss = 1 2 2 C TOT V DD t Lundstrom EE-612 F06 16

charging cycle (iii) dV c i ( t ) = C TOT R - + dt + ( ) R V c ( t ) = V DD − i t C TOT V c ( t ) V ( t ) - di i ( t ) = − RC TOT dt i ( t ) = i (0 + ) e − t / τ = V DD R ( ) e − t / τ V ( t ) T / 2 T /2 ∫ V DD E B = = C TOT V DD 2 V DD i ( t ) dt 0 0 E diss = 1 2 2 C TOT V DD t Lundstrom EE-612 F06 17

adiabatic charging dV V DD R - i ( t ) = C TOT dt = C TOT + T + C TOT V c ( t ) 2 ⎛ ⎞ V ( t ) C TOT V DD - R = i 2 R = ⎜ ⎟ P R ⎝ ⎠ T 2 V DD T 2 = C TOT ∫ E diss = P R dt RT V ( t ) T 2 0 V DD ⎛ ⎞ 0 RC TOT E diss = C TOT V DD t 2 ⎜ ⎟ ⎝ ⎠ T T Lundstrom EE-612 F06 18

outline 1) Review 2) Speed 3) Power 4) Circuit performance 5) CMOS circuit metrics Lundstrom EE-612 F06 19

device impact on circuit performace Question: Given a technology, how does circuit performance depend on transistor design ( W , T OX , V DD , etc.) Taur and Ning assume a 250nm technology and explore this question by Spice simulation (see pp. 264 - 279). Can we understand the major trends simply? Lundstrom EE-612 F06 20

effect of transistor W on delay ( ) R swn + R swp τ = C TOT = R sw C TOT 2 C TOT = C out + C wire + FO × C in R sw = kV DD I D (on) I (on) ~ W C out ~ W C in ~ W R sw ~ 1/ W Lundstrom EE-612 F06 21

loaded vs. unloaded delay ( ) τ = R sw C TOT = R sw C out + FO × C in + C wire i) unloaded: C in and C out dominate, C TOT ~ W --> τ independent of W ii) loaded: C L dominates, C TOT ~ independent of W --> τ ~1/ W Lundstrom EE-612 F06 22

effect of T OX on delay ( ) τ = R sw C TOT = R sw C out + FO × C in + C L i) intrinsic delay ( C L = 0) R sw = kV DD / I D (ON) ~ T OX τ int ~ constant C in ~ 1/ T OX constant C out ii) loaded delay ( C L > 0) τ loaded ↑ T OX ↑ as τ loaded ≈ R sw C L (see Fig. 5.32 of Taur and Ning ) Lundstrom EE-612 F06 23

effect of L on delay ( ) τ = R sw C TOT = R sw C out + FO × C in + C L R sw = kV DD / I D (ON) ( ) ↓ as L ↑ I D ( ON ) = W C OX υ (0) V GS − V T R sw ↑ as L ↑ τ ↑ L ↑ as C in ~ L C out , C L constant (see Fig. 5.31 of Taur and Ning ) Lundstrom EE-612 F06 24

effect of V DD on delay ( ) τ = R sw C TOT = R sw C out + FO × C in + C L R sw = kV DD / I D (ON) ( ) I D ( ON ) = W C OX υ (0) V GS − V T 1 ( ) τ ~ V DD − V T R sw ~ V DD 1 − V T V DD ( ) R sw ~ 1 1 − V T V DD C out = ε Si W D ~ 1 V DD + V bi Lundstrom EE-612 F06 25

delay vs. V DD τ 1 τ ~ 1 − V T V DD V T V DD = 0.2 fixed V T V DD V T I D (off) ~ e − qV T / mk BT (see Fig. 5.33 of Taur and Ning ) Lundstrom EE-612 F06 26

power-delay trade-off circuit speed: ( ) ( ) τ ~ V DD V DD − V T f ~ 1 − V T V DD dynamic (switching) power: ( ) 2 ~ V DD dynamic = α fC TOT V DD 1 − V T V DD 2 P static (leakage) power: static ~ I D (OFF) V DD ~ e − qV T / mk B T V DD P Lundstrom EE-612 F06 27

power-delay trade-off ( ) 1 − V T V DD 2 dynamic ~ V DD P ( ) speed ~ 1 − V T V DD decreasing active power increasing speed LSP V T decreasing leakage power static ~ e − qV T / mk B T V DD P HP V DD (see Fig. 5.34 of Taur and Ning ) Lundstrom EE-612 F06 28

Outline 1) Review 2) Speed 3) Power 4) Circuit performance 5) CMOS circuit metrics Lundstrom EE-612 F06 29

key metrics E S = 1 1) Switching energy: 2 2 CV DD τ S = CV DD 2) Switching delay: I D (ON) D = α f CV DD 2 P 3) Dynamic power: C 2 V DD 3 E S τ = 1 4) Energy-delay product: 2 I D (on) Lundstrom EE-612 F06 30

the energy-delay metric Energy-delay product: C 2 V DD 3 3 E S τ = 1 V DD I D (on) ~ ( ) V DD − V T 2 Minimum energy-delay product: ( ) ∂ τ E = ⇒ = S opt 0 1.5 V V ∂ DD T V DD Lundstrom EE-612 F06 31

device metrics for 65 nm technology node 2 ≈ 21 aJ E S = 1 2 CV DD 1) Switching energy: τ S = CV DD I D (ON) = 0.64 ps 2) Switching delay: D = α f CV DD 2 P 3) Dynamic power: C 2 V DD 3 E S τ = 1 I D (on) = 1.4 × 10 − 29 J-s 4) Energy-delay product: 2 Lundstrom EE-612 F06 32

circuit performance (high-speed logic) Typical power dissipation of a logic chip: 100 W ≈ 20 W Dissipation of logic core: f α = 10 7 × C S × 1 2 2 ( ) × 10 − 1 C S V DD core = N core × 4 × 10 9 P 2 2 C S ≈ 10 fF/node 2 E S ≈ C S V DD = 6,000 aJ Average switching energy: 2 E S τ ≈ 1.5 × 10 − 24 J-s Energy-delay product: Lundstrom EE-612 F06 33

from device to circuit device circuit increase delay: 0.64 ps 250 ps ~ 400 × switching ~300 × 21 aJ 6000 aJ energy: energy- ~ 10 − 29 J-s ~ 10 − 24 J-s ~100,000 × delay: Lundstrom EE-612 F06 34

Outline 1) Review 2) Speed 3) Power 4) Circuit performance 5) CMOS circuit metrics Lundstrom EE-612 F06 35

conclusions / questions 1) Device metrics aren’t enough; the circuit is critical. 2) How close is CMOS to fundamental limits? Lundstrom EE-612 F06 36

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.