CMOS Inverter: Power Dissipation and Sizing CMOS Inverter Power - PowerPoint PPT Presentation

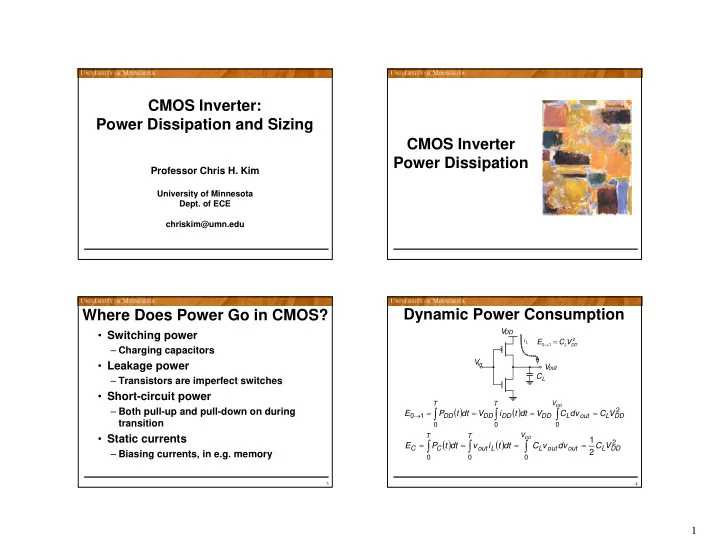

CMOS Inverter: Power Dissipation and Sizing CMOS Inverter Power Dissipation Professor Chris H. Kim University of Minnesota Dept. of ECE chriskim@umn.edu Dynamic Power Consumption Where Does Power Go in CMOS? V DD Switching power i L

CMOS Inverter: Power Dissipation and Sizing CMOS Inverter Power Dissipation Professor Chris H. Kim University of Minnesota Dept. of ECE chriskim@umn.edu Dynamic Power Consumption Where Does Power Go in CMOS? V DD • Switching power i L = 2 E C L V → 0 1 DD – Charging capacitors V • Leakage power in V out C L – Transistors are imperfect switches • Short-circuit power T T V ( ) ( ) DD ∫ ∫ ∫ – Both pull-up and pull-down on during 2 = = = = E P t dt V i t dt V C dv C V → 0 1 DD DD DD DD L out L DD transition 0 0 0 V T T • Static currents ( ) ( ) DD 1 ∫ ∫ ∫ = = = = 2 E P t dt v i t dt C v dv C V C C out L L out out L DD 2 – Biasing currents, in e.g. memory 0 0 0 3 4 1

Circuits with Reduced Swing Dynamic Power Consumption = 2 E C L V V → DD 0 1 DD V dd i L 1 = 2 E C V V dd R L DD 2 V in V dd -V Th V out 1 = 2 E C V C L C L DD 2 C L • One half of the energy from the supply is consumed in the pull-up network and one half is ( ) = − stored on C L E C V V V → 1 0 L DD DD Th • Energy from C L is dumped during the 1 → 0 transition 5 6 Transition Activity and Power Dynamic Power Consumption Power = Energy/transition • Transition rate • Energy consumed in N cycles, E N : 2 • f 0 → 1 = C L V DD E N = C L • V DD 2 • n 0 → 1 2 • f • P 0 → 1 = C L V DD n 0 → 1 – number of 0 → 1 transitions in N cycles 2 • f ⎛ ⎞ E n = C switched V DD = ⋅ = ⋅ ⋅ ⋅ ⎜ → ⎟ 2 N 0 1 P lim f lim C V f avg L DD ⎝ ⎠ → ∞ → ∞ N N N N n • Power dissipation is data dependent – α = → ⋅ lim 0 1 f → 0 1 → ∞ N depends on the switching probability N = α ⋅ ⋅ 2 ⋅ • Switched capacitance C switched = C L • P 0 → 1 P C V f → avg 0 1 L DD 7 8 2

Short Circuit Current Transistor Leakage V DD V DD • Transistors that are supposed to be off - leak I sc ∼ 0 I sc = I MAX V out V out V in V DD V in V DD C L C L x 10 − 4 I Leak 2.5 C L = 20 fF 2 V DD Large load 0V Small load 0V V DD 1.5 C L = 100 fF I sc (A) 1 C L = 500 fF 0.5 I Leak 0 − 0.5 0 20 40 60 time (s) Input at V DD Input at 0 • Short circuit current is usually well controlled 9 10 Diode Leakage GATE p + p + N Sizing of an Reverse Leakage Current Inverter Chain + - V dd I DL = J S × A JS = 10-100 pA/mm2 at 25 deg C for 0.25um CMOS JS doubles for every 9 deg C! Much smaller than transistor leakage in deep submicron 11 3

Inverter Chain Inverter Delay • Minimum length devices, L =0.25um • Assume that for W P = 2 W N = 2 W 2 W In Out • same pull-up and pull-down currents • approx. equal resistances R N = R P C L • approx. equal rise t pLH and fall t pHL delays W • Analyze as an RC network − − 1 1 ⎛ ⎞ ⎛ ⎞ W W = ⎜ ⎟ ≈ ⎜ ⎟ = = P N R R R R R ⎜ ⎟ ⎜ ⎟ If C L is given: P unit unit N W ⎝ W ⎠ ⎝ W ⎠ unit unit - How many stages are needed to minimize the t pHL = (ln 2) R N C L delay? Delay ( D ): t pLH = (ln 2) R P C L - How to size the inverters? W = C 3 C Load for the next stage: gin unit May need some additional constraints. W unit 13 14 Inverter with Load Inverter with Load Delay C P = 2 C unit Delay R W 2 W W C L C int C L R W Load ( C L ) Load t p = k R W C L C N = C unit k is a constant, equal to 0.69 for step input Delay = kR W ( C int + C L ) = kR W C int + kR W C L = kR W C int (1+ C L Assumptions: no load -> zero delay / C int ) W unit = 1 = Delay (Intrinsic) + Delay (Load) 15 16 4

Delay Formula Apply to Inverter Chain ( ) In Out + ~ Delay R C C W int L C L 1 2 N ( ) ( ) = + = + γ t kR C 1 C / C t 1 f / p W int L int p 0 t p = t p 1 + t p 2 + …+ t pN ⎛ ⎞ C γ = ⎜ ⎟ + C int = γ C gin with γ ≈ 1 + 1 gin , j 1 t ~ R C 1 ⎜ ⎟ pj unit unit ⎝ C ⎠ f = C L /C gin - effective fanout gin , j ⎛ ⎞ N N C R = R unit /W ; C int =WC unit ∑ ∑ ⎜ ⎟ + = = + = gin , j 1 t t t 1 , C C ⎜ ⎟ + p p , j p 0 gin , N 1 L t p 0 = 0.69 R unit C unit C ⎝ ⎠ = = j 1 i 1 gin , j 17 18 Optimal Tapering for Given N Optimum Delay and Number of Stages Delay equation has N - 1 unknowns, C gin,2 – C gin,N When each stage is sized by f and has same eff. fanout f : = = N Minimize the delay, find N - 1 partial derivatives f F C / C L gin , 1 Effective fanout of each stage: Result: C gin,j +1 / C gin,j = C gin,j / C gin,j -1 N F f = Size of each stage is the geometric mean of two neighbors = C C C − + gin , j gin , j 1 gin , j 1 Minimum path delay ( ) - each stage has the same effective fanout ( C out / C in ) = + N t Nt 1 F - each stage has the same delay p p 0 19 20 5

Example Optimum Number of Stages For a given load, C L and given input capacitance C in Find optimal number of stages, N, and optimal sizing, f In Out ln F = ⋅ = = N C F C f C with N L in in ln C L = 8 C 1 f f 2 1 f C 1 ⎛ ⎞ ( ) γ t ln F f ⎜ ⎟ = γ + = + 1 / N p 0 t Nt F / 1 ⎜ ⎟ γ p p 0 ⎝ ⎠ ln f ln f C L / C 1 has to be evenly distributed across N = 3 stages: ∂ − − γ t t ln F ln f 1 f = ⋅ = p p 0 0 ∂ γ = = 3 2 f ln f f 8 2 ( ) = + γ For γ = 0, f = e, N = ln F f exp 1 f 21 22 Optimum Effective Fanout f Impact of Loading on tp With self-loading γ =1 Optimum f for given process defined by γ ( ) 7 = + γ f exp 1 f 6 5 Normalized delay f opt = 3.6 5 for γ =1 4.5 4 4 f opt 3 3.5 2 1 3 0 2.5 1 1.5 2 2.5 3 3.5 4 4.5 5 0 0.5 1 1.5 2 2.5 3 γ f 23 24 6

Buffer Design Normalized Delay Function of F N f t p ( ) = + γ N 1 t Nt 1 F / 64 1 64 65 p p 0 ( ) = + γ = N t Nt 1 F , with 1 p p 0 2 8 18 1 8 64 3 4 15 1 4 16 64 1 4 2.8 15.3 64 8 22.6 2.8 25 26 7

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.