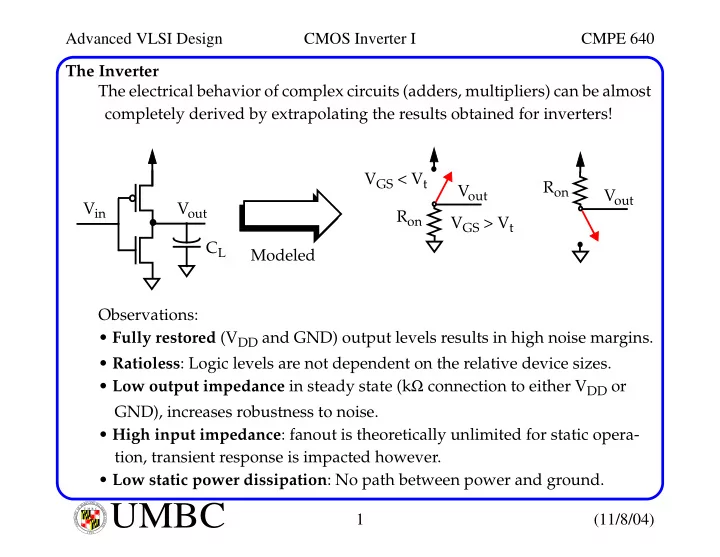

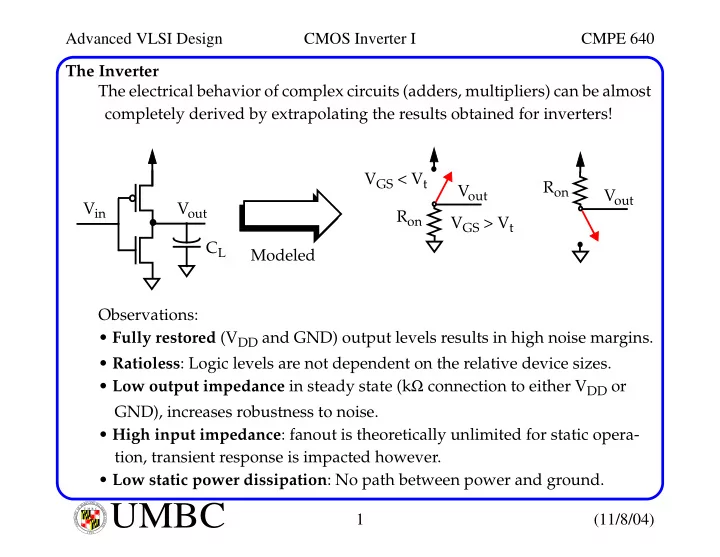

Advanced VLSI Design CMOS Inverter I CMPE 640 The Inverter The electrical behavior of complex circuits (adders, multipliers) can be almost completely derived by extrapolating the results obtained for inverters! V GS < V t R on V out V out V in V out R on V GS > V t C L Modeled Observations: • Fully restored (V DD and GND) output levels results in high noise margins. • Ratioless : Logic levels are not dependent on the relative device sizes. • Low output impedance in steady state (k Ω connection to either V DD or GND), increases robustness to noise. • High input impedance : fanout is theoretically unlimited for static opera- tion, transient response is impacted however. • Low static power dissipation : No path between power and ground. L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 1 (11/8/04) I E S R C E O V U I N N U T Y 1 6 9 6

Advanced VLSI Design CMOS Inverter I CMPE 640 The Inverter DC current characteristics 0V 2.5V Load-line plot Here, PMOS curves have been 0.5V 2.0V mirrored around x and shifted. I DS (mA) 1.5V 1V The current of the NMOS and PMOS device MUST be equal. 1V 1.5V All points are located at either the 2.0V 0.5V 2.5V 0V high or low output levels. NMOS sat V DD NMOS off PMOS lin Inverter exhibits a very PMOS lin narrow transition zone. V out NMOS sat PMOS sat 1.25V NMOS lin PMOS sat NMOS lin PMOS off 0V V in V DD 1.25V L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 2 (11/8/04) I E S R C E O V U I N N U T Y 1 6 9 6

Advanced VLSI Design CMOS Inverter I CMPE 640 Inverter Models It is possible to approximate the transient response to an RC model. The response is dominated by the output capacitance of the gate, C L . R p V out V out R n C L C L Load capacitance, C L , is due to diffusion, routing and downstream gates. The propagation delay assuming an instantaneous input transition is R p C L . This indicates a fast gate is built by keeping either or both of R p and C L small. R p is reduced by increasing the W/L ratio. Bear in mind that, in reality, R n/p is a nonlinear function of the voltage across the transistor. L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 3 (11/8/04) I E S R C E O V U I N N U T Y 1 6 9 6

Advanced VLSI Design CMOS Inverter I CMPE 640 Switching Threshold Previously, we defined V M as the inverter threshold voltage but did not derive an analytical expression for it. The same is true for V IH and V IL , and consequently the noise margins (see text for this analysis). V M is defined as the intersection of the line V in = V out and the inverter VTC. VTC V in =V out V out V M (gate threshold voltage) V in In this region, both the NMOS and PMOS transistors are in saturation since V DS = V GS . L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 4 (11/8/04) I E S R C E O V U I N N U T Y 1 6 9 6

Advanced VLSI Design CMOS Inverter I CMPE 640 Switching Threshold Therefore, the value of V M can be obtained by equating the NMOS and PMOS currents (assuming devices are velocity saturated). V DSATn V DSATp 2 k n V DSATn V M V Tn k p V DSATp V M V DD V Tp – – - - - - - - - - - - - - - - - - - - - - - + – – – - - - - - - - - - - - - - - - - - - - - - 2 2 Solving for V M : V DSATn V DSATp Further simplified: r V Tn r V DD V Tp – - - - - - - - - - - - - - - - - - - - - - + + + - - - - - - - - - - - - - - - - - - - - - 2 2 rV DD V M = - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - r ≅ V M 1 + - - - - - - - - - - - - - - - r 1 + υ satp W p k p V DSATp with r = - - - - - - - - - - - - - - - - - - - - - - - - - - - = - - - - - - - - - - - - - - - - - - - - - - υ satn W n k n V DSATn V M is set by the ratio r , and r compares the relative driving strengths of the PMOS and NMOS transistors. It is desirable to have r = 1, i.e., V M situated in the middle of the available voltage swing (V DD /2) to provide comparable low and high noise margins. L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 5 (11/8/04) I E S R C E O V U I N N U T Y 1 6 9 6

Advanced VLSI Design CMOS Inverter I CMPE 640 Switching Threshold The required ratio can be determined for any value of V M using: V DSATn V DSATn k ′ n V M V Tn ( ⁄ ) p – – - - - - - - - - - - - - - - - - - - - - - W L 2 - - - - - - - - - - - - - - - - - - - - - = - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - ( ⁄ ) n W L V DSATp V DSATp k ′ p V DD V M V Tp – + + - - - - - - - - - - - - - - - - - - - - - 2 Using a generic 0.25 µ m CMOS process, this means making the PMOS 3.5 times wider than the NMOS. V M plotted as a function of the PMOS-to-NMOS ratio. 2.0 1.6 V M (V) 1.2 x scale gives the log of the ratio of PMOS and NMOS 0.8 widths as the difference. 0.1 1.0 10.0 W p -W n L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 6 (11/8/04) I E S R C E O V U I N N U T Y 1 6 9 6

Advanced VLSI Design CMOS Inverter I CMPE 640 Switching Threshold Observations from plot: • V M is relatively insensitive to variations in device ratio. Small variations in the ratio (3.0 -> 2.5) do not disturb the VTC much. Industry sets the ratio of PMOS width to NMOS width to values smaller than that needed for an exact symmetry. For example, setting the ratio to 3, 2.5 and 2 yields switching thresholds of 1.22 V, 1.18 V and 1.13 V, respectively. • Increasing the width of the PMOS or the NMOS moves V M toward V DD or GND, respectively. This feature may be desirable in some applications, e.g., when the input signal is noisy (see text). Bear in mind that when the ratio of V DD to V T is relatively small , e.g. 2.5/ 0.4 = 6), moving V M a lot is difficult and requires very large differences in the width ratios. L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 7 (11/8/04) I E S R C E O V U I N N U T Y 1 6 9 6

Advanced VLSI Design CMOS Inverter I CMPE 640 Inverter Threshold Robustness under process variations: V DD Weak NMOS Strong PMOS 1.25V Strong NMOS Nominal Weak PMOS V out V in V DD 1.25V Process variations will cause only small shifts in the transfer curve. The functionality of the gate is not effected however, and this feature has con- tributed in a big way to the popularity of the static CMOS gate. L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 8 (11/8/04) I E S R C E O V U I N N U T Y 1 6 9 6

Advanced VLSI Design CMOS Inverter I CMPE 640 Dynamic Behavior Propagation delay is determined by the time it takes to charge/discharge the load cap, C L , so it’s worth looking closely at C L before developing a delay model. Simple propagation delay models lumps all capacitances into C L . V out M 2 M 4 C gd12 All cap influencing C g4 C db2 V in V out2 transient response of node V out . C g3 C db1 C w M 3 M 1 In this analysis, assume V in is driven by an ideal voltage source with fixed rise/fall times. L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 9 (11/8/04) I E S R C E O V U I N N U T Y 1 6 9 6

Advanced VLSI Design CMOS Inverter I CMPE 640 Dynamic Behavior Gate-drain capacitance: • C gd12 : Capacitance between the gate and drain of the first inverter. M 1 and M 2 are either in cut-off or in saturation during the first half (up to 50% point) of the output transient. It is reasonable to assume that only M1 & M2 overlap capacitances contrib- ute. Remember, gate cap is either completely between gate/bulk (cut-off) or gate/src (sat). In the lumped model, we need to replace the C gd12 with a capacitor to GND. The value of this capacitor is given as C gd = 2*C GD0 *W where C GD0 is overlap capacitance per unit width. Note it is doubled due to the Miller effect . L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 10 (11/8/04) I E S R C E O V U I N N U T Y 1 6 9 6

Recommend

More recommend