5. Introduction to CMOS Digital Gates Lecture notes: Sec. 4 Sedra - PowerPoint PPT Presentation

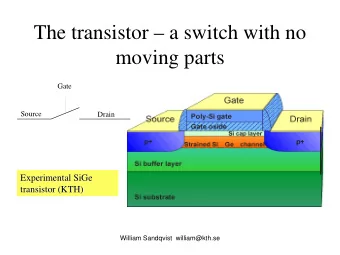

5. Introduction to CMOS Digital Gates Lecture notes: Sec. 4 Sedra & Smith (6 th Ed): Sec. 5.1-5.3 Sedra & Smith (5 th Ed): Sec. 4.1-4.3 ECE 65, Winter2013, F. Najmabadi Complementary MOS (CMOS) is based on NMOS/PMOS pairs NMOS Inverter

5. Introduction to CMOS Digital Gates Lecture notes: Sec. 4 Sedra & Smith (6 th Ed): Sec. 5.1-5.3 Sedra & Smith (5 th Ed): Sec. 4.1-4.3 ECE 65, Winter2013, F. Najmabadi

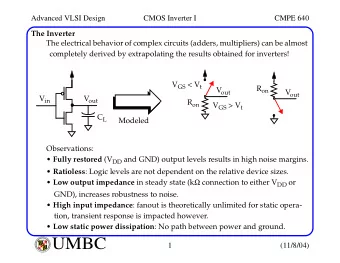

Complementary MOS (CMOS) is based on NMOS/PMOS pairs NMOS Inverter CMOS Inverter Replace R D with a PMOS “Effective” R D seen by Q1 is controlled by v i : o “ Infinite” R D when Q1 is ON o “Very small” R D when Q1 is OFF Maximum signal swing: Low State: 0, High State: V DD o Independent of MOS device parameters! o Wide noise margin. Zero “static” power dissipation ( i D = 0 in each state). Higher speed compare to a “RTL-type” NMOS inverter F. Najmabadi, ECE65, Winter 2013, Intro to CMOS (2/11)

Analysis of CMOS Inverter (1) − = GS1 KVL : v v GS 1 i − = + → = − GS2 KVL : V v v v V v DD SG 2 i SG 2 DD i − = + DS1 & 2 KVL : V v v DD SD 2 DS 1 = i i D 1 D 2 = = − v v V v o DS 1 DD SD 2 Case 1: v i = 0 = = = = < < → → → → = = v v v v 0 0 V V Q1 Q1 OFF OFF i i 0 0 GS GS 1 1 i i tn tn D D 1 1 ↓ ↓ KCL = = − − = = > > → → = v v V V v v V V |V |V | | Q2 Q2 ON ON i 0 SG SG 2 2 DD DD i i DD DD tp tp D 2 ? F. Najmabadi, ECE65, Winter 2013, Intro to CMOS (3/11)

A MOS is ON and i D = 0 only if MOS is in triode and v DS = 0 MOS ON: V OV > 0 W = µ = → = 2 MOS in saturation: incorrect! i 0 . 5 C V 0 V 0 D n ox OV OV L [ ] W = µ − = → = 2 MOS in triode: i 0 . 5 C 2 V v v 0 v 0 D n ox OV DS DS DS L When is i D = 0 ? MOS is OFF ( V OV < 0) o No channel is formed, no i D can flow MOS is ON ( V OV > 0) o A channel is formed, and i D can flow but i D = 0 because no voltage is applied to drive i D ( v DS = 0) ! F. Najmabadi, ECE65, Winter 2013, Intro to CMOS (4/11)

Analysis of CMOS Inverter (2) − = GS1 KVL : v v GS 1 i − = + → = − GS2 KVL : V v v v V v DD SG 2 i SG 2 DD i − = + DS1 & 2 KVL : V v v DD SD 2 DS 1 = i i D 1 D 2 = = − v v V v o DS 1 DD SD 2 Case 1: v i = 0 = = = = < < → → → → = = = v v v v 0 0 V V Q1 Q1 OFF OFF i i 0 0 v V GS GS 1 1 i i tn tn D D 1 1 DS 1 DD ↓ ↓ ↑ = = − − = = > > → → = = → = v v V V v v V V | | V V | | Q2 Q2 ON ON i i 0 0 Q2 in Triode & v 0 SG SG 2 2 DD DD i i DD DD tp tp D D 2 2 SD 2 For v i = V DD , v o = v DS1 = 0 ( i D1 = 0, i D2 = 0 ) Gate remains in this state as long as v i > V DD − | V tp | (Q2 OFF) F. Najmabadi, ECE65, Winter 2013, Intro to CMOS (5/11)

Analysis of CMOS Inverter (3) − = GS1 KVL : v v GS 1 i − = + → = − GS2 KVL : V v v v V v DD SG 2 i SG 2 DD i − = + DS1 & 2 KVL : V v v DD SD 2 DS 1 = i i D 1 D 2 = = − v v V v o DS 1 DD SD 2 Case 2: v i = V DD = = = = = = > > > → → → = = → = v v v v v v V V V V V V Q1 Q1 Q1 ON ON ON i i 0 0 Q1 in Triode & v 0 GS GS GS 1 1 1 i i i DD DD DD tn tn tn D D 1 1 DS 1 ↑ ↑ ↑ ↓ = = = − − − = = = < < < → → → → → → = = = = v v v V V V v v v 0 0 0 | | | V V V | | | Q2 Q2 Q2 OFF OFF OFF i i i 0 0 0 v V SG SG SG 2 2 2 DD DD DD i i i tp tp tp D D D 2 2 2 SD 2 DD For v i = V DD , v o = v DS1 = 0 ( i D1 = 0, i D2 = 0 ) Gate remains in this state as long as v i > V DD − | V tp | (Q2 OFF) F. Najmabadi, ECE65, Winter 2013, Intro to CMOS (6/11)

Transfer function of a CMOS inverter Transfer function is “symmetric” for matched transistors: V tn =| V tp | & µ n ( W/L ) n = µ p ( W/L ) p During transition from one state to another, i D > 0 F. Najmabadi, ECE65, Winter 2013, Intro to CMOS (7/11)

CMOS NAND Gate Truth Table v 1 = 0 v 2 = 0: v o = V DD v 1 = 0 v 2 = V DD : v o = V DD v 1 = V DD v 2 = 0 : v o = V DD v 1 = V DD v 2 = V DD : v o = 0 F. Najmabadi, ECE65, Winter 2013, Intro to CMOS (8/11)

Analysis of CMOS NAND Gate (1) v GS = v GS4-KVL GS1-KVL: 1 1 GS3-KVL = + v v v GS2-KVL: 2 GS 2 DS 1 → = − v v v GS 2 2 DS 1 = + V v v GS3-KVL: DD SG 3 1 → = − v V v SG 3 DD 1 = + V v v GS4-KVL: DD SG 4 2 → = − GS2-KVL v V v SG 4 DD 2 = + + V v v v DS-KVL: DD SD 4 DS 2 DS 1 = v v SD 3 SD 4 = + = = + v v v i i i i KCL: o DS 1 DS 2 D 1 D 2 D 3 D 4 = − = − v V v V v o DD SD 4 DD SD 3 F. Najmabadi, ECE65, Winter 2013, Intro to CMOS (9/11)

Analysis of CMOS NAND Gate (2) = − = − = + v V v V v v v o DD SD 4 DD SD 3 DS 1 DS 2 = = + i i i i D 1 D 2 D 3 D 4 Case 1: v 1 = 0 & v 2 = 0 = = = = = = < < < → → → → → → = = = v v v v v v 0 0 0 V V V Q1 Q1 Q1 OFF OFF OFF i i i 0 0 0 GS GS GS 1 1 1 1 1 1 tn tn tn D D D 1 1 1 = = = − − − = = = − − − → → → = = v v v v v v v v v v v v Q2 Q2 Q2 ? ? ? i i 0 0 GS GS GS 2 2 2 2 2 2 DS DS DS 1 1 1 DS DS DS 1 1 1 D D 2 2 = = = − − − = = = > > > → → → = = → = v v v V V V v v v V V V | | | V V V | | | Q3 Q3 Q3 ON ON ON i i 0 0 Q3 in Triode & v 0 SG SG SG 3 3 3 DD DD DD 1 1 1 DD DD DD tp tp tp D D 3 3 SD 3 = = = − − − = = = > > > → → → = = → = v v v V V V v v v V V V | | | V V V | | | Q4 Q4 Q4 ON ON ON i i 0 0 Q4 in Triode & v 0 SG SG SG 4 4 4 DD DD DD 2 2 2 DD DD DD tp tp tp D D 4 4 SD 4 = − = v V v V o DD SD 4 DD For v 1 = 0 & v 2 = 0, v o = V DD ( i D1 = i D2 = i D3 = i D4 = 0) Note: Since v DS1 ≥ 0, we can say v GS2 = v DS1 < V tn and Q2 is OFF! F. Najmabadi, ECE65, Winter 2013, Intro to CMOS (10/11)

Analysis of CMOS NAND Gate (3) = − = − = + v V v V v v v o DD SD 4 DD SD 3 DS 1 DS 2 = = + i i i i D 1 D 2 D 3 D 4 Case 2: v 1 = V DD & v 2 = 0 = = = = = = > > > → → → = = → = v v v v v v V V V V V V Q1 Q1 Q1 ON ON ON i i 0 0 Q1 in Triode & v 0 GS GS GS 1 1 1 1 1 1 DD DD DD tn tn tn D D 1 1 DS 1 = = = − − − = = = − − − < < < → → → → → → = = = v v v v v v v v v v v v V V V Q2 Q2 Q2 OFF OFF OFF i i i 0 0 0 GS GS GS 2 2 2 2 2 2 DS DS DS 1 1 1 DS DS DS 1 1 1 tn tn tn D D D 2 2 2 = = = − − − = = = < < < → → → → → → = = = v v v V V V v v v 0 0 0 | | | V V V | | | Q3 Q3 Q3 OFF OFF OFF i i i 0 0 0 SG SG SG 3 3 3 DD DD DD 1 1 1 tp tp tp D D D 3 3 3 = = = − − − = = = > > > → → → = = → = v v v V V V v v v V V V | | | V V V | | | Q4 Q4 Q4 ON ON ON i i 0 0 Q4 in Triode & v 0 SG SG SG 4 4 4 DD DD DD 2 2 2 DD DD DD tp tp tp D D 4 4 SD 4 = − = v V v V o DD SD 4 DD For v 1 = V DD & v 2 = 0, v o = V DD ( i D1 = i D2 = i D3 = i D4 = 0) Exercise: Complete the analysis of the truth table of this NAND gate F. Najmabadi, ECE65, Winter 2013, Intro to CMOS (11/11)

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.