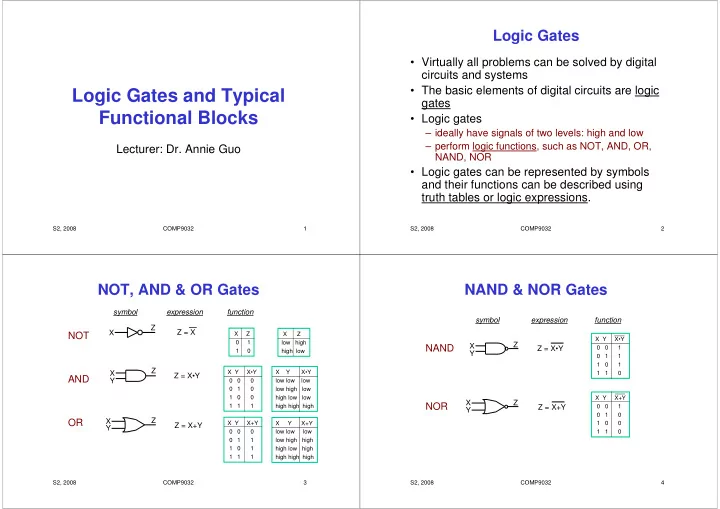

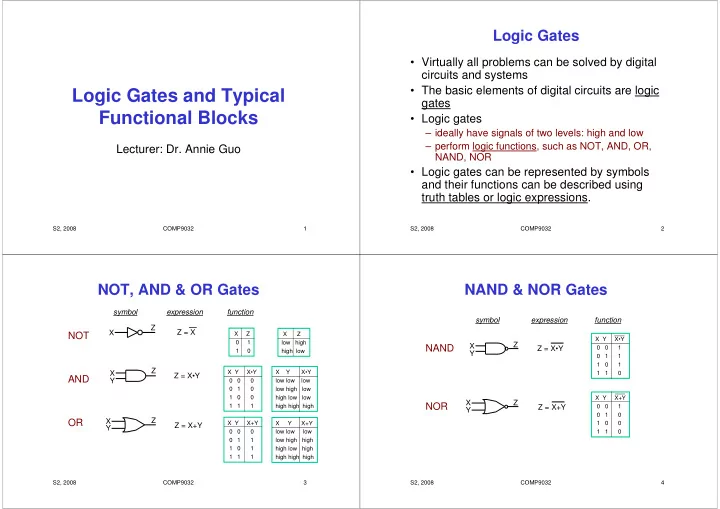

Logic Gates • Virtually all problems can be solved by digital circuits and systems • The basic elements of digital circuits are logic Logic Gates and Typical gates Functional Blocks • Logic gates – ideally have signals of two levels: high and low – perform logic functions, such as NOT, AND, OR, Lecturer: Dr. Annie Guo NAND, NOR • Logic gates can be represented by symbols and their functions can be described using truth tables or logic expressions. S2, 2008 COMP9032 1 S2, 2008 COMP9032 2 NOT, AND & OR Gates NAND & NOR Gates symbol expression function symbol expression function Z X Z = X NOT X Z X Z X Y X•Y 0 1 low high Z X NAND Z = X•Y 0 0 1 1 0 high low Y 0 1 1 1 0 1 Z X X Y X•Y X Y X•Y 1 1 0 Z = X•Y AND Y 0 0 0 low low low 0 1 0 low high low 1 0 0 high low low X Y X+Y X Z NOR 1 1 1 high high high Z = X+Y 0 0 1 Y 0 1 0 X Z OR X Y X+Y X Y X+Y 1 0 0 Z = X+Y Y 0 0 0 low low low 1 1 0 0 1 1 low high high 1 0 1 high low high 1 1 1 high high high S2, 2008 COMP9032 3 S2, 2008 COMP9032 4

XOR & XNOR Gates Functional Blocks symbol expression function • With basic logic gates we can build up different functional blocks such as Z X XOR Z = X ⊕ Y X Y X ⊕ Y Y – Adders 0 0 0 0 1 1 – Multiplexers 1 0 1 1 1 0 – Decoders – Latches XNOR X Z X Y X ⊕ Y Z = X ⊕ Y – Registers Y 0 0 1 0 1 0 – Counters 1 0 0 1 1 1 S2, 2008 COMP9032 5 S2, 2008 COMP9032 6 Adders (1/3) Adders (2/3) • One bit adder • One bit adder with carry – Truth table A B S C – Called Full Adder – Logic function 0 0 0 0 – Symbol A 0 1 1 0 S Full B 1 0 1 0 Cout Sum: S = A ⊕ ⊕ B Adder ⊕ ⊕ Cin 1 1 0 1 Carry: C = A•B – Function A B C in S C out – Digital circuit A S • Adding three 1-bit numbers 0 0 0 0 0 B 0 0 1 1 0 C 0 1 0 1 0 0 1 1 0 1 – Symbol 1 0 0 1 0 A 1-bit S 1 0 1 0 1 B adder C 1 1 0 0 1 1 1 1 1 1 S2, 2008 COMP9032 7 S2, 2008 COMP9032 8

Adders (3/3) Multiplexers • n-bit adder • Function: – Symbol – A multiplexer selects one input among multiple inputs and passes it to output. n n A n-bit S • The selection is controlled by control signal S n-1 ~S 0 B adder C • The symbol: n – Function • Adding two n-bit numbers D0 – The result is n-bit sum and 1-bit carry m:1 D1 m:1 OR Y mux mux Dm-1 S n -1 S 0 … S2, 2008 COMP9032 9 S2, 2008 COMP9032 10 Example Decoders • 4:1 multiplexer • Function: – A decoder converses an n-bit input code to an m- D0 bit output code D1 4:1 • n ≤ m ≤ 2 n Y mux D2 • each valid input code word produces a unique output D3 S 1 S 0 code – Typical n-to-2 n decoder • One line of outputs represents a specific input • Function: combination When S 1 S 0 = 00, Y=D0 B0 A0 B1 When S 1 S 0 = 01, Y=D1 A1 n-to-2 n – The symbol: When S 1 S 0 = 10, Y=D2 decoder When S 1 S 0 = 11, Y=D3 An-1 B2 n -1 S2, 2008 COMP9032 11 S2, 2008 COMP9032 12

Example Multi-operation Unit • 3-to-8 register file address decoder • Perform following1-bit logic operations: – AND, OR, XOR, NOT B0 B1 A0 3-to-8 A1 decoder A2 B7 Address Output • Function: A2 A1 A0 B0 B1 B2 B3 B4 B5 B6 B7 0 0 0 1 0 0 0 0 0 0 0 0 0 1 0 1 0 0 0 0 0 0 0 1 0 0 0 1 0 0 0 0 0 0 1 1 0 0 0 1 0 0 0 0 1 0 0 0 0 0 0 1 0 0 0 1 0 1 0 0 0 0 0 1 0 0 1 1 0 0 0 0 0 0 0 1 0 1 1 1 0 0 0 0 0 0 0 1 Constructed with functional components S2, 2008 COMP9032 13 S2, 2008 COMP9032 14 ALU Example • Perform arithmetic and logic operations – such as addition, subtraction, logic AND, logic OR Operation selection Operation S2 S1 S0 • Symbol: – A, B are operands, S selects one of operations 0 0 0 Addition that can be performed by ALU 0 0 1 Subtraction 0 1 0 AND 0 1 1 OR 1 0 0 XOR 1 0 1 NOT A 1 1 0 Increment B OR ALU R ALU 1 1 1 Transfer S S2, 2008 COMP9032 15 S2, 2008 COMP9032 16

Latches and Flip Flops (1/3) Latches and Flip Flops (2/3) • A latch can store one bit information. • Clocked latch uses clock to control the latch operation • Can be constructed in many ways. – When Clk=1, • 2-NAND-gate latch • S=1, set the latch • R=0, reset the latch • R=1, reset the latch • S=0, set latch • S=R=0, the data is retained • S = R = 1, the data is retained – When Clk=0, S • Data is retained Q S Q Clk Q R Q R S2, 2008 COMP9032 17 S2, 2008 COMP9032 18 Latches and Flip Flops (3/3) Registers (1/3) • Flip Flops use clock edges to trigger the data- • A register is a collection of latches/FFs store operation. – storing a vector of bit values – A very commonly used Flip Flop is D FF • Symbol • On the rise edge of clock, the input data D is locked into the D flip flop PC D Q(n+1) D Q clk Q 0 0 15 8 7 0 1 1 R(H) R(L) – Timing diagram cp D Q S2, 2008 COMP9032 19 S2, 2008 COMP9032 20

Registers (2/3) Registers (3/3) • 4-bit Parallel In Parallel Out (PIPO) registers. • 4-bit Serial In Parallel Out (SIPO) registers. I 3 Q 3 D Q On the clock edge, the output of each flip- flop is passed to the next flip-flop in the The 4-bit input I 3 I 2 I 1 I 0 is chain. The input signal is fed serially (one “loaded” (copied to the I 2 Q 2 D Q bit at a time) into the first flip-flop. The flip- output Q 3 Q 2 Q 1 Q 0 of the D flop outputs are available in parallel. FFs ) on the rising clock edge, and that output is I 1 Q 1 Q 0 Q 1 Q 2 Q 3 D Q held until the next clock edge. Input D Q D Q D Q D Q I 0 Q 0 D Q Clk CP S2, 2008 COMP9032 21 S2, 2008 COMP9032 22 Counters (1/2) Counters (2/2) • A counter increases/decrease its value every • 4-bit counter clock cycle. • Symbol 0 D3 Q3 The counter has 0 D2 Q2 • a synchronous load 0 D1 Q1 n-bit • an asynchronous clear 0 D0 Q0 counter The counter counts through 0, Clock CP 1, 2, …, 15, 0 LOAD Reset CLEAR S2, 2008 COMP9032 23 S2, 2008 COMP9032 24

Recommend

More recommend