Chapter 5 Fundamental parameters The CMOS Inverter for digital - PowerPoint PPT Presentation

Digital IC-Design Digital IC-Design Chapter 5 Fundamental parameters The CMOS Inverter for digital gates Goal With This Chapter Robustness Analyze Fundamental Parameters Noise - unwanted variations of voltages and A general

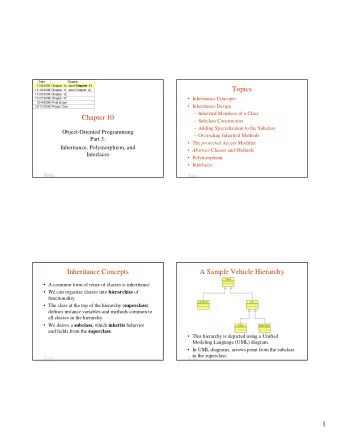

Digital IC-Design Digital IC-Design Chapter 5 Fundamental parameters The CMOS Inverter for digital gates Goal With This Chapter Robustness Analyze Fundamental Parameters Noise - “unwanted variations of voltages and A general understanding of the inverter currents in logical nodes” g behavior is useful to understand more complex behavior is useful to understand more complex functions Classical noise such as thermal and flicker noise are not critical in digital design Outline Noise Noise sources in digital circuits are Reliability Capacitive coupling Capacitive coupling Performance P f Inductive coupling Power Consumption Power and ground noise 1

Capacitive and Inductive Coupling Power and Ground Noise A voltage or a current A big V problem on change may influence V DD V DD large large th i the signal on a parallel l ll l C Coupling C R Wire V synchronously V DD wire, especially when: clocked chips I Switch Long wires V On chip Sub micron tech. decoupling I Many metal layers capacitors helps p p Mutual Mutual ( ≈ 1/10 of the Inductance switched C) Conclusion: The world is I not digital. We need to know the limitations Definitions DC Operation Voltage Transfer Characteristic (VTC) V IN V OUT 5 V V OH DC Operation Switching Threshold 4 Noise Margins V M when V IN = V OUT V OUT 3 V out = V IN Fan OUT - Fan IN Balanced if V M = V DD /2 V M 2 Logical “1” at V OH 1 Logical “0” at V OL V OL 1 2 3 4 5 V IN 2

Analog versus Digital Signals Analog versus Digital Signals Nominal Accepteble V OUT V OH , V OL = nominal Output Levels Input Levels 5 The noise margins The noise margins V OH V OH output voltage t t lt V OH are defined as the 4 NM H difference V IH between V OH / V OL 3 Slope = -1 V IH , V IL = acceptable and V IH / V IL Undefined input voltage 2 Region NM L = V IL NM = V - V O V OL 1 V IL NM H = V OH - V IH V OL NM L V OL V IN 1 2 3 4 V IL V IH The Ideal Gate Fan-In and Fan-Out V OUT Fan-in = M Fan-out = N R in = ∞ R = ∞ R out =0 Noise Margin= V DD /2 Gain = ∞ Fan-in = The Fan-out = The number of number of inputs to the gates that loads gate the gate V IN 3

Dynamic Definitions A Real Gate NM L = V IL - V OL = 0.75 - 0.50 = 0.25V Propagation delay Propagation delay 5 NM H = V OH - V IH = 3.50 - 2.25 = 1.25V Rise and fall time 4 V M = 1.75V V OH Power consumption V OUT V DD V IL 3 V M 2 V IH 1 V OL GND 1 2 3 4 5 V IN Delay Definitions Ring Oscillator – minimum t p V 1 V 2 V 3 V 4 V 5 V IN Odd # of Odd # of inverters 50% + V 1 t t “De-facto = pHL pLH t pHL t pLH t t V 2 Standard” for p 2 performance V OUT V 3 90% 50% V 2 Fan-out = 1 10% V 5 t f t r t t 2 N t p 4

Ring Oscillator Power Dissipation Two measures are important Do t p = 100ps mean 10 GHz chip? Peak power (Sets wire dimensions) Peak power (Sets wire dimensions) Good Custom Design ≈ 1/10 Synthesized design ≈ 1/50 - 1/100 = × P V i peak DD DD max Why? V 1 V 2 V 3 V 4 V 5 Average power (Battery and cooling) Low load Low load Short Wires T V ∫ Fan-out = 1 = DD P i ( ) t dt Low complexity av DD T 0 Power-Delay Product Digital IC-Design = × PDP PDP t t P P ( ) ( ) J J p av The CMOS Inverter Energy per operation Energy per switching event 5

Inverters The CMOS Inverter V DD + Lower static power On-chip resistors are large V DD St ti Static power consumption ti consumption ti V OL ≠ 0 + V OH = V DD ; V OL = 0 Large t pLH + t pLH = t pHL If properly designed GND + Low Impedance connection to ground and V DD V DD Extra process step Extra process step Static power consumption - More fab. stages V OL ≠ 0 GND - Lower hole mobility Large t pLH GND The CMOS Inverter The CMOS Inverter V DD V DD Wider PMOS to Shared power and ground compensate for lower mobility lower mobility Cascaded Abuted cells V DD GND GND V DD V DD V DD In Out In Out In Out In Out GND GND GND GND 6

CMOS Inverter - Model CMOS Static Behavior Complementary i.e. output V DD Load characteristics Load characteristics have always a low impedance y p R R eq-p connection to GND or V DD VTC Switching threshold V OH = V DD C L V OL = 0 Noise margin g R eq-n R V M = f(R eq-n , R eq-p ) V M = V DD /2 if R eq-n = R eq-p Load Lines Inverter Load Characteristics The VTC can be determined graphically N-channel P-channel I Dn = -I Dp I D - I Dp I Dn V GS =5V V in =0V V GS =5V V in = V DD -V GSp V V V V DS I D V GS =4V V in =1V V GS =4V I D V GS =5V V GS =3V V in =2V V GS =3V V GS =-3V V DS V DS V GS =4V V out = V DD -V DSp V GS =-3V V GS =-4V out DD DSp GS V GS =3V V GS =-4V V in = V out = V GS =-5V V DD -V GSp V DD -V DSp V GS =-5V V DS 7

Inverter Load Characteristics Region: Linear - Saturation I V in =0V V in =5V I 5 V in =0V V in =5V N sat N sat N off N off in in V V OUT V in =1V V in =4V P lin P lin 4 V in =2V V in =3V V in =1V V in =4V V M 3 N sat V in =3V V in =2V P sat V out 2 V in =2V V in =3V V M 1 N lin N lin V in =3V V in =2V P sat P off V out 1 2 3 4 V IN 5 CMOS Inverter VTC Switching Threshold Long Channel Transistors VTC graphically Both transistors are saturated extracted from the 5 load lines l d li V OUT k V OH = V DD k − = − − − − ⇒ 2 p 2 n ( V V ) ( ( V V V ) ) 4 M Tn M DD Tp 2 2 High noise margin k 3 NM H = V OH -V IH ≈ 5-2.9 = 2.1V − = − − + + ⇒ p V V ( V V V ) V M = V DD /2 M Tn M DD Tp NM L = V IL -V OL ≈ 2.1-0 = 2.1V k n 2 + × = + × + ⇒ V V r V V V V r ( ( V V V V ) ) M M Tn DD Tp 1 + + − V r V ( V ) k V OL = 0 ⇒ = = Tn DD Tp p V with r + M 1 r k n 1 2 3 4 5 V IN 8

Switching Threshold Switching Threshold Long Channel Transistors + + − r V ( V ) V k + + − r V ( V ) V k = = DD Tp Tn p (V Tn = -V Tp = 0.5 V) = = V with r DD Tp Tn p V with r + M + M 1 r k 1 r k n n 5 V M 5 5 4 Moderate deviation from V M V M 4 4 k p /k n = 1 gives only 3 small changes in V M 3 3 2 2 2 W p = 2W n common to W 2W t 1 save area, since the 1 1 change in V M is small 0.1 0.32 1 3.2 k p /k n 10 1 2 4 6 8 10 0.1 0.32 1 3.2 10 k p /k n k p /k n W p ≈ 3W n Switching Threshold: Example Simulated VTC: Short Channel Inverter with W/L = 0.6 μ / 0.35 μ Balanced 0.25 μ m inverter V Tn = 0.50, k n = 300 μ , V Tp = - 0.65, k p = -103 μ 2.5 − μ k 103 = = = 2 p r 0.59 μ V DD = 3V k 300 n 1.5 + + V out (V) r V ( V ) V = = DD Tp Tn V + + M 1 1 r r 1 − + 0.5 0.59 (3 0.65) 0.5 = 1.18 V + GND 1 0.59 0 0 0.5 1 1.5 2 2.5 V in (V) 9

VTC: Short Channel VTC: Short Channel W 0.375 L = p 0.25 p 0.25 Minimum sized 0.25 μ m transistors I D (mA) W 0.375 V IN = 2.5 L = n 0.25 0.20 0.25 I D (mA) I D (mA) n V GS 2.5 V = 2 5 0 25 0.25 I D (mA) V GS = 2.5 0.20 0.20 V IN = 1.875 0.15 V GS = 1.875 0.15 V GS = 1.875 0.10 0.10 V IN = 0 0.10 V GS = 1.25 0.05 V IN = 1.25 V GS = 1.25 V GS = 1.0 PMOS V IN = 0.625 V GS = -1.25 V GS = 0.625 V GS = -0.625 0.05 0 V GS = 1.0 V = 1 0 V V IN = 1.0 = 1 0 V IN = 1.0 V = 1 0 V GS = -1.25 V IN = 1.25 V GS = 0.625 V GS = -0.625 -0.05 0 V IN = 1.875 V IN = 0.625 V GS = -1.5 V DS (V) NMOS V GS = -2.5 V GS = -1.875 0 0.5 1.0 1.5 2.0 2.5 -0.10 -2.5 -2.0 -1.5 -1.0 -0.5 0 0.5 1.0 1.5 2.0 2.5 V OUT (V) -0.05 V GS = -1.5 V DS (V) V GS = -2.5 V GS = -1.875 Move the PMOS part to the first quadrant -0.10 -2.5 -2.0 -1.5 -1.0 -0.5 0 0.5 1.0 1.5 2.0 2.5 VTC: Short Channel - Graphically Switching Threshold: Short Channel 0.25 V out (V) I D (mA) V out (V) 2.5 V IN = 2.5 2.5 0.20 2.0 2 0 VTC 2.0 The threshold 1.5 V M is when V IN = 1.875 1.5 1.0 V IN = V OUT V M =1 V 0.10 V IN = 0 1.0 0.5 V IN = 1.25 V IN = 0.625 0.5 0 V IN = 1.0 V IN = 1.0 0.5 1.0 1.5 2.0 2.5 V IN = 1.25 V in (V) V IN = 1.875 V IN = 0.625 0 0.5 1.0 1.5 2.0 2.5 0 0.5 1.0 1.5 2.0 2.5 V in (V) V OUT (V) 10

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.