Designing Logic Gates Low Swing Signals Note: The tree is reduced - PowerPoint PPT Presentation

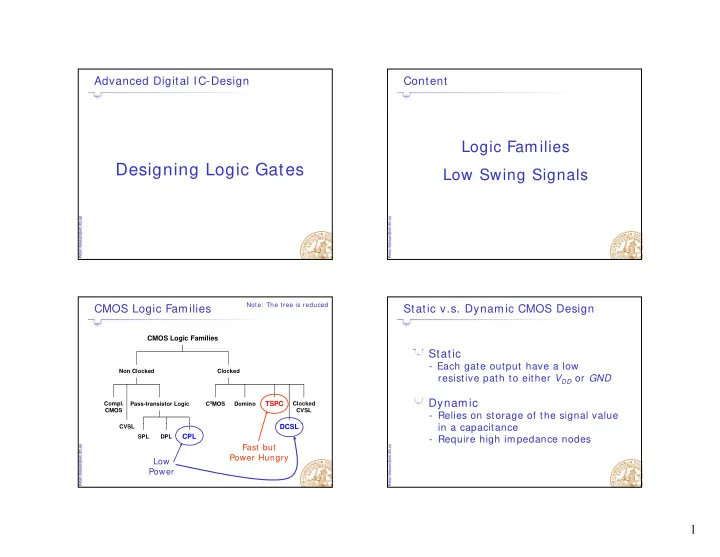

Advanced Digital IC-Design Content Logic Families Designing Logic Gates Low Swing Signals Note: The tree is reduced CMOS Logic Families Static v.s. Dynamic CMOS Design CMOS Logic Families Static - Each gate output have a low Non Clocked

Advanced Digital IC-Design Content Logic Families Designing Logic Gates Low Swing Signals Note: The tree is reduced CMOS Logic Families Static v.s. Dynamic CMOS Design CMOS Logic Families Static - Each gate output have a low Non Clocked Clocked resistive path to either V DD or GND Dynamic C 2 MOS TSPC Compl. Pass-transistor Logic Domino Clocked CMOS CVSL - Relies on storage of the signal value in a capacitance i it CVSL DCSL DCSL CPL SPL DPL - Require high impedance nodes Fast but Power Hungry Low Power 1

Static v.s. Dynamic CMOS Design Static NAND Characteristics V DD V DD V DD R l ti Relatively low power l l CLK A B V DD V DD In stand-by, only leakage f NAND f NAND A B B B Medium performance f NAND f NAND B B A Low perf. for large fan-in A A A CLK High noise margin GND GND GND GND - Low impedance to supply Static Dynamic Static current when PDN is on Ratioed Logic have Resistive Load Ratioed Logic R pull-up >> R on-n Depletion mode = V T < 0, i.e. always on V V V DD OH DD R R V DD V DD V DD − = DD DD DD eq n V V + OL DD R R R pull-up R pull-up "R pull-up " "R pull-up " − − eq n pull up f f f f Asymmetrical VTC PDN PDN PDN GND GND GND PDN PDN t pLH = 0.69 R pull-up C L t = 0 69 R C R Resistive i i NMOS NMOS P Pseudo- d load NMOS GND Static Logic: 2 n Transistors Static current when PDN is on Ratioed Logic: n + 1 Transistors 2

Pass-Transistor Logic Differential Cascode Voltage Switch Logic (DCVSL) Cross-coupled N transistors transistors Switching Switching f f Network V DD V DD No static power No static power consumption in (except leakage) pass transistors f f (except leakage) B Fully differential B A&A f f PDN PDN PDN PDN A A B&B Dual B GND GND AND NAND Two dual NMOS PDN nets Pass-transistor Logic NMOS switch net AND/ NAND 0 1 V DD B B → B V Static Static DD DD 1 0 0 B B f Current AND X f f = NAND NAND A V f The PMOS will not 0 1 A 0 A DD AND be completely V X = V DD -V T 1 0 B B closed while the 0 1 NMOS is open B B - Static power 1 1 0 0 0 0 V (V) V (V) B B B B f f B AND V X = V DD -V T consumption f f NAND NAND f 1 0 A A 1 AND 1 0 B B 3

NMOS Switch Net: Improvement Single Pass-transistor Logic – Level Restorer Careful Advantage: Full Level restorer Swing dimensioning of the g m r transistor Disadvantage: m r More Complex, Larger Capacitance B → 1 m r X A = A = B->VDD B VDD 1 1 Hard to pull Hard to pull V X = V DD V V X Careful design: k mr down if m r is to A = V DD small to be able to strong sink node X V X = V DD Transmission Gate Resistance in a Transmission Gate V DD R eq high when V GS close to GND B → 0 R eq high when V GS close to V DD R R X A = V DD R R − − eq n eq p B → 1 GND V IN V OUT Symbol V V DD V X = V DD B R − eq total t V in (V) 4

Complementary Pass-transistor Logic C 2 MOS (CPL) A B Clocked Static CMOS Inputs Switching f Network φ Two Clock Phases Inverse f Inverse Switching Network Inputs φ B B B B B B Tri-state A A A - High impedance output is possible f f f f f f B B A A No Static Power A A A f f f B B B A AND/NAND OR/NOR EXOR/XNOR Dynamic Logic Example n + 2 Transistors V DD V DD V DD φ φ φ φ - 2 n in Static CMOS 2 i St ti CMOS V OH = V DD and V OL = GND f Out + AB C In PDN C L PUN C L - High impedance node at V OH In PDN A Out No Static Power C C L φ φ φ φ B Requires Clock Requires Clock GND GND φ NMOS PMOS GND Net Net 5

Domino Logic Domino Logic - Characteristics Only non-inverting logic - limits the use φ φ φ Nodes pre-charged only to be discharged - high activity PDN PDN PDN φ φ φ φ φ φ PDN PDN PDN φ φ φ All inputs are set to 0 during precharge ”CPL: The Low Power Family?” CMOS Logic Families CPL vs. CMOS CPL is often CMOS Logic Families + Fewer transistors - Need level restorer claimed to be ” The Low Power Family” + Mostly NMOS - More wires smaller transistors Non Clocked Clocked + Lower internal swing B B + No input inverters A C 2 MOS TSPC F Compl. Pass-transistor Logic Domino Clocked + Smaller stack height CMOS CVSL A + Complex functions with p CVSL DCSL DCSL A a minimum of transistors CPL SPL DPL F A XOR Low Power ? 6

CPL – XOR Gate CPL vs. CMOS – XOR Gate A= 0, B= 0 A= 0, B= 1 CPL Static CMOS B B V DD V DD B B B B B A 1 0 A 0 1 F A A A 0 0 1 0 1 0 A Q F F B A A B A 1 1 A F A A A 1 1 0 1 0 1 F F 6 NMOS 5 NMOS A A 0 0 2 PMOS 5 PMOS CPL: Fast Level Restoring CPL Example: Adder - Carry Part A Cross coupling give fast restoring Low Stacking B � Lower Power Consumption A � Small Transistors � Small Transistors Low short-circuit � Lower Power A C B B current in V DD inverters A C C o A B Carry F A C B A A A C C C o C XOR V DD A A F A A B 7

CPL Example: Adder with Low Stacking CPL Example: Adder - Sum Part A The nets are shared Sum Carry A C B � Minimum number of transistors � Lower Power A B A C S A C A A C C Only 2 O l 2 B V DD A C A C C o stacked B B B A C A C S B A C S B A C C o V DD A "0" P D B V DD A Sum Sum A C A V DD V DD B A B B A B C B B C A C o C S A C C A C S A B B A B C B B A G "1" P CPL: However! Differential Current Switch Logic Cross-coupled inverters for fast switching (compare to sense amplifiers) Most reports are on adders Phase 1: Low CLK Phase 1: Low CLK – Output is precharged Output is precharged Cross-coupled Adders and MUXes suites CPL inverters CLK CLK 1 1 Q Q Other circuitry might not show that good result good result CLK CLK CLK - R. Zimmerman, JSSC, July 97 NMOS NMOS Three Three 8

Differential Current Switch Logic Conclusions: Logic families Phase 2: High CLK � If Q falls faster � Right NMOS three is cut of � No Charge up of the right NMOS three � No Charge up of the right NMOS three � Low Power TSPC is fast but power hungry Cross-coupled inverters Static CMOS has rather low power cons. CLK CLK CPL and DCSL are known to be better Q Q CLK CLK CLK Cut of by Q NMOS NMOS Three Three Low Swing Signals Low Swing Signals: Idea Convert to low swing Restore to High swing For long wires (large C L ) Can be used locally (e.g. Pass transistors) BUS with high load Local Block Local Block Conversion between supply voltage regions is needed Restoring/ amplifying circuitry to convert Low swing signals will save power back to high voltage Delays can be reduced using repeaters 9

Low Swing Driver Low Swing Driver V DD Up Low Swing Down Low Swing UDLD NMOS transistor Driver (ULD) Driver (ULD) Driver (DLD) Driver (DLD) close when the V DD output voltage reach V DD V DD V DD -V T Only one supply is Only one supply is needed Low at 0 Low at V T Low at 0 Low at V T High at V DD -V T High at V DD -V T High at V DD High at V DD -V T Low Swing Driver Full Swing Receiver The cross-coupled Up Low Swing Down Low Swing transistors are Driver (ULD) Driver (DLD) restoring the voltage g g V DDhigh V DD V DD Two Supplies are needed 1 High Output Sving Voltage Sving Voltage 0 1 V DDlow Low Input Sving Voltage 0 Low at 2 V T Low at 0 High at V DD -2V T High at V DD 10

Full Swing Receiver Full Swing Receiver High input Up Down Full UFR � M 1 turns off swing Receiver � M 2 turns on V DD � ( (UDFR) ) M 3 turns on 3 � M 4 turns off V DD � = > Low output High V DD Low swing out swing in M 3 M 4 Low input High swing out � M 1 turns on Low High � V DD M 2 turns off swing in Low M 1 swing out � � swing in swing in M 4 turns on M turns on Low M 2 � High M 3 turns off swing in swing out � = > High output � Only one supply is needed DFR Repeaters to Reduce the Bus Delay Repeaters to Reduce the Bus Delay Consider a 20 mm long wire, 1 um wide Up Low Swing Down Low Swing UDLR R = 2 k Ω Repeater (ULR) Repeater (ULR) Repeater (DLR) Repeater (DLR) V DD C = 20 pF V DD V DD Buffer data = 200 Ω 200 Ω R R eq C out = 0.1 pF C in = 0.1 pF 11

Repeaters: Buffers Neglected Repeaters: Buffers included R R × = × × × − 12 = 0.69 0.69 2000 20 10 27.6 ns n + 1 n + 1 RC C C R C out C out C in C in C out C out C in C in n + n + 1 1 C n = number of repeaters R C × × = × × × × − 12 = 0.69 2 0.69 2 1000 10 10 13.8 ns 2 2 R C × + + + × × + + + R /2 R /2 0.69 ( 1)( ( 1) ) ( ( 1)( )) n n R n C C + eq + out in ( 1) ( 1) n n C /2 C /2 Buffer data Buffer data Example: n = 2 R eq = 200 Ω R C × × = 0.69 3 9.2 ns C out = 0.1 pF 3 3 C in = 0.1 pF R C × × + × + × + = R /3 R /3 R /3 0.69 3 ( 3 ) ( 3 ( )) R C C 3 eq 3 out in C /3 C /3 C /3 2000 20 = × × + × × + × × -12 = 0.69 3 ( 3 200) ( 3 0.2) 10 19.1 ns 3 3 Repeaters: Minimum delay 35 Minimum delay 30 30 with two repeaters ith t t 25 t p (ns) 20 Buffers included 15 10 Buffers excluded 5 0 0 1 2 3 4 5 Number of repeaters 12

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.