ECEU530 Homework 4 due Wednesday Oct 25 ECE U530 Digital Hardware - PDF document

ECEU530 Homework 4 due Wednesday Oct 25 ECE U530 Digital Hardware Synthesis Write a testbench for the ALU from Homework 3 Prof. Miriam Leeser mel@coe.neu.edu Write the MUX function from lecture 10 October 18, 2005 Write code that

ECEU530 Homework 4 due Wednesday Oct 25 ECE U530 Digital Hardware Synthesis • Write a testbench for the ALU from Homework 3 Prof. Miriam Leeser mel@coe.neu.edu • Write the MUX function from lecture 10 October 18, 2005 • Write code that calls the MUX function • Lecture 11: • Sequential Logic in VHDL • Finite State Machines in VHDL • Project proposals due now • HW 4 due Wednesday, October 25 • Use the discussion board to post questions lect11.ppt ECE U530 F06 lect11.ppt 2 ECE U530 F’06 Schedule VHDL for Synthesis with Xilinx • Homework 4 due Wednesday, October 25 • Documentation available from Xilinx: • link on course web page (External Links) • Review in class on Monday, October 30 • http://www.xilinx.com/support/sw_manuals/xilinx6/index.htm • Midterm in class on Wednesday, November 1 • From the PDF collection, we are interested in: • Homework 5: based on ECEU323 Lab 4 – Synthesis and Verification Design Guide Due Wednesday November 8 – XST Users Guide • Some material in this lecture is from: • XST Users Guide Chapter 6 VHDL language support: – Sequential Circuits lect11.ppt lect11.ppt 3 ECE U530 F’06 4 ECE U530 F’06

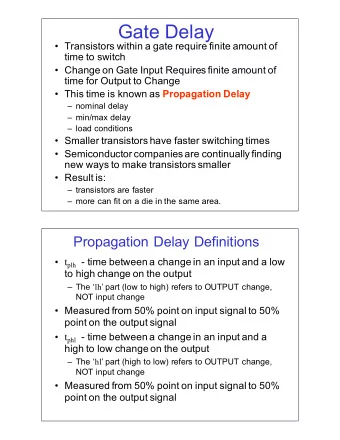

ECEU530 Sequential HW in VHDL Combinational Hardware in VHDL • We will describe synchronous, sequential hardware in • Process has no wait statements or clock signals VHDL • All signals on RHS of assignments appear in process • Synchronous, sequential hardware is clocked sensitivity list • flip-flops • Example of a good combinational HW description: • registers and shift registers process (A, B, C) • counters variable D: Std_Logic; • state machines begin A if A='1' then • I can describe sequential hardware with D := B; B • sequential VHDL statements F else • concurrent VHDL statements C D := B or C; end if; –signal assignments F <= D; • same as combinational hardware end process; lect11.ppt lect11.ppt 5 ECE U530 F’06 6 ECE U530 F’06 Good Combinational Techniques Sequential Logic when you don’t want it • All signals that effect result go in process sensity list • You can write combinational VHDL that synthesizes to sequential hardware that you did not intend • Any signal assigned in one branch is assigned in all branches: • No clock signal, no wait signal • latches are synthesized • of a case statement • If you use the VHDL term unaffected • of if-then-else clause –Why? • Use case statements (NOT nested if-then-else statements) to avoid inferring priority encoder • If you use the VHDL term null • Use don’t cares to assign to outputs –Why? • Never use don’t cares in a comparison statement • If you do NOT put the same assignment on every branch of your if--then--else or CASE statements –Why? lect11.ppt lect11.ppt 7 ECE U530 F’06 8 ECE U530 F’06

ECEU530 GOOD If statement example Null and Unaffected signal A, B, C, P1, P2, Y, Z: std_logic; case opcode is process ( A, B, C, P1, P2 ) when add => begin Acc1 <= Acc + operand; Y <= ‘0’; when subtract => Acc1 <= Acc - operand; Z <= ‘1’; when nop => if (P1 = ‘1’) then null; Y <= A; end case; elsif (P2 = ‘0’) then Y <= B; with sel select else Z <= C; Z <= A when ‘0’, end if; Z <= B when ‘1’, end process; Z <= unaffected when others; lect11.ppt lect11.ppt 9 ECE U530 F’06 10 ECE U530 F’06 Sequential Logic when you want it wait statements • Process statement with Clock on sensitivity list or • wait can be used to suspend a process for a specified wait statement time period • Wait statement or sensitivity list, never both • Example: Using wait in a testbench: -- ********************************* • Clocked, sequential hardware with sensitivity list -- process for simulating the clock • Do NOT put all signals on Right hand side on sensitivity list process begin • Do put on sensitivity list clock plus any asynchronous inputs: clk <= not(clk); –Clock, or wait for 20 ns; end process; – Clock and reset, or -- ********************************* –Clock and set, or –Clock and reset and set • Can also wait on a signal or on an event wait until clk’event wait until clk’event and clk = ‘1’ wait until clk’event and clk =’0’ lect11.ppt 11 ECE U530 F’06

ECEU530 Process Simulation Sequential vs. Combinational HW • Combinational Circuits • Output depends on current values of inputs only • Process can have wait statement or sensitivity list, but not both • No feedback • No memory • If process has sensitivity list, process is executed once at simulation start up, and after that when a • Sequential Hardware signal on the sensitivity list changes • Feedback • If process has has a wait statement, process is • Output depends on current inputs and current state executed at simulation start up, until wait statement • Circuit has memory elements is executed, then it suspends • Sequential Hardware = Combinational Hardware plus memory elements: latches, flipflops, memories ... • Process “wakes up” when wait condition is met lect11.ppt lect11.ppt 13 ECE U530 F’06 14 ECE U530 F’06 Sequential Hardware in VHDL D Latch in VHDL -- D_LATCH.VHD • Synchronous Only library IEEE; use IEEE.std_logic_1164.all; • Clock entity d_latch is • May or may not have a reset signal port ( EN, DATA: in STD_LOGIC; Q: out STD_LOGIC); end d_latch; • Sequential Hardware is defined with a particular “style” architecture BEHAV of d_latch is begin LATCH: process (EN, DATA) • VHDL synthesis tool looks for hardware described begin using that style, and translates it to flip-flops and if (EN = '1') then Q <= DATA; combinational logic end if; end process; end BEHAV; • Clock signal is special. Usually called “CLK” lect11.ppt lect11.ppt 15 ECE U530 F’06 16 ECE U530 F’06

ECEU530 D-Flipflop D-Flipflop with wait statement library IEEE; library IEEE; use IEEE.std_logic_1164.all; use IEEE.std_logic_1164.all; entity d_ff is entity d_ff is port ( CLK, DATA: in STD_LOGIC; port ( CLK, DATA: in STD_LOGIC; Q: out STD_LOGIC ); Q: out STD_LOGIC ); end d_ff; end d_ff; architecture BEHAV of d_ff is architecture with_wait of d_ff is begin begin process (CLK) begin process if (CLK'event and CLK='1') then begin Q <= DATA; wait until rising_edge(CLK); end if; Q <= DATA; end process; end process; end BEHAV; end BEHAV; lect11.ppt lect11.ppt 17 ECE U530 F’06 18 ECE U530 F’06 Edge Detection Functions D-FF with Reset process (CLK, RST) begin FUNCTION rising_edge (SIGNAL s : std_logic) RETURN BOOLEAN IS if RST = '1' then BEGIN RETURN (s’EVENT AND (s = ’1’)); Q <= ‘0’; END; elsif CLK'EVENT and CLK = '1' then FUNCTION falling_edge (SIGNAL s : std_logic) Q <= Data; RETURN BOOLEAN IS end if; BEGIN RETURN (s'EVENT AND s = ’0’)); end process; END; IMPORTANT : Use these only with the clk signal • Asynchronous Set is similar lect11.ppt lect11.ppt 19 ECE U530 F’06 20 ECE U530 F’06

ECEU530 D-FF with Clock Enable D-FF with Asynchronous Reset and Synchronous Enable • Not supported: wait until CLOCK'event and CLOCK = '0' and ENABLE = '1' ; • Supported: process(Rst, Clk) wait until CLOCK'event and CLOCK = '0' ; if ENABLE = '1' then ... begin if Rst = '0' then Q <= '0'; process(Clk) elsif rising_edge(Clk) then begin if Clk'event and Clk='1' then -- or rising_edge(Clk) if EN = ’1’ then if ENABLE = '1' then Q <= D; Q <= DATA; end if; end if; end if; end if; end process; end process; lect11.ppt lect11.ppt 21 ECE U530 F’06 22 ECE U530 F’06 Clocked Flip-flop Active Low Reset on a FF D D Q Q D D Q Q process(Clk) C Clk C begin Clk R if rising_edge(Clk) then Rst Q <= D; end if; Active low end process; -- or -- process(Rst, Clk) process begin begin if Rst = '0' then wait until rising_edge(CLK); Q <= '0'; Q <= D; end process elsif rising_edge(Clk) then Q <= D; end if; end process; lect11.ppt lect11.ppt 23 ECE U530 F’06 24 ECE U530 F’06

ECEU530 Register (Eight-bit) 8 bit register entity EXAMPLE is D(7) Q(7) port (DI : in STD_LOGIC_VECTOR (7 downto 0); D(6) Q(6) CLK : in STD_LOGIC; D (7 downto 0) Q(7 downto 0) D(5) Q(5) DO : out STD_LOGIC_VECTOR (7 downto 0)); D(4) Q(4) end EXAMPLE; D(3) Q(3) architecture ARCH1 of EXAMPLE is D(2) Q(2) begin Clk D(1) Q(1) process (CLK) D(0) Q(0) begin if CLK'EVENT and CLK = '1' then DO <= DI ; end if; end process; Clk process(Clk) end ARCH1; architecture ARCH2 of EXAMPLE is begin begin if rising_edge(Clk) then process begin Q <= D; wait until CLK'EVENT and CLK = '1'; DO <= DI; end if; end process; end process; end ARCH2; This register has no reset lect11.ppt lect11.ppt 25 ECE U530 F’06 26 ECE U530 F’06 Shift Register (Eight-bit) 8 bit register with reset entity EXAMPLE is Q(7 downto 0) Ser_In port ( DI : in STD_LOGIC_VECTOR (7 downto 0); CLK : in STD_LOGIC; RST : in STD_LOGIC; DO : out STD_LOGIC_VECTOR (7 downto 0) ); Clk end EXAMPLE; architecture ARCHI of EXAMPLE is begin process (CLK, RST) begin process(Clk) if RST = '1' then begin DO <= "00000000"; elsif CLK'EVENT and CLK = '1' then if rising_edge(Clk) then DO <= DI ; Q <= Q(6 downto 0) & Ser_In; end if; end process; end if; end ARCHI; end process; lect11.ppt lect11.ppt 27 ECE U530 F’06 28 ECE U530 F’06

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.