ECEU530 Homework 2 ECE U530 Complete Lab 2 from ECEU323 in VHDL - PDF document

ECEU530 Homework 2 ECE U530 Complete Lab 2 from ECEU323 in VHDL Digital Hardware Synthesis Describe a seven segment decoder Prof. Miriam Leeser mel@coe.neu.edu September 27, 2006 Implementing the equations using std_logic Quiz

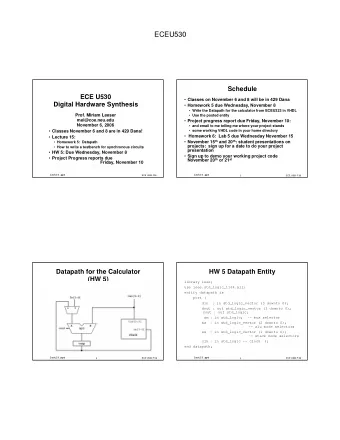

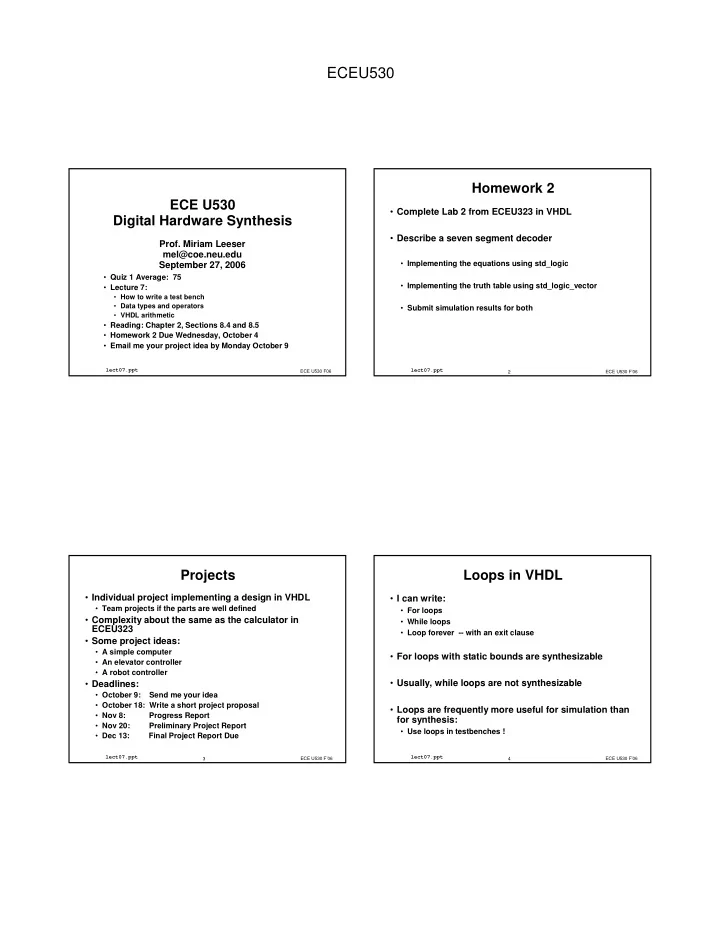

ECEU530 Homework 2 ECE U530 • Complete Lab 2 from ECEU323 in VHDL Digital Hardware Synthesis • Describe a seven segment decoder Prof. Miriam Leeser mel@coe.neu.edu September 27, 2006 • Implementing the equations using std_logic • Quiz 1 Average: 75 • Implementing the truth table using std_logic_vector • Lecture 7: • How to write a test bench • Data types and operators • Submit simulation results for both • VHDL arithmetic • Reading: Chapter 2, Sections 8.4 and 8.5 • Homework 2 Due Wednesday, October 4 • Email me your project idea by Monday October 9 lect07.ppt ECE U530 F06 lect07.ppt 2 ECE U530 F’06 Projects Loops in VHDL • Individual project implementing a design in VHDL • I can write: • Team projects if the parts are well defined • For loops • Complexity about the same as the calculator in • While loops ECEU323 • Loop forever -- with an exit clause • Some project ideas: • A simple computer • For loops with static bounds are synthesizable • An elevator controller • A robot controller • Usually, while loops are not synthesizable • Deadlines: • October 9: Send me your idea • October 18: Write a short project proposal • Loops are frequently more useful for simulation than • Nov 8: Progress Report for synthesis: • Nov 20: Preliminary Project Report • Use loops in testbenches ! • Dec 13: Final Project Report Due lect07.ppt lect07.ppt 3 ECE U530 F’06 4 ECE U530 F’06

ECEU530 For Loops For Loop Example [label:] for <identifier> in <range> loop FOR N IN 3 DOWNTO 1 LOOP sequential statement; shift_reg(N) <= shift_reg(N-1); {sequential statements}; END LOOP; end loop [label]; Unrolled Loop : shift_reg(3) <= shift_reg(2); • A loop statement is a sequential statement shift_reg(2) <= shift_reg(1); • Must be in a process shift_reg(1) <= shift_reg(0); • identifier is automatically declared and is local to the loop • Range: <integer expression> to <integer expression> • Note: N is only defined for the loop or <integer expression> downto • What goes on the process sensitivity list? <integer expression> • When synthesized, loops are usually unrolled • An integer expression evaluates to an integer • Integer expressions are evaluated at compile time lect07.ppt lect07.ppt 5 ECE U530 F’06 6 ECE U530 F’06 Inferring Hardware from a For Loop Array Attributes A’left(N) left bound of index range of dimension N of A ARCHITECTURE arch OF some IS BEGIN A’right(N) right bound of index range of dimension N of A PROCESS (A) Z A’low(N) lower bound of index range of dimension N of A BEGIN FOR i IN A’RANGE LOOP A’high(N) upper bound of index range of dimension N of A Z(i) <= NOT A(i); END LOOP; A’range(N) index range of dimension N of A END PROCESS; A’reverse_range(N) reverse of index range of dimension N of A END arch; A’length(N) length of index range of dimension N of A Unrolled loop : A’ascending(N) true if index range of dimension N of A is an Z(3) <= NOT A(3); ascending range, false otherwise Z(2) <= NOT A(2); A Z(1) <= NOT A(1); (Book page 93) Z(0) <= NOT A(0); lect07.ppt lect07.ppt 7 ECE U530 F’06 8 ECE U530 F’06

ECEU530 Using a VHDL testbench : Simulation Test Methods Stimulus Design • UUT = Unit under test; Non-portable DESIGN DESIGN • testbench = VHDL code to test UUT SIMULATOR (SCHEMATIC OR (SCHEMATIC OR STIMULUS OTHER) • testbench code is OTHER) Testbench COMMANDS usually not synthesized, usually written in a Generate Stimulus Simple behavioral style BEHAVIORAL BEHAVIORAL RTL VHDL RTL VHDL TESTBENCH UUT TESTBENCH Complex Monitor Response BEHAVIORAL BEHAVIORAL RTL VHDL RTL VHDL TESTBENCH TESTBENCH lect07.ppt lect07.ppt 9 ECE U530 F’06 10 ECE U530 F’06 VHDL Testbench VHDL Testbench Organization • Testbench code does not need to be synthesizable: • Library and package calls • anything goes • Entity declaration • Entity is empty • Generally has no inputs or outputs • UUT is a component in the testbench • Architecture section • This part is automatically generated by Xilinx tools • UUT is a component • Testbench logic is a process • All inputs and outputs to the UUT are declared as internal signals • Testbench generates all external stimuli, • including clock and reset • tests different input combinations lect07.ppt lect07.ppt 11 ECE U530 F’06 12 ECE U530 F’06

ECEU530 Tutorial Testbench Tutorial Testbench (2) LIBRARY IEEE; SIGNAL CLK : std_logic; USE IEEE.STD_LOGIC_1164.ALL; SIGNAL RESET : std_logic; USE IEEE.STD_LOGIC_ARITH.ALL; SIGNAL CE : std_logic; USE IEEE.STD_LOGIC_UNSIGNED.ALL; SIGNAL LOAD : std_logic; USE IEEE.STD_LOGIC_TEXTIO.ALL; USE STD.TEXTIO.ALL; SIGNAL DIR : std_logic; SIGNAL DIN : std_logic_vector (3 DOWNTO 0); ENTITY counter_tbw IS SIGNAL COUNT : std_logic_vector (3 DOWNTO 0); END counter_tbw; ARCHITECTURE testbench_arch OF counter_tbw IS BEGIN FILE RESULTS: TEXT OPEN WRITE_MODE IS "results.txt"; UUT : counter COMPONENT counter PORT ( PORT MAP ( CLK : In std_logic; CLK => CLK, RESET : In std_logic; RESET => RESET, CE : In std_logic; CE => CE, LOAD : In std_logic; DIR : In std_logic; LOAD => LOAD, DIN : In std_logic_vector (3 DOWNTO 0); DIR => DIR, COUNT : InOut std_logic_vector (3 DOWNTO 0) ); DIN => DIN, END COMPONENT; COUNT => COUNT); lect07.ppt lect07.ppt 13 ECE U530 F’06 14 ECE U530 F’06 Testbench from Tutorial (3) wait statements PROCESS -- clock process for CLK, • wait can be used to suspend a process for a specified BEGIN time period CLOCK_LOOP : LOOP • Example: Using wait in a testbench: CLK <= transport '0'; -- ********************************* WAIT FOR 10 ns; -- process for simulating the clock CLK <= transport '1'; process WAIT FOR 10 ns; begin WAIT FOR 40 ns; clk <= not(clk); wait for 20 ns; CLK <= transport '0'; end process; WAIT FOR 40 ns; -- ********************************* END LOOP CLOCK_LOOP; • Can also wait on a signal or on an event END PROCESS; • Most synthesis tools limit the way wait statements can be used lect07.ppt lect07.ppt 15 ECE U530 F’06 16 ECE U530 F’06

ECEU530 Testbench from Tutorial (4) Inertial vs Transport Delays --Simulation Code ���������������� simulation: process(clk) -- simulation process ENTITY nand2 IS ENTITY nand2 IS -- triggers on clock edge A C PORT( A, B : IN BIT; C : OUT BIT); PORT( A, B : IN BIT; C : OUT BIT); B variable cycle : integer := 0; END nand2; END nand2; begin ARCHITECTURE behavior OF nand2 IS ARCHITECTURE behavior OF nand2 IS case cycle is BEGIN BEGIN C <= TRANSPORT NOT(A AND B) C <= TRANSPORT NOT(A AND B) when 0 to 1 => -- reset the counter AFTER 25 ns; AFTER 25 ns; ��������������� reset <= '1'; END behavior; END behavior; ce <= '0'; ENTITY nand2 IS ENTITY nand2 IS load <= '0'; PORT( A, B : IN BIT; C : OUT BIT); PORT( A, B : IN BIT; C : OUT BIT); END nand2; dir <= '0'; END nand2; din <= (others => '0'); ARCHITECTURE behavior OF nand2 IS ARCHITECTURE behavior OF nand2 IS BEGIN BEGIN C <= NOT(A AND B) AFTER 25 ns; C <= NOT(A AND B) AFTER 25 ns; END behavior; END behavior; lect07.ppt lect07.ppt 17 ECE U530 F’06 18 ECE U530 F’06 Testbench from Tutorial(5) Testbench from Tutorial (6) when 2 to 5 => -- count up for two cycles ... reset <= '0'; when others => -- hold count value ce <= '1'; reset <= '0'; load <= '0'; ce <= '0'; dir <= '1'; load <= '0'; when 6 to 7 => -- count down for one cycle dir <= '0'; reset <= '0'; end case; ce <= '1'; cycle := cycle+1; dir <= '0'; end process; load <= '0'; ... lect07.ppt lect07.ppt 19 ECE U530 F’06 20 ECE U530 F’06

ECEU530 Testbench Example: Adder Testbench Example (2) component adder Library IEEE; port( use IEEE.STD_LOGIC_1164.all; in1 : in std_logic_vector(4 downto 0); use IEEE.STD_LOGIC_ARITH.all; in2 : in std_logic_vector(4 downto 0); use IEEE.std_logic_unsigned.all; out : out std_logic_vector(4 downto 0)); Library WORK; end component; use WORK.all; signal a : std_logic_vector(4 downto 0); entity testbench is signal b : std_logic_vector(4 downto 0); end testbench; signal c : std_logic_vector(4 downto 0); architecture test of testbench is begin signal clk : std_logic:= '0'; add1 : adder signal rst : std_logic:= '0'; port map( in1 => a, signal data_in1:std_logic_vector(4 downto 0); in2 => b, signal data_in2:std_logic_vector(4 downto 0); out => c ); signal data_out:std_logic_vector(4 downto 0); lect07.ppt lect07.ppt 21 ECE U530 F’06 22 ECE U530 F’06 Testbench Example (3) Testbench Example (4) process -- ********************************* variable i : integer; -- process for simulating the clock variable j : integer; process begin begin for i in 0 to 15 loop clk <= not(clk); for j in 0 to 15 loop wait for 20 ns; a <= CONV_STD_LOGIC_VECTOR(i, 5); end process; b <= CONV_STD_LOGIC_VECTOR(j, 5); -- ********************************* wait until (clk'event and clk='1'); end loop; end loop; end process; --****************************************** end test; CONV_STD_LOGIC_VECTOR is a function that converts an integer. Takes bitwidth of the standard logic vector. lect07.ppt lect07.ppt 23 ECE U530 F’06 24 ECE U530 F’06

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.