ECEU530 Schedule ECE U530 Homework 4 due Wednesday, October 23 - PDF document

ECEU530 Schedule ECE U530 Homework 4 due Wednesday, October 23 Digital Hardware Synthesis Write testbench for ALU Use a function Prof. Miriam Leeser Review in class on Monday, October 30 mel@coe.neu.edu I will hand out a

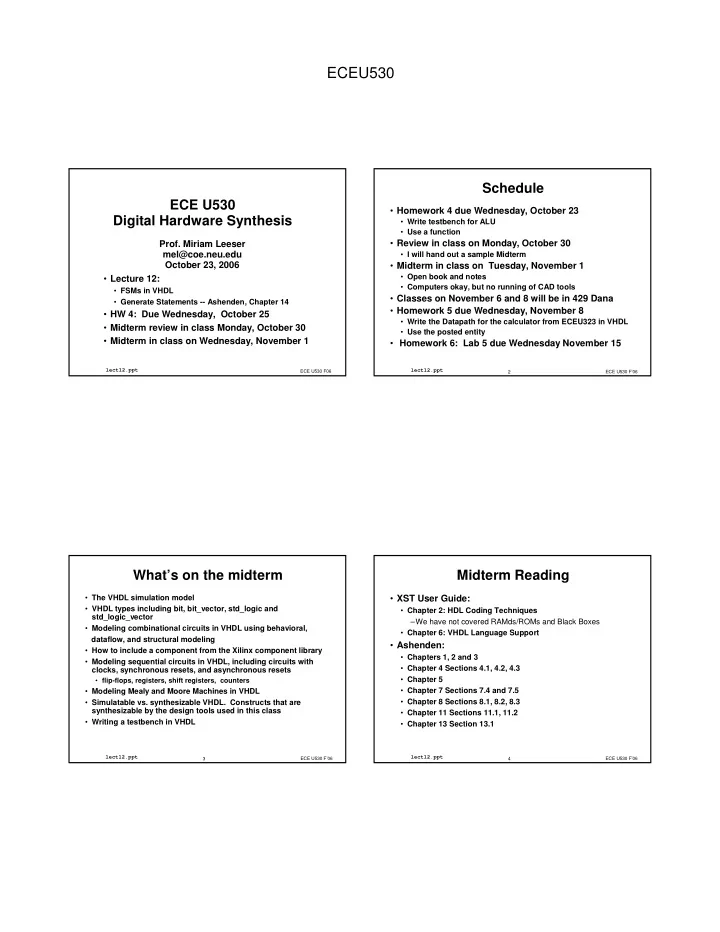

ECEU530 Schedule ECE U530 • Homework 4 due Wednesday, October 23 Digital Hardware Synthesis • Write testbench for ALU • Use a function Prof. Miriam Leeser • Review in class on Monday, October 30 mel@coe.neu.edu • I will hand out a sample Midterm October 23, 2006 • Midterm in class on Tuesday, November 1 • Open book and notes • Lecture 12: • Computers okay, but no running of CAD tools • FSMs in VHDL • Classes on November 6 and 8 will be in 429 Dana • Generate Statements -- Ashenden, Chapter 14 • Homework 5 due Wednesday, November 8 • HW 4: Due Wednesday, October 25 • Write the Datapath for the calculator from ECEU323 in VHDL • Midterm review in class Monday, October 30 • Use the posted entity • Midterm in class on Wednesday, November 1 • Homework 6: Lab 5 due Wednesday November 15 lect12.ppt ECE U530 F06 lect12.ppt 2 ECE U530 F’06 What’s on the midterm Midterm Reading • The VHDL simulation model • XST User Guide: • VHDL types including bit, bit_vector, std_logic and • Chapter 2: HDL Coding Techniques std_logic_vector –We have not covered RAMds/ROMs and Black Boxes • Modeling combinational circuits in VHDL using behavioral, • Chapter 6: VHDL Language Support dataflow, and structural modeling • Ashenden: • How to include a component from the Xilinx component library • Chapters 1, 2 and 3 • Modeling sequential circuits in VHDL, including circuits with • Chapter 4 Sections 4.1, 4.2, 4.3 clocks, synchronous resets, and asynchronous resets • Chapter 5 • flip-flops, registers, shift registers, counters • Modeling Mealy and Moore Machines in VHDL • Chapter 7 Sections 7.4 and 7.5 • Chapter 8 Sections 8.1, 8.2, 8.3 • Simulatable vs. synthesizable VHDL. Constructs that are synthesizable by the design tools used in this class • Chapter 11 Sections 11.1, 11.2 • Writing a testbench in VHDL • Chapter 13 Section 13.1 lect12.ppt lect12.ppt 3 ECE U530 F’06 4 ECE U530 F’06

ECEU530 Where to declare a function Functions can be Declared in Packages package PKG is • Any place that signals can be declared: function ADD (A,B, CIN : STD_LOGIC ) • In an architecture body before the begin statement return STD_LOGIC_VECTOR; • In a process before the begin statement end PKG; package body PKG is function ADD (A,B, CIN : STD_LOGIC ) • In a separate package return STD_LOGIC_VECTOR is • The package must be declared BEFORE it is used variable S, COUT : STD_LOGIC; variable RESULT : STD_LOGIC_VECTOR (1 downto 0); begin S := A xor B xor CIN; COUT := (A and B) or (A and CIN) or (B and CIN); RESULT := COUT & S; return RESULT; end ADD; end PKG; lect12.ppt lect12.ppt 5 ECE U530 F’06 6 ECE U530 F’06 Finite State Machine Using Function ADD use work.PKG.all; entity EXAMPLE is port ( A,B : in STD_LOGIC_VECTOR (3 downto 0); CIN : in STD_LOGIC; S : out STD_LOGIC_VECTOR (3 downto 0); Outputs Next COUT : out STD_LOGIC); Inputs Output end EXAMPLE; state Logic State architecture ARCHI of EXAMPLE is logic signal S0, S1, S2, S3 : STD_LOGIC_VECTOR (1 downto 0); register begin S0 <= ADD (A(0), B(0), CIN); S1 <= ADD (A(1), B(1), S0(1)); S2 <= ADD (A(2), B(2), S1(1)); S3 <= ADD (A(3), B(3), S2(1)); Moore machine: outputs depend on current state only S <= S3(0) & S2(0) & S1(0) & S0(0); Mealy machine: outputs depend on COUT <= S3(1); current state and inputs end ARCHI; lect12.ppt lect12.ppt 7 ECE U530 F’06 8 ECE U530 F’06

ECEU530 State Machine Diagram Example: Stop Watch Inputs: Start_stop, Reset Outputs: Count enable: advance time State Name Clear: reset time State0 Out1<=‘0’ Out2<=‘1’ START_STOP CE Moore Machine Outputs Counter and STOPWATCH RESET CLEAR Display In1=‘0’ and In2=‘1’ Condition to transition Asynch reset between states Reset will be shown once lect12.ppt lect12.ppt 9 ECE U530 F’06 10 ECE U530 F’06 1 State Diagram To Describe an FSM in VHDL • Next state function • Output function • State register to store current state • Each can be its own process • Which processes are combinational? • Which processes are sequential? lect12.ppt lect12.ppt 11 ECE U530 F’06 12 ECE U530 F’06

ECEU530 FSM Description in VHDL Stopwatch FSM Entity library IEEE; use IEEE.std_logic_1164.all; architecture FSM of DEMO is type STATE_TYPE is ( … ); signal CURRENT_STATE, NEXT_STATE : STATE_TYPE; entity STOPWATCH is begin STATE_REG: process(CLK, RESET) port( CLK, RESET, START_STOP: in std_logic; ... CE, CLEAR: out std_logic); end process; end STOPWATCH; NEXT_STATE_LOGIC: process(CURRENT_STATE, <inputs>) ... end process; START_STOP CE OUTPUT_LOGIC: process(CURRENT_STATE) ... Counter and end process; STOPWATCH RESET CLEAR end FSM; Display lect12.ppt lect12.ppt 13 ECE U530 F’06 14 ECE U530 F’06 Defining States State Register is only Sequential Part architecture FSM of STOPWATCH is architecture FSM of STOPWATCH_CTRL is type STATE_TYPE is (ZERO, START, COUNT, STOP, STOPPED); type STATE_TYPE is (ZERO, START, COUNT, STOP, ... STOPPED); begin signal CURRENT_STATE, NEXT_STATE : STATE_TYPE; ... begin end FSM; STATE_REG: process(CLK, RESET) begin if (RESET = '0') then CURRENT_STATE <= ZERO; elsif (rising_edge(CLK)) then CURRENT_STATE <= NEXT_STATE; end if; end process; ... end FSM; lect12.ppt lect12.ppt 15 ECE U530 F’06 16 ECE U530 F’06

ECEU530 Next State Logic Next State Logic (cont’d) when STOP => NS_LOGIC: process (CURRENT_STATE, START_STOP) begin if(START_STOP = '1')then case CURRENT_STATE is NEXT_STATE <= STOP; when ZERO => else if(START_STOP = '1')then NEXT_STATE <= STOPPED; NEXT_STATE <= START; end if; else when STOPPED => NEXT_STATE <= ZERO; end if; if(START_STOP = '1')then when START => NEXT_STATE <= START; if(START_STOP = '1')then else NEXT_STATE <= START; NEXT_STATE <= STOPPED; else end if; NEXT_STATE <= COUNT; end if; when others => when COUNT => NEXT_STATE <= ZERO; if(START_STOP = '1')then NEXT_STATE <= STOP; end case; else end process; NEXT_STATE <= COUNT; end if; lect12.ppt lect12.ppt 17 ECE U530 F’06 18 ECE U530 F’06 Output Logic To Describe an FSM in VHDL OUTPUT_LOGIC: process(CURRENT_STATE) begin case CURRENT_STATE is • Create an enumerated type for states when ZERO => CE <= '0'; CLEAR <= '1'; • Three processes for behavior of FSM when START => CE <= '1'; CLEAR <= '0'; 1. clocked process for state register when COUNT => 2. combinational process for next state logic CE <= '1'; CLEAR <= '0'; sensitivity list : inputs and current state when STOP => CE <= '0'; CLEAR <= '0'; 3. combination process for outputs when STOPPED => Moore Machine: sensitivity list: current state CE <= '0'; CLEAR <= '0'; Mealy Machine: sensitivity list: current state and inputs when others => CE <= '0'; CLEAR <= '1'; Where does reset go? end case; end process; lect12.ppt lect12.ppt 19 ECE U530 F’06 20 ECE U530 F’06

ECEU530 3 Process FSM in VHDL 2 Process FSM in VHDL • Define an ennumerated type for • Define an ennumerated type for current state, next state current state, next state • State register: clocked, sequential process • One sequential process, one combinational process • State register: clocked, sequential process • Next state: combinational process • Combinational process • sensitive to state, inputs • sensitive to state, inputs • computes next state AND outputs • Outputs: combinational process • natural way to describe Mealy machine • sensitive to state only: Moore Machine • sensitive to state and inputs: Mealy machine lect12.ppt lect12.ppt 21 ECE U530 F’06 22 ECE U530 F’06 FSM Description in VHDL Example State Machine library ieee; use ieee.std_logic_1164.all; architecture FSM of DEMO is entity state_machine is type STATE_TYPE is ( … ); signal CURRENT_STATE, NEXT_STATE : STATE_TYPE; port(X, CLK: in std_logic; begin Z: out std_logic); STATE_REG: process(CLK, RESET) ... end state_machine; end process; NEXT_STATE_LOGIC: process(CURRENT_STATE, <inputs>) architecture moore of state_machine is ... type state_type is (S0, S1, S2, S3); end process; signal state, next_state : state_type; OUTPUT_LOGIC: process(CURRENT_STATE) begin ... end process; end FSM; lect12.ppt lect12.ppt 23 ECE U530 F’06 24 ECE U530 F’06

ECEU530 State Machine Sequential Process Combinational Process COMB: process (state, X) SYNCH: process begin begin case state is when S0 => wait until CLK'event and CLK = '1'; Z <= '0'; state <= next_state; if X = '0' then end process SYNCH; next_state <= S0; else next_state <= S2; end if; when S1 => Z <= '1'; if X = '0' then next_state <= S0; else next_state <= S2; end if; -- ... continued on next slide end process COMB; lect12.ppt lect12.ppt 25 ECE U530 F’06 26 ECE U530 F’06 Combinational Process Example State Machine 2 COMB: process (state, X) library IEEE; begin -- ... continued from previous slide use IEEE.std_logic_1164.all; when S2 => Z <= '1'; entity seq_circuit is if X = '0' then next_state <= S2; port ( else next_state <= S3; X: in STD_LOGIC; end if; Y: in STD_LOGIC; when S3 => CLK: in STD_LOGIC; Z <= '0'; RESET: in STD_LOGIC; if X = '0' then Z: out STD_LOGIC next_state <= S3; ); else next_state <= S1; end seq_circuit; end if; end case; end process COMB; lect12.ppt lect12.ppt 27 ECE U530 F’06 28 ECE U530 F’06

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.

![How are file systems implemented? ! How do we represent CSCI [4|6]730 Directories (link file](https://c.sambuz.com/1033087/how-are-file-systems-implemented-s.webp)