ECEU530 Homework 2 ECE U530 Now due on Thursday October 5 th by - PDF document

ECEU530 Homework 2 ECE U530 Now due on Thursday October 5 th by 4pm Digital Hardware Synthesis Describe a seven segment decoder Implementing the equations using std_logic Prof. Miriam Leeser Implementing the truth table using

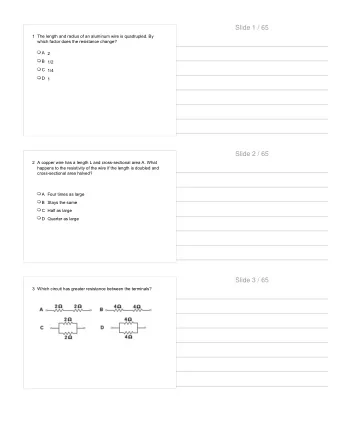

ECEU530 Homework 2 ECE U530 • Now due on Thursday October 5 th by 4pm Digital Hardware Synthesis • Describe a seven segment decoder • Implementing the equations using std_logic Prof. Miriam Leeser • Implementing the truth table using std_logic_vector mel@coe.neu.edu • Submit simulation results for both October 4, 2006 • No need to do a structural description! • Lecture 8: • For std_logic_vector : • Homework 2 -- due Thursday October 5 by 2pm Create a four bit std_logic_vector for the inputs and a seven bit • Projects std_logic_vector for the outputs. These should be internal • Homework 3 signals. Assign the inputs (A,B,C,D) to the input vector. In a • VHDL arithmetic case statement, choose a combination of inputs and for that • Reading: Sections 4.1, 4.2, 8.4, 8.5 combination assign outputs. To get the outputs in the entity you • Email me your project idea by Tuesday October 10! will need to select each of the output bits and assign them to the • Homework 3 due October 18 approprate signal in the entity. • Project Proposals due October 18 lect08.ppt ECE U530 F06 lect08.ppt 2 ECE U530 F’06 Homework 2: Waveforms Debugging VHDL • Submit a waveform for each • VHDL Errors can be cryptic!To debug: • Waveforms should be complete: • synthesize your VHDL in Xilinx. Click on the Errors tab at the bottom to see the error messages • Show outputs for all combinations of 4 inputs: A, B, C and D • Easier to do all combinations in a testbench • Click on the VHDL source code in Xilinx, then click on “launch Modelsim simulator” • An example testbench was posted with Homework 1 solutions • Sometimes Modelsim gives you better error • Submit waveform from Modelsim messages, sometimes Xilinx does. Try looking in • Save as a bitmap file both places. • Lab 2, page 5 explains how to save the waveform lect08.ppt lect08.ppt 3 ECE U530 F’06 4 ECE U530 F’06

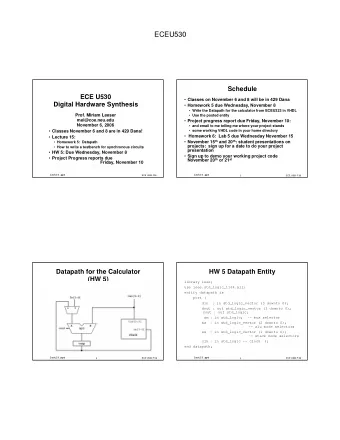

ECEU530 Testbench from HW1 Projects ENTITY testbench IS END testbench; • Individual project implementing a design in VHDL ARCHITECTURE behavior OF testbench IS signal input: std_logic_vector(7 downto 0); • Team projects if the parts are well defined signal output : std_logic; • Complexity about the same as the calculator in COMPONENT aoi PORT(a : IN std_logic; b : IN std_logic; c : IN std_logic; ECEU323 d : IN std_logic; e : IN std_logic; f : IN std_logic; • Some project ideas: g : IN std_logic; h : IN std_logic; y : OUT std_logic ); END COMPONENT; • A simple computer BEGIN • An elevator controller uut: aoi PORT MAP(a => input(0), b => input(1), c => input(2), d => input(3), e => input(4), f => input(5), g => input(6), • A robot controller h => input(7), y => output); • Deadlines: tb : PROCESS variable i : integer :=0; • October 9: Send me your idea BEGIN • October 18: Write a short project proposal for i in 0 to 127 loop input <= conv_std_logic_vector(i,8); • Nov 8: Progress Report wait for 10 ns; -- will wait forever • Nov 20: Preliminary Project Report end loop; END PROCESS; • Dec 13: Final Project Report Due END; lect08.ppt lect08.ppt 5 ECE U530 F’06 6 ECE U530 F’06 Project Proposal (Handout 4) Homework 3 due Wed, October 18 • Description of what you will describe in VHDL • Write a VHDL description of the ALU • A detailed plan of how you will implement your from ECEU323 lab 3 project • Your solution should include: • Several different implementations, each adding more functionality • An entity that describes the interface of the ALU • Example: Elevator controller • Some ports are std_logic and some ports are std_logic_vector –1 elevator, 2 floors, only up and down buttons at each floor • An architectural body for the ALU –add buttons inside the elevator • You may use any technique you wish –add open/close door functionality • What is hard? –add more floors, more elevators ... • Getting the arithmetic right • Specification of all inputs and outputs you anticipate • Carry, borrow and overflow • Writing the testbench • Entity in VHDL • Homework 4 will ask you to write a testbench for your ALU • Schedule for the rest of the semester lect08.ppt lect08.ppt 7 ECE U530 F’06 8 ECE U530 F’06

ECEU530 Package std_logic_1164 Types signed and unsigned library IEEE; type unsigned is array (natural <>) of std_logic; use IEEE.std_logic_1164.all; type signed is array (natural <>) of std_logic; • Defines types: • Defined in packages: std_ulogic • package std_logic_arith (signed) std_logic • package std_logic_unsigned (unsigned) std_ulogic_vector std_logic_vector • These packages define arithmetic operations on type • Defines logical, relation operations on these types signed and unsigned • Arithmetic is either unsigned or signed two’s • Does NOT define arithmetic operations on these types complement lect08.ppt lect08.ppt 9 ECE U530 F’06 10 ECE U530 F’06 Numeric Packages Representing Signed Values • If you want arithmetic operations, your code should start with: Value Sign Magnitude one’s comp two’s comp library IEEE; +7 0111 0111 0111 +6 0110 0110 0110 use IEEE.std_logic_1164.all; +5 0101 0101 0101 +4 0100 0100 0100 use ieee.numeric_std.all; +3 0011 0011 0011 or +2 0010 0010 0010 +1 0001 0001 0001 library IEEE; +0 0000 0000 0000 -0 1000 1111 ----- use IEEE.std_logic_1164.all; -1 1001 1110 1111 -2 1010 1101 1110 use ieee.std_logic_arith.all; -3 1011 1100 1101 -4 1100 1011 1100 use ieee.std_logic_unsigned.all; -5 1101 1010 1011 -6 1110 1001 1010 -7 1111 1000 1001 -8 ----- ---- 1000 The second option is what the Xilinx tools use by default lect08.ppt lect08.ppt 11 ECE U530 F’06 12 ECE U530 F’06

ECEU530 Types Signed and Unsigned Types Signed and Unsigned Data Type Value • definitions of types Unsigned and Signed are identical 0 to 2 N - 1 to definition of std_logic_vector: unsigned -2 (N-1) to 2 (N-1) - 1 signed --signed two’s complement type UNSIGNED is array (natural range <>) of std_logic; signal A_unsigned: unsigned(3 downto 0); signal B_signed: signed(3 downto 0); type SIGNED is array (natural range <>) of std_logic; signal C_slv: std_logic_vector(3 downto 0); A_unsigned <= “1111”; -- value is ______ • How are these types distinguished from one another? B_signed <= “1111”; -- value is ______ • How do these generate signed and unsigned C_slv <= “1111”; -- value is _______ arithmetic? lect08.ppt lect08.ppt 13 ECE U530 F’06 14 ECE U530 F’06 Signed and Unsigned Arithmetic Signed and Unsigned Arithmetic • For each operator, a unique function is called: UNSIGNED’(“1000”) -- has value ______ SIGNED’(“1001”) -- has value ______ function “+” (L,R: signed) return signed; SIGNED’(“0101”) -- has value ______ function “+” (L,R: unsigned) return unsigned; SIGNED’(“1011”) -- has value ______ • This is called operator overloading • What is difference? • A different “+” function is called depending on the types of • how bits are interpretted the operands • how +, - are defined • VHDL uses operator overloading often • how relational operations are defined: • relational operators • is “1011” < “1010” ? • logical operators • arithmetic operators lect08.ppt lect08.ppt 15 ECE U530 F’06 16 ECE U530 F’06

ECEU530 More Operators Arithmetic Operators • Arithmetic operators (defined on types integer, • Logic operators are defined as bitwise on signed, unsigned) std_logic_vectors: • +, -, & signal A,D: std_logic_vector(3 downto 0); • Unary (sign) operators: +, - on integers signal B,C: std_logic_vector(1 downto 0); • Multiplying operators: * / mod rem signal check: Boolean; • Other operators: D <= (not B) & (not C); • ** raise to a power: must be 2**n to synthesize check <= ( D = (not (B & C))); (for most CAD tools) • abs defined on signed types only • Can’t add, subtract std_logic_vectors • not • Can add, subtract signed, unsigned • Unless you use package std_logic_unsigned • Note: mod and rem return the same result, but may differ in –Allows you to add, subtract slv using unsigned arithmetic their sign depending on the sign of the divisor • Not recommended lect08.ppt lect08.ppt 17 ECE U530 F’06 18 ECE U530 F’06 Arithmetic Operators Types and Subtypes • Convert std_logic_vectors to signed or unsigned first • Users can specify new types and new subtypes • A subtype is a constrained version of an existing type signal A: std_logic_vector(3 downto 0); signal A_unsigned: unsigned(3 downto 0); subtype small_int is integer range -128 to 127; variable deviation: small_int; A_unsigned <= unsigned’(A); variable adjustment: integer; A <= std_logic_vector’(A_unsigned); deviation := deviation + adjustment; • unsigned’() and std_logic_vector’() are type conversion functions • This is legal VHDL. Can mix types small_int and • they are overloaded functions integer. Result must be in the range -128 to 127. • std_logic_vector’() is defined differently for • Can use all the operations of integer with a subtype parameters of type signed and unsigned based on integer lect08.ppt lect08.ppt 19 ECE U530 F’06 20 ECE U530 F’06

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.

![[I NTER P ROCESS C OMMUNICATIONS ] Shrideep Pallickara Computer Science Colorado State](https://c.sambuz.com/1068564/i-nter-p-rocess-c-ommunications-s.webp)