ECEU530 Project Proposal (Handout 4) ECE U530 Description of what - PDF document

ECEU530 Project Proposal (Handout 4) ECE U530 Description of what you will describe in VHDL Digital Hardware Synthesis A detailed plan of how you will implement your project Prof. Miriam Leeser Several different implementations,

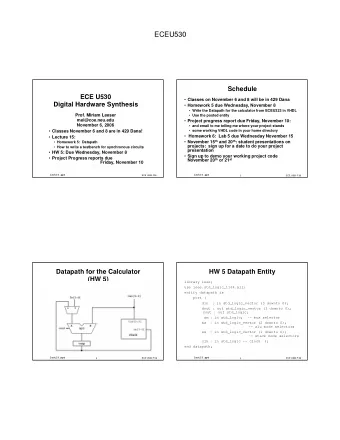

ECEU530 Project Proposal (Handout 4) ECE U530 • Description of what you will describe in VHDL Digital Hardware Synthesis • A detailed plan of how you will implement your project Prof. Miriam Leeser • Several different implementations, each adding more mel@coe.neu.edu functionality October 16, 2006 • Example: Elevator controller • Lecture –1 elevator, 2 floors, only up and down buttons at each floor –add buttons inside the elevator • Functions in VHDL –add open/close door functionality • Sequential Hardware –add more floors, more elevators ... • Reading: Sections • Specification of all inputs and outputs you anticipate • Homework 3 due October 18 • Entity in VHDL • Project Proposals due October 18 • Schedule for the rest of the semester lect10.ppt lect10.ppt ECE U530 F06 2 ECE U530 F’06 Submitting Homework Homework 3 due Wed, October 18 • In your ECEU530 directory for submitting homework: • Write a VHDL description of the ALU • Create subdirectories for each assignment from ECEU323 lab 3 –HW1, HW2, ... • Your solution should include: • Put your VHDL files in THAT directory • An entity that describes the interface of the ALU • Do not create extra levels of hierarchy • Some ports are std_logic and some ports are std_logic_vector • An architectural body for the ALU • Do NOT put any files in this directory except what you • You may use any technique you wish want to submit • What is hard? • Getting the arithmetic right • MAKE SURE YOU PUT THIS HOMEWORK IN A • Carry, borrow and overflow DIRECTORY CALLED HW3! • Writing the testbench • Homework 4 will ask you to write a testbench for your ALU lect10.ppt lect10.ppt 3 ECE U530 F’06 4 ECE U530 F’06

ECEU530 Homework 2: Process Sensitivity List Homework 4 due Wednesday, Oct 25 architecture Behavioral of hw2 is signal input: std_logic_vector(3 downto 0); signal output: std_logic_vector(6 downto 0); begin input <= (A,B,C,D); • Write a testbench for the ALU from Homework 3 process ( input, output ) begin case input is when "0000" => output <= "1111110"; -- 0 when "0001" => output <= "0110000"; -- 1 • Write a MUX4 function when "0010" => output <= "1101101"; -- 2 when "0011" => output <= "1111001"; -- 3 • Call your MUX4 function from within a VHDL when "0100" => output <= "0110011"; -- 4 when "0101" => output <= "1011011"; -- 5 architecture when "0110" => output <= "1011111"; -- 6 ... when others => output <= "-------"; -- dont care • Described on next few slides end case; Sa <= output(6); Sb <= output(5); Sc <= output(4); Sd <= output(3); Se <= output(2); Sf <= output(1); Sg <= output(0); end process; end Behavioral; lect10.ppt lect10.ppt 5 ECE U530 F’06 6 ECE U530 F’06 HW4: Implement this functionality To Guarantee Resource Sharing process(OpSel, A, B, C, D, E, F, G, H) • Create a function called Mux4 begin case OpSel is X <= Mux4(OpSel, A, C, E, G); when ”00” => Z <= A - B; Y <= Mux4(OpSel, B, D, F, H); when ”01” => Z <= C - D; when ”10” => Z <= E - F; Z <= X � Y; when ”11” => Z <= G - H; Z <= (others => ’ � ’) ; when others => • Function is NOT a component end case; • more on functions and procedures later end process; • with a function • This guarantees one subtractor is inferred lect10.ppt lect10.ppt 7 ECE U530 F’06 8 ECE U530 F’06

ECEU530 Functions Functions • Declared by specifying: • Algorithmically generates and returns only one value • May be on right hand side of expression • Must always return a value 1) The name of the function • must always contain a return statement 2) The input parameters, (if any), and their type • Executes in zero simulation time • No process statements inside a function 3) The type of the returned value • Functions cannot contain wait statements 4) Any declarations required by the function itself 5) An algorithm for the computation of the returned value lect10.ppt lect10.ppt 9 ECE U530 F’06 10 ECE U530 F’06 Function Syntax Function Example function identifier [ parameter_interface_list ] subtype word_8 is std_logic_vector(7 downto 0); return {type} is function byte_to_int ( my byte : word_8 ) { subprogram_declarative_part } return integer is begin variable result : integer : = 0 ; begin { sequential_statement } for index in 0 to 7 loop [ label : ] return expression ; result : = result*(2**index) + mybyte(index) ; end [ function ] [ identifier ] ; end loop ; return result ; end function byte_to_int ; lect10.ppt lect10.ppt 11 ECE U530 F’06 12 ECE U530 F’06

ECEU530 Function Calling Pure Functions • A pure function does not refer to any variables or signals declared by parent • Once declared, can be used in any expression • Result of function only depends on parameters passed to it • A function Is not a sequential statement: • Always returns the same value for same passed • It is called as part of an expression parameters: • A pure function does not have any state function_name [ label : ] [ parameter_association_list ] ; • If not stated explicitly, a function is assumed to be pure lect10.ppt lect10.ppt 13 ECE U530 F’06 14 ECE U530 F’06 Functions can be Declared in Packages Using Function ADD package PKG is use work.PKG.all; function ADD (A,B, CIN : STD_LOGIC ) entity EXAMPLE is return STD_LOGIC_VECTOR; port ( A,B : in STD_LOGIC_VECTOR (3 downto 0); end PKG; CIN : in STD_LOGIC; package body PKG is S : out STD_LOGIC_VECTOR (3 downto 0); function ADD (A,B, CIN : STD_LOGIC ) COUT : out STD_LOGIC); return STD_LOGIC_VECTOR is end EXAMPLE; variable S, COUT : STD_LOGIC; architecture ARCHI of EXAMPLE is variable RESULT : STD_LOGIC_VECTOR (1 downto 0); signal S0, S1, S2, S3 : STD_LOGIC_VECTOR (1 downto 0); begin begin S0 <= ADD (A(0), B(0), CIN); S := A xor B xor CIN; COUT := (A and B) or (A and CIN) or (B and CIN); S1 <= ADD (A(1), B(1), S0(1)); RESULT := COUT & S; S2 <= ADD (A(2), B(2), S1(1)); return RESULT; S3 <= ADD (A(3), B(3), S2(1)); S <= S3(0) & S2(0) & S1(0) & S0(0); end ADD; COUT <= S3(1); end PKG; end ARCHI; lect10.ppt lect10.ppt 15 ECE U530 F’06 16 ECE U530 F’06

ECEU530 VHDL Testbench Components in your Design • Testbench code does not need to be synthesizable: • A component is a structural entity: • anything goes • Just like you did for the structural design in Homework 1 • Similar to the way it is done in a testbench • Entity is empty • Your component is compiled in library work • UUT is a component in the testbench library work; • This part is automatically generated by our tools • All inputs and outputs to the UUT are declared as use work.all; internal signals • Testbench generates all external stimulus, • Declare the component in your architecture • including clock and reset • Instantiate the component and wire it up using a port • tests different input combinations map lect10.ppt lect10.ppt 17 ECE U530 F’06 18 ECE U530 F’06 Using Components Synthesizable Subset of VHDL library IEEE; • Not all VHDL constructs are synthesizable use ieee.std_logic_1164.all; • What is synthesizable differs from one tool to another library work; use work.all; • Most synthesis tools support: • Loops whose bounds can be determined at compile time architecture test of tb is • Functions that can be expanded in-line component aoi_structural port (a,b,c,d: in std_logic; e: out std_logic); • Most synthesis tools do NOT support: end component; • Arbitrary loops: –While loops, loops with exit statements signal a,b,c,d,e: std_logic ; • Procedures begin uut: aoi_structural port map(a => a, b=>b, c=>c, d=>d, e=>e); ... lect10.ppt lect10.ppt 19 ECE U530 F’06 20 ECE U530 F’06

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.