Learning Outcomes I understand the control inputs to counters I can - PowerPoint PPT Presentation

2-2.1 2-2.2 Learning Outcomes I understand the control inputs to counters I can design logic to control the inputs of Spiral 2-2 counters to create a desired count sequence I understand how smaller adder blocks can be combined to

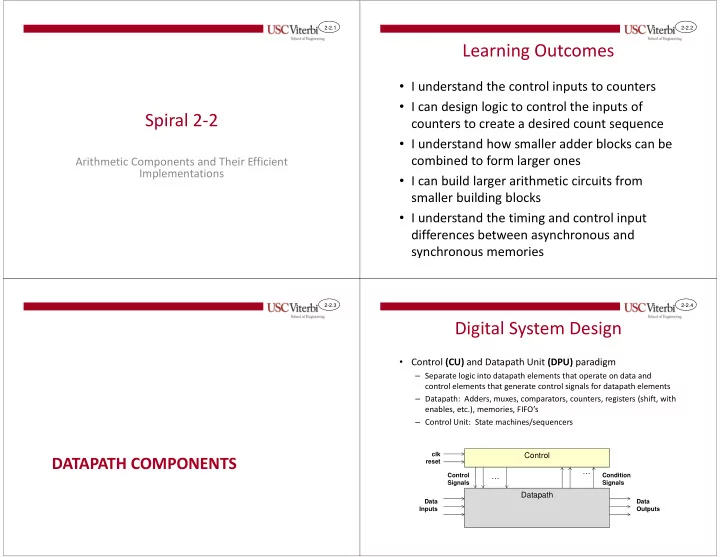

2-2.1 2-2.2 Learning Outcomes • I understand the control inputs to counters • I can design logic to control the inputs of Spiral 2-2 counters to create a desired count sequence • I understand how smaller adder blocks can be combined to form larger ones Arithmetic Components and Their Efficient Implementations • I can build larger arithmetic circuits from smaller building blocks • I understand the timing and control input differences between asynchronous and synchronous memories 2-2.3 2-2.4 Digital System Design • Control (CU) and Datapath Unit (DPU) paradigm – Separate logic into datapath elements that operate on data and control elements that generate control signals for datapath elements – Datapath: Adders, muxes, comparators, counters, registers (shift, with enables, etc.), memories, FIFO’s – Control Unit: State machines/sequencers clk Control DATAPATH COMPONENTS reset … Control Condition … Signals Signals Datapath Data Data Inputs Outputs

2-2.5 2-2.6 Overflow • Overflow occurs when the result of an arithmetic operation is __________ to be represented with the given number of bits – Unsigned overflow occurs when adding or subtracting unsigned numbers Detecting Overflow Helps Us Perform Comparison – Signed (2’s complement overflow) overflow occurs OVERFLOW & COMPARISON when adding or subtracting 2’s complement numbers 2-2.7 2-2.8 Unsigned Overflow 2’s Complement Overflow 0 Overflow occurs when you cross -1 +1 0000 this discontinuity 0 1111 0001 -2 +15 +2 +1 0000 1110 0010 1111 0001 +14 -3 +2 +3 1101 1110 0010 0011 5 + 7 = +12 +13 +3 1101 0011 -4 1100 0100 +4 Plus 7 -6 + -4 = -10 10 + 7 = 17 +12 1100 0100 +4 1011 0101 -5 +5 With 4-bit 2’s complement 1010 With 4-bit unsigned numbers we 10 0110 1011 0101 +11 numbers we can only represent +5 -6 1001 0111 +6 can only represent 0 – 15. Thus, 1010 -8 to +7. Thus, we say overflow 0110 1000 we say overflow has occurred. +7 -7 has occurred. +10 1001 0111 +6 -8 1000 +7 +9 +8 Overflow occurs when you cross this discontinuity

2-2.9 2-2.10 Testing for Overflow Testing for Unsigned Overflow • Unsigned Overflow has occurred if… • Most fundamental test – Unsigned Addition: If final carry-out = ___ – Check if answer is _______ (i.e. Positive + Positive yields a – Unsigned Subtraction: If final carry-out = ___ negative) • Unsigned overflow test [Different for add or sub] 1011 1011 – Addition: If carry-out of final position equals ____ + 0110 + 0011 – Subtraction: If carry-out of final addition equals ____ • Signed (2’s complement) overflow test [Same for add or sub] 1011 0110 – Only occurs if ________________________________ - 0110 - 1011 – Alternate test: if ____________________ of final column are different 2-2.11 2-2.12 Testing for 2’s Comp. Overflow Checking for Overflow • Produce additional outputs to indicate if • 2’s Complement Overflow Occurs If… unsigned (UOV) or signed (SOV) overflow – Test 1: If pos. + pos. = neg. or neg. + neg. = pos. – Test 2: If carry-in to MSB position and carry-out of MSB has occurred position are different 0101 (5) 1100 (-4) + 0110 (6) + 1001 (-7) X Y X Y X Y X Y Full Full Full Full C out C in C out C in C out C in C out C in Adder Adder Adder Adder S S S S 0011 (3) 1110 (-2) + 0010 (2) + 1010 (-6)

2-2.13 2-2.14 Comparison Via Subtraction • Suppose we want to compare two numbers: A & B • Suppose we let DIFF = A-B…what could the result tell us – If DIFF < 0, then _______ – If DIFF = 0, then _______ – IF DIFF > 0, then _______ • How would we know DIFF == 0? COMPARISON – If all bits of our answer _________________________. • How would we know DIFF < 0 (i.e. negative)? – Signed: __________! (but what about overflow) – Unsigned: Huh? In unsigned there are no negative results 2-2.15 2-2.16 Unsigned Comparator Computing A<B from "Negative" Result • A comparator can be built by using a subtractor Unsigned Signed • Perform A-B • Perform A-B • If A-B would yield a negative • If there is no overflow (V=0) , result, this will appear as simply check if _________ A=B __________in an unsigned • But if there is overflow?? subtraction – Recall overflow has the effect of A • And we know unsigned flipping the sign of the result to A[3:0] A>B the opposite of what it should be. subtraction overflow occurs DIFF[3:0] • So if there is overflow (V=1) Res[3:0] if __________ check is ________(i.e. positive) Subtractor • So just check if _______ B B[3:0] • Summary: A-B is "truly" C4 A<B negative if:

2-2.17 2-2.18 Signed Comparator Summary • A comparator can be built by using a subtractor • You should now be able to build: – Fast Adders – Comparators A=B A A[3:0] A>B DIFF[3:0] Res[3:0] Subtractor B B[3:0] C4 A<B 2-2.19 2-2.20 Addition – Full Adders • Be sure to connect first C in to 0 0110 = X + 0111 = Y 0 0 1 1 1 1 0 1 ADDER TIMING X Y X Y X Y X Y Full Full Full Full 0 C out C in C out C in C out C in C out C in Adder Adder Adder Adder S S S S

2-2.21 2-2.22 Timing Timing Example • Assume that we were adding one set of inputs and • A chain of full adders presents an interesting timing analysis then change to a new set of inputs: problem • To correctly compute its own Sum and Carry-out, each full Old inputs: 0000 New inputs: 1111 adder requires the carry-out bit from the ________ full adder 0010 = X 1111 = X • Because hardware works in parallel, the full adders further + 0001 = Y + 0001 = Y down the chain may _____________ produce the _______ outputs because the carry has not had time to ___________ 0011 0000 to them Old inputs: 0 0 1 0 0 0 0 1 X Y X Y X Y X Y X Y X Y X Y X Y 0 0 0 0 Full Full Full Full C out C in C out C in C out C in C out C in 0 Full Full Full Full C out C in C out C in C out C in C out C in 0 Adder Adder Adder Adder Adder Adder Adder Adder S S S S S S S S 0 0 1 1 2-2.23 2-2.24 Timing Timing • At the time just before we enter the new • Now we enter the new inputs and all the FA’s input values, all carries are 0’s starting adding their respective inputs 0000 1111 New inputs: 1111 = X 0010 = X Time Time -1 + 0001 = Y 0 + 0001 = Y 0000 0011 Old inputs: New inputs: 0 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 X Y X Y X Y X Y X Y X Y X Y X Y 0 0 0 0 0 0 0 0 Full Full Full Full Full Full Full Full C out C in C out C in C out C in C out C in 0 C out C in C out C in C out C in C out C in 0 Adder Adder Adder Adder Adder Adder Adder Adder S S S S S S S S 0 0 1 1 Due to propagation delay, the carries are still from the old inputs

2-2.25 2-2.26 Timing Timing • Each adder computes from the current inputs (notice the • The carry is “rippling” through each adder sum of 1110 is incorrect at this point) 1111 1111 1111 = X 1111 = X Time Time + 0001 = Y 1 + 0001 = Y 2 0000 0000 1 0 1 0 1 0 1 1 1 0 1 0 1 0 1 1 X Y X Y X Y X Y X Y X Y X Y X Y 0 0 0 1 0 0 1 1 Full Full Full Full Full Full Full Full C out C in C out C in C out C in C out C in 0 C out C in C out C in C out C in C out C in 0 Adder Adder Adder Adder Adder Adder Adder Adder S S S S S S S S 1 1 1 0 1 1 0 0 Now the carries are all based off the new inputs 2-2.27 2-2.28 Timing Timing • Only after the carry propagates through all the adders is the • The carry is “rippling” through each adder sum valid and correct 1111 1111 1111 = X 1111 = X Time Time + 0001 = Y 3 + 0001 = Y 4 0000 0000 1 0 1 0 1 0 1 1 1 0 1 0 1 0 1 1 X Y X Y X Y X Y X Y X Y X Y X Y 0 1 1 1 1 1 1 1 Full Full Full Full Full Full Full Full 0 0 C out C in C out C in C out C in C out C in C out C in C out C in C out C in C out C in Adder Adder Adder Adder Adder Adder Adder Adder S S S S S S S S 1 0 0 0 0 0 0 0

2-2.29 2-2.30 “Ripple-Carry” Adder Ripple Carry Adder Delay time • The longest path through a • An n-bit ripple carry adder has a worst case chain of full adders is the delay proportional to _____ carry path • We say that the carry “_________” through the adder 1 0 1 0 1 0 1 1 1 0 1 0 1 0 1 1 X Y X Y X Y X Y X Y X Y X Y X Y 1 1 1 1 Full Full Full Full 0 C out C in C out C in C out C in C out C in 1 1 1 1 Full Full Full Full Adder Adder Adder Adder C out C in C out C in C out C in C out C in 0 Adder Adder Adder Adder C 4 C 3 C 2 C 1 C 0 S S S S S S S S 0 0 0 0 0 0 0 0 2-2.31 2-2.32 Glitches Output Glitches • ______________, ___________ output values • Delay of the carry causes glitches on the due to _____________ arrival times of gate sum bits inputs • Glitch = momentarily, incorrect output value early 0 → 1 0 → 0 X Y X Y X Y X Y late 1 1 0 → 1 Full Full Full Full C out C in C out C in C out C in C out C in 0 Adder Adder Adder Adder S S S S S 3 0 → 1 → 0

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.