ECEU530 Schedule ECE U530 Midterm in class on Wednesday, November - PDF document

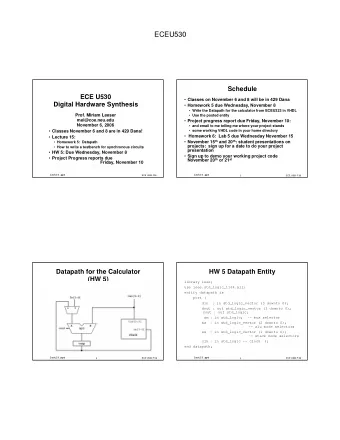

ECEU530 Schedule ECE U530 Midterm in class on Wednesday, November 1 Digital Hardware Synthesis Open book and notes Computers okay, but no running of CAD tools Prof. Miriam Leeser Classes on November 6 and 8 will be in 429 Dana

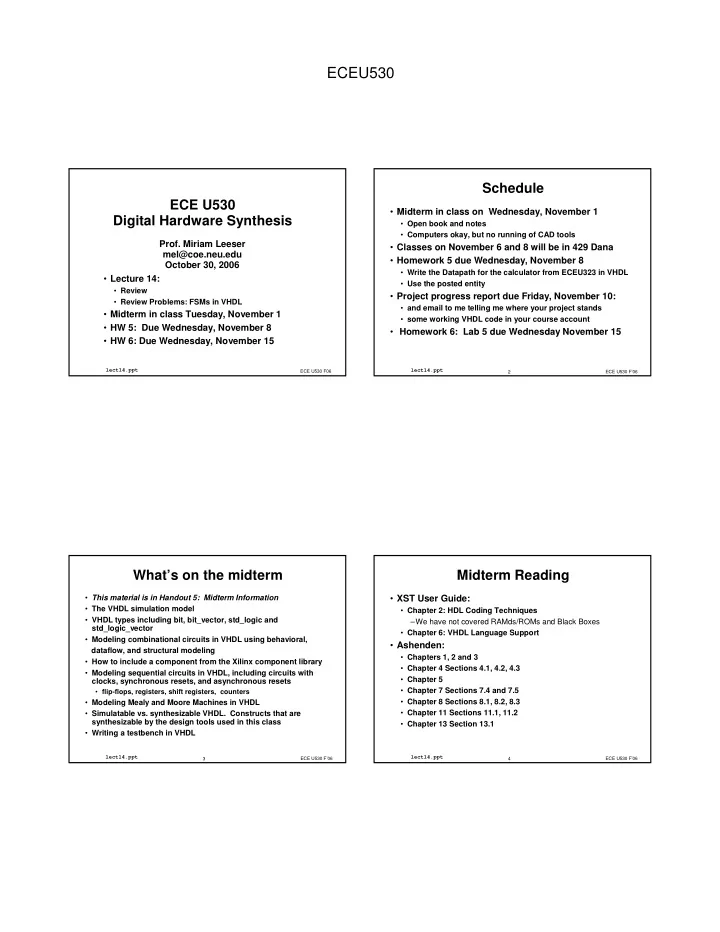

ECEU530 Schedule ECE U530 • Midterm in class on Wednesday, November 1 Digital Hardware Synthesis • Open book and notes • Computers okay, but no running of CAD tools Prof. Miriam Leeser • Classes on November 6 and 8 will be in 429 Dana mel@coe.neu.edu • Homework 5 due Wednesday, November 8 October 30, 2006 • Write the Datapath for the calculator from ECEU323 in VHDL • Lecture 14: • Use the posted entity • Review • Project progress report due Friday, November 10: • Review Problems: FSMs in VHDL • and email to me telling me where your project stands • Midterm in class Tuesday, November 1 • some working VHDL code in your course account • HW 5: Due Wednesday, November 8 • Homework 6: Lab 5 due Wednesday November 15 • HW 6: Due Wednesday, November 15 lect14.ppt ECE U530 F06 lect14.ppt 2 ECE U530 F’06 What’s on the midterm Midterm Reading • This material is in Handout 5: Midterm Information • XST User Guide: • The VHDL simulation model • Chapter 2: HDL Coding Techniques • VHDL types including bit, bit_vector, std_logic and –We have not covered RAMds/ROMs and Black Boxes std_logic_vector • Chapter 6: VHDL Language Support • Modeling combinational circuits in VHDL using behavioral, • Ashenden: dataflow, and structural modeling • Chapters 1, 2 and 3 • How to include a component from the Xilinx component library • Chapter 4 Sections 4.1, 4.2, 4.3 • Modeling sequential circuits in VHDL, including circuits with • Chapter 5 clocks, synchronous resets, and asynchronous resets • Chapter 7 Sections 7.4 and 7.5 • flip-flops, registers, shift registers, counters • Chapter 8 Sections 8.1, 8.2, 8.3 • Modeling Mealy and Moore Machines in VHDL • Simulatable vs. synthesizable VHDL. Constructs that are • Chapter 11 Sections 11.1, 11.2 synthesizable by the design tools used in this class • Chapter 13 Section 13.1 • Writing a testbench in VHDL lect14.ppt lect14.ppt 3 ECE U530 F’06 4 ECE U530 F’06

ECEU530 Q1: 4 errors Q2a: VHDL Code library ieee; library IEEE; use ieee.std_logic_1164.all; use IEEE.std_logic_1164.all; entity my_ckt is entity exam21 is port(CLK, RESET, EN, I1 : in std_logic; port (D: in STD_LOGIC; Q : out std_logic_vector(3 downto 0) ); EN: in STD_LOGIC; end my_ckt; Q: out STD_LOGIC ); architecture behavioral of my_ckt is end exam21; signal internal : std_logic_vector(1 to 4); architecture exam21_arch of exam21 is begin begin if RESET then process(D, EN) internal <= "1111"; begin elsif (CLK'event and (CLK = '1') and EN = '1') then if EN = '1' internal <= I1 & internal(2 downto 0); then Q <= D; end if; end if; Q <= internal; end process; end behavioral; end exam21_arch; lect14.ppt lect14.ppt 5 ECE U530 F’06 6 ECE U530 F’06 Q2a: Timing Diagram Q2b: VHDL Code entity exam22 is port (D: in STD_LOGIC; CLK: in STD_LOGIC; EN Reset: in STD_LOGIC; Q: out STD_LOGIC ); D end exam22; architecture exam22_arch of exam22 is Q begin process(D, CLK, Reset) begin if Reset = '1' then Q <= ‘0’; elsif CLK’EVENT and CLK = ‘1’ then Q <= D; end if; end process; end exam22_arch; lect14.ppt lect14.ppt 7 ECE U530 F’06 8 ECE U530 F’06

ECEU530 Q2b: Timing Diagram Q2c • Part (a) has no reset signal. Is one needed? Why or why not? Reset CLK D Q lect14.ppt lect14.ppt 9 ECE U530 F’06 10 ECE U530 F’06 Q3: VHDL code Q3:a entity mygate is • Draw the schematic that is defined by the VHDL code. port (A, B, C, D : in STD_LOGIC; Y: out STD_LOGIC); end mygate; architecture structural of mygate is component nand2 port (i0,i1: in std_logic; o: out std_logic); end component; signal y1,y2: STD_LOGIC; begin u1: nand2 port map (i0 => A, i1 => B, o => y1); u2: nand2 port map (i0 => C, i1 => D, o => y2); u3: nand2 port map (i0 => y1, i1 => y2, o => Y); end structural; lect14.ppt lect14.ppt 11 ECE U530 F’06 12 ECE U530 F’06

ECEU530 Q3:b Q3:c • Write a Boolean logic function for the function Y. Simplify • When you simulate the circuit, the signal y1 does not it as much as possible. appear in your simulation. Why not? • Explain why the input ports for the logic gate are named i0 and i1 . Can they be named something else? lect14.ppt lect14.ppt 13 ECE U530 F’06 14 ECE U530 F’06 Q4: VHDL Code: entity Q4: VHDL Code (1 of 3 ) library IEEE; architecture seq_circuit_arch of seq_circuit is type state_type is (A, B); use IEEE.std_logic_1164.all; signal state, next_state:state_type; entity seq_circuit is begin port ( X: in STD_LOGIC; state_register:process (CLK, RESET) begin if RESET='1' then Y: in STD_LOGIC; state <= A; CLK: in STD_LOGIC; elsif (CLK'event and CLK='1') then RESET: in STD_LOGIC; state <=next_state; end if; Z: out STD_LOGIC ); end process; end seq_circuit; lect14.ppt lect14.ppt 15 ECE U530 F’06 16 ECE U530 F’06

ECEU530 Q4: VHDL Code (2 of 3) Q4: VHDL Code (3 of 3) process (X, Y, state) begin end process; case state is process (X, state) begin when A => case state is if (X='1' and Y='0') then next_state <= B; when A => else next_state <= A; Z <= X; end if; when B => when B => Z <= not X; if (Y='1') then next_state <= A; end case; else next_state <= B; end process; end if; end seq_circuit_arch; end case; end process; lect14.ppt lect14.ppt 17 ECE U530 F’06 18 ECE U530 F’06 Q4: a Q4:b • Draw the entity for this circuit. • Draw the state diagram for this circuit. Clearly label all inputs, states and outputs. Show the behavior on reset. lect14.ppt lect14.ppt 19 ECE U530 F’06 20 ECE U530 F’06

ECEU530 Q4:c Q5 • Is this a Mealy machine or a Moore Machine? Explain • Write VHDL code to implement an S-R flipflop with your answer. asynchronous reset. The table for an S-R flip flop is given below. A D in the table indicates a don’t care, and an X indicates an error state. S R Q Q* 0 0 0 0 0 0 1 1 0 1 D 0 1 0 D 1 1 1 D X lect14.ppt lect14.ppt 21 ECE U530 F’06 22 ECE U530 F’06 Q5: entity To Describe an FSM in VHDL entity SRFF is • Next state function port (S: in STD_LOGIC; • Output function R: in STD_logic; • State register to store current state Reset: in STD_LOGIC; CLK: in STD_LOGIC; • Each can be its own process Q: out STD_LOGIC ); end SRFF; • State register is ONLY sequential process • Next state, output are purely combinational • Can combine these into one process lect14.ppt lect14.ppt 23 ECE U530 F’06 24 ECE U530 F’06

ECEU530 J-K Flip-Flop JK FlipFlop in VHDL lect14.ppt lect14.ppt 25 ECE U530 F’06 26 ECE U530 F’06 Odd Parity Generator Odd Parity Generator in VHDL • Input is a stream of bits • Output is 1 if odd number of ones seen on input • 0 otherwise lect14.ppt lect14.ppt 27 ECE U530 F’06 28 ECE U530 F’06

ECEU530 String Recognizer Example String Recognizer in VHDL • Recognize the string: 1011 • Input: 1 0 0 1 0 1 1 0 1 1 0 0 1 0 • Output: • State Diagram: lect14.ppt lect14.ppt 29 ECE U530 F’06 30 ECE U530 F’06

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.