Lecture 13: Sequential Networks Flip flops and Finite State - PowerPoint PPT Presentation

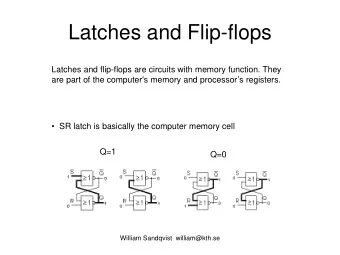

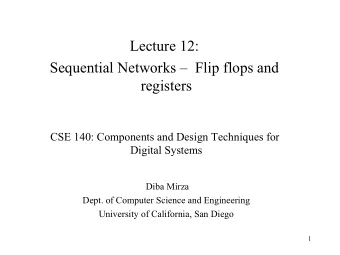

Lecture 13: Sequential Networks Flip flops and Finite State Machines CSE 140: Components and Design Techniques for Digital Systems Diba Mirza Dept. of Computer Science and Engineering University of California, San Diego 1 T Flip-Flop

Lecture 13: Sequential Networks – Flip flops and Finite State Machines CSE 140: Components and Design Techniques for Digital Systems Diba Mirza Dept. of Computer Science and Engineering University of California, San Diego 1

T Flip-Flop (Toggle) CLK State table Q T PS T 0 1 0 0 1 Q’ 1 1 0 Q(t+1) Characteristic Expression Q(t+1) = Q’(t)T(t) + Q(t)T’(t) 2

Using a JK F-F to implement a D and T F-F CLK Q x J Q’ K iClicker The above circuit behaves as which of the following flip flops? A. D F-F B. T F-F C. None of the above 3

Using a JK F-F to implement a T F-F CLK Q T J Q’ K T flip flop 4

5

6

7

8

Flip flops • Write the state-table of the following flip-flops – D – JK – T 9

Sequential Networks Y D B C X A S(t) Combinational CLK CLK RTL: Register-Transfer Level Description CLK 1. Components F-Fs 2. Specification 3. Implementation: Excitation Table 10

Specification • Combinational Logic – Truth Table – Boolean Expression – Logic Diagram (No feedback loops) • Sequential Networks: State Diagram (Memory) – State Table and Excitation Table – Characteristic Expression – Logic Diagram (FFs and feedback loops) 11

What we will learn: 1. Describe the desired behavior of a sequential circuit over time (FSMs) 2. Given the behavior of a sequential circuit, implement the circuit Describing Wall-E Wall-E is a Finite State Machine Inactive Active 12 Implementing Wall-E

Finite State Machines: Describing circuit behavior over time Symbol/ Circuit 2 bit Counter 13

Finite State Machines: Describing circuit behavior over time Output over time Symbol/ Circuit CLK time Free running 2 bit Counter Q 1 Q 0 What is the expected output of the counter over time? 14

Finite State Machines: Describing circuit behavior over time Diagram that depicts Symbol/ Circuit behavior over time 00 2 bit Counter 01 11 10 15

State: What is it ? Why do we need it? Symbol/ Circuit Behavior over time CLK 2 bit Counter t 1 time t 2 PI Q: At time t 1 , what information is needed to produce the output of the counter at the next rising edge of the clock (i.e t 2 )? A. All the outputs of the counter until t 1 B. The initial output of the counter at time t=0 C. The output of the counter at current time t 1 D. We cannot determine the output of the counter at t 2 prior to t 2 16

Implementing the 2 bit counter S 0 Current state Next State S 0 S 1 S 1 S 2 S 3 S 1 S 2 S 3 S 3 S 0 S 2 Q 1 (t) Q 0 (t) Q 1 (t+1) Q 0 (t+1) State Diagram State Table 17

State Table PI Q: Which of the following is the likely structure of the circuit realization of the Q 1 (t) Q 0 (t) Q 1 (t+1) Q 0 (t+1) counter 0 0 0 1 A. 0 1 1 0 Combinational 1 0 1 1 circuit 1 1 0 0 Circuit with no flip flops Q B. C. D Q’ Q 0 (t) Q Combinational Q Q 0 (t) circuit D Combinational Q’ Q Q 1 (t) circuit D Q’ CLK Q 1 (t) CLK Circuit with 2 flip flops 18 Circuit with one flip flop

State Table Q 1 (t) Q 0 (t) Q 1 (t+1) Q 0 (t+1) 0 0 0 1 D 0 (t) = Q 0 (t)’ D 1 (t) = Q 0 (t) Q 1 (t)’ + Q 0 (t)’ Q 1 (t) 0 1 1 0 1 0 1 1 1 1 0 0 Q B. D Q’ Q 0 (t) Combinational Q circuit D Q 1 (t) Q’ CLK Circuit with 2 flip flops 19

Q 1 (t) Q 0 (t) Q 1 (t+1) Q 0 (t+1) Q 0 (t+1) = Q 0 (t)’ 0 0 0 1 Q 1 (t+1) = Q 0 (t) Q 1 (t)’ + Q 0 (t)’ Q 1 (t) 0 1 1 0 1 0 1 1 1 1 0 0 State Table Q We store the current state using D-flip D flops so that: Q’ Q 0 (t) • Inputs to the combinational circuit Q don’t change while the next output D Q’ is being computed Q 1 (t) • The transition to the next state CLK only occurs at the rising edge of the clock Implementation of 2-bit counter 20

Generalized Model of Sequential Circuits Y X S(t) CLK 21

Let’s implement our free running 2-bit counter using T-flip flops Q T Q’ Q 0 (t) Combinational Q circuit T Q’ Q 1 (t) CLK Circuit with 2 T-flip flops Excitation table id Q 1 (t) Q 0 (t) T 1 (t) T 0 (t) Q 1 (t+1) Q 0 (t+1) 0 0 0 0 1 1 0 1 1 0 2 1 0 1 1 3 1 1 0 0 22

Let’s implement our free running 2-bit counter using T-flip flops Q T Q’ Q 0 (t) Q T Q’ Q 1 (t) CLK Circuit with 2 T-flip flops Excitation table id Q 1 (t) Q 0 (t) T 1 (t) T 0 (t) Q 1 (t+1) Q 0 (t+1) 0 0 0 0 1 0 1 1 0 1 1 1 1 0 2 1 0 0 1 1 1 3 1 1 1 1 0 0 23

Let’s implement our free running 2-bit counter using T-flip flops Q T Q’ Q 0 (t) Q T Q’ Q 1 (t) CLK Circuit with 2 T-flip flops Excitation table id Q 1 (t) Q 0 (t) T 1 (t) T 0 (t) Q 1 (t+1) Q 0 (t+1) T 0 (t) = 0 0 0 0 1 0 1 T 1 (t) = 1 0 1 1 1 1 0 2 1 0 0 1 1 1 3 1 1 1 1 0 0 24

Free running counter with T flip flops Q 0 1 Q T Q’ Q Q 1 T Q’ T 1 T 0 (t) = 1 T 1 (t) = Q 0 (t) 25

Let’s implement our free running 2-bit counter using JK-flip flops Q Q’ Q 0 (t) Combinational Q circuit Q’ Q 1 (t) CLK Circuit with 2 JK-flip flops Excitation table id Q 1 (t) Q 0 (t) J 1 (t) K 1 (t) J 0 (t) K 0 (t) Q 1 (t+1) Q 0 (t+1) 0 0 0 0 1 1 0 1 1 0 2 1 0 1 1 3 1 1 0 0 26

Let’s implement our free running 2-bit counter using JK-flip flops Q Q’ Q 0 (t) Combinational Q circuit Q’ Q 1 (t) CLK Circuit with 2 JK-flip flops Excitation table id Q 1 (t) Q 0 (t) J 1 (t) K 1 (t) J 0 (t) K 0 (t) Q 1 (t+1) Q 0 (t+1) 0 0 0 0 X 0 1 1 0 1 1 X 1 0 2 1 0 X 0 1 1 3 1 1 X 1 0 0 27

Let’s implement our free running 2-bit counter using JK-flip flops Q Q’ Q 0 (t) Combinational Q circuit Q’ Q 1 (t) CLK Circuit with 2 JK-flip flops Excitation table id Q 1 (t) Q 0 (t) J 1 (t) K 1 (t) J 0 (t) K 0 (t) Q 1 (t+1) Q 0 (t+1) 0 0 0 0 X 1 X 0 1 1 0 1 1 X X 1 1 0 2 1 0 X 0 1 X 1 1 3 1 1 X 1 X 1 0 0 28

Let’s implement our free running 2-bit counter using JK-flip flops Q Q’ J 1 (t) = Q 0 (t) Q 0 (t) Combinational K 1 (t) = Q 0 (t) Q circuit J 0 (t) = 1 Q’ Q 1 (t) K 0 (t) =1 CLK Circuit with 2 JK-flip flops Excitation table id Q 1 (t) Q 0 (t) J 1 (t) K 1 (t) J 0 (t) K 0 (t) Q 1 (t+1) Q 0 (t+1) 0 0 0 0 X 1 X 0 1 1 0 1 1 X X 1 1 0 2 1 0 X 0 1 X 1 1 3 1 1 X 1 X 1 0 0 29

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.