ECEU530 Schedule ECE U530 Classes on November 6 and 8 will be in - PDF document

ECEU530 Schedule ECE U530 Classes on November 6 and 8 will be in 429 Dana Digital Hardware Synthesis Homework 5 due Wednesday, November 8 Write the Datapath for the calculator from ECEU323 in VHDL Prof. Miriam Leeser Use the

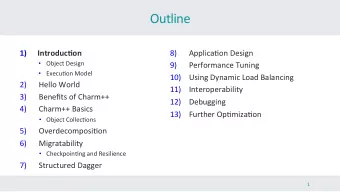

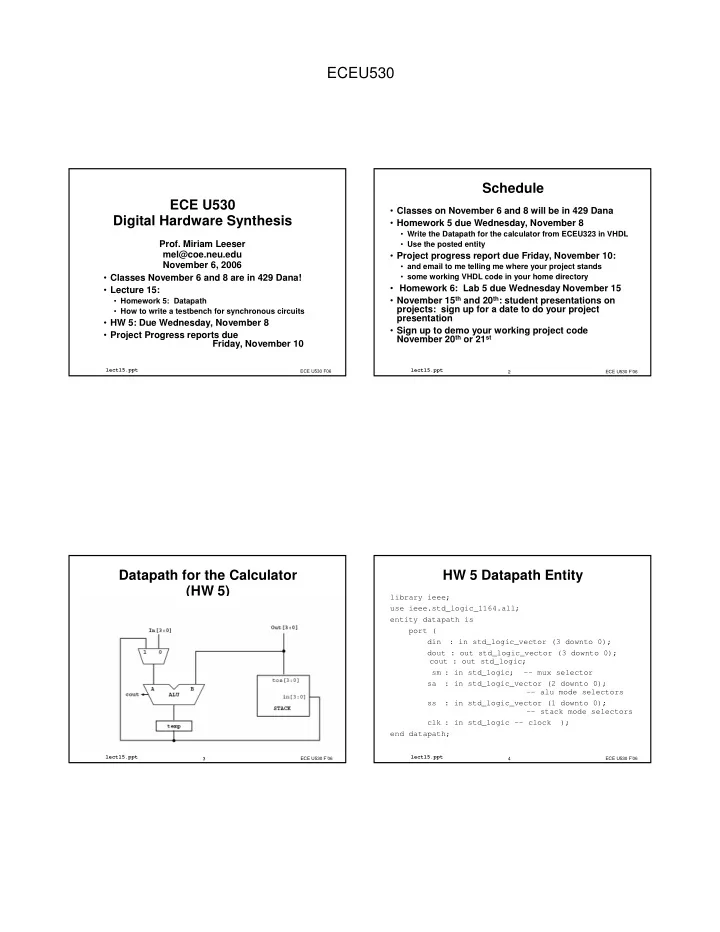

ECEU530 Schedule ECE U530 • Classes on November 6 and 8 will be in 429 Dana Digital Hardware Synthesis • Homework 5 due Wednesday, November 8 • Write the Datapath for the calculator from ECEU323 in VHDL Prof. Miriam Leeser • Use the posted entity mel@coe.neu.edu • Project progress report due Friday, November 10: November 6, 2006 • and email to me telling me where your project stands • Classes November 6 and 8 are in 429 Dana! • some working VHDL code in your home directory • Homework 6: Lab 5 due Wednesday November 15 • Lecture 15: • November 15 th and 20 th : student presentations on • Homework 5: Datapath projects: sign up for a date to do your project • How to write a testbench for synchronous circuits presentation • HW 5: Due Wednesday, November 8 • Sign up to demo your working project code • Project Progress reports due November 20 th or 21 st Friday, November 10 lect15.ppt ECE U530 F06 lect15.ppt 2 ECE U530 F’06 Datapath for the Calculator HW 5 Datapath Entity (HW 5) library ieee; use ieee.std_logic_1164.all; entity datapath is port ( din : in std_logic_vector (3 downto 0); dout : out std_logic_vector (3 downto 0); cout : out std_logic; sm : in std_logic; -- mux selector sa : in std_logic_vector (2 downto 0); -- alu mode selectors ss : in std_logic_vector (1 downto 0); -- stack mode selectors clk : in std_logic -- clock ); end datapath; lect15.ppt lect15.ppt 3 ECE U530 F’06 4 ECE U530 F’06

ECEU530 Stack for Datapath Implement the Stack: entity stack is Stack Function Stack select port( hold 0, 1 clk, reset : in std_logic; -- clock push 2 ss : in std_logic_vector (1 downto 0); din : in std_logic_vector (4 downto 0); pop 3 tos : out std_logic_vector (4 downto 0) ); end stack; • In lab, used shift registers to implement the stack • In VHDL, use behavioral code to implement the stack architecture behavioral of stack is • How ? begin • Hint: Create internal state for the “stack” -- <<enter your statements here>> • Looks like a simple state machine end behavioral; • Output is simply TOS • Note: Stack has an asynchronous reset lect15.ppt lect15.ppt 5 ECE U530 F’06 6 ECE U530 F’06 Stack Shift Register entity shift is ARCHITECTURE behavioral of stack IS port(Clk, SI : in std_logic; SUBTYPE five_bit is std_logic_vector (4 SO : out std_logic); downto 0); end shift; architecture archi of shift is TYPE four_array IS ARRAY (3 downto 0) OF signal next_state, state: five_bit; std_logic_vector(3 downto 0); SIGNAL stk, next_stack : four_array; begin process begin begin -- process for updating stack state next_state <= state(2 downto 0) & SI; wait until (Clk'event and Clk = '1'); state <= next_state; • Why do you need a new stack? end process; SO <= state(3); end archi; lect15.ppt lect15.ppt 7 ECE U530 F’06 8 ECE U530 F’06

ECEU530 Testbench Design Simple UUTs • Combinational circuits are easy to test • Inputs can come in any order • Already seen basics of how to write one • Outputs are only dependent on current input, not previous (Lecture 7) inputs • Libraries, Entity, Architecture • Usually we can test combinational circuits • Instance of Unit Under Test (UUT) exhaustively (all possible combinations of inputs) • Process to control clock � ��� ��� ��� loops are often useful here ��� • Today: More important concepts • Which input combinations should I try? • Self-checking testbenches lect15.ppt lect15.ppt 9 ECE U530 F’06 10 ECE U530 F’06 Simple UUT: AOI Simple UUT: Testbench (1) �������������� ������������� ����������������������������� ��� ������������������������ �������������� ��� �������������������&������** ���'�����������'����� ������������� ���������� ���������� � ! " #$��������������� ��������� �� �$���������������%�� ��� ��� ��������� ���&���������������� �� �� ���&�����������&�'�������� ��� ��� ��+���������� ������ ������ � � � �$�������������� ��()�������������!%�����"�����#%%�� �$���������������%� ������&�'������ ������+������� lect15.ppt lect15.ppt 11 ECE U530 F’06 12 ECE U530 F’06

ECEU530 Simple UUT: Testbench (2) What does it do? ���������� $�����������'������, ������ -%� ��� cycles through 0(0000) to 15(1111) � ��� ��� ��� ���������$����������� � � � � are assigned to bits of ��� � � � � � � � � � � � � � ��� ��� ��� ����� ���$ ��� �����+�����).����,% ��).����/% � • This covers all possible inputs to the circuit �).�����% ��).����-% ��).��%� ��������&$����������� • Coverage is an important term when testing any '����������$���������$)�-� ����� circuit ���������-�����0����� • “How much functionality did I actually test?” ��� () ���'�����������'������� �%� ���������/-���� ��������� ������������ �������&��������� lect15.ppt lect15.ppt 13 ECE U530 F’06 14 ECE U530 F’06 How do I know it works? (1) How do I know it works? (2) • Inspection : Run it in Modelsim and see if the output is what you expect • Have to figure out all the correct outputs yourself • Golden Standard : Compare the output to another circuit which implements the same function • There are only 4 inputs (16 possible values) here, so this is pretty easy and doable • Ex.: Behavioral model vs. Structural model • What if I have a lot of inputs, or a more complex circuit? • Instantiate a “standard” circuit alongside the UUT, connected to the same inputs • If the outputs are the same, the UUT works • Requires a circuit that already works! lect15.ppt lect15.ppt 15 ECE U530 F’06 16 ECE U530 F’06

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.