Introduction Embedded system architecture Electronic systems - PDF document

Outline HDL and Embedded Systems Design SystemC and VHDL Platform Based Design Transaction Level Modeling

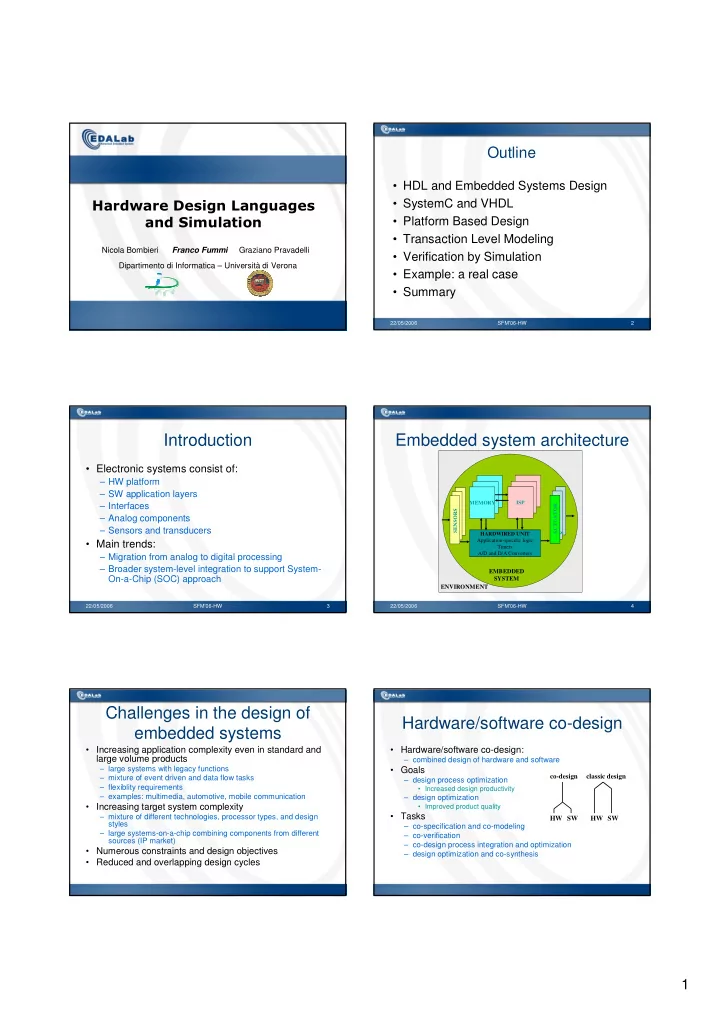

Outline • HDL and Embedded Systems Design ������������������������� • SystemC and VHDL �������������� • Platform Based Design • Transaction Level Modeling Nicola Bombieri Graziano Pravadelli Franco Fummi • Verification by Simulation Dipartimento di Informatica – Università di Verona • Example: a real case • Summary 22/05/2006 SFM'06-HW 2 Introduction Embedded system architecture • Electronic systems consist of: – HW platform – SW application layers MEMORY ISP – Interfaces ACTUATOR SENSORS – Analog components – Sensors and transducers HARDWIRED UNIT S Application-specific logic • Main trends: Timers A/D and D/A Converters – Migration from analog to digital processing – Broader system-level integration to support System- EMBEDDED On-a-Chip (SOC) approach SYSTEM ENVIRONMENT 22/05/2006 SFM'06-HW 3 22/05/2006 SFM'06-HW 4 Challenges in the design of Hardware/software co-design embedded systems • Increasing application complexity even in standard and • Hardware/software co-design: large volume products – combined design of hardware and software – large systems with legacy functions • Goals co-design classic design – mixture of event driven and data flow tasks – design process optimization – flexiblity requirements • Increased design productivity – examples: multimedia, automotive, mobile communication – design optimization • Increasing target system complexity • Improved product quality • Tasks – mixture of different technologies, processor types, and design HW SW HW SW styles – co-specification and co-modeling – large systems-on-a-chip combining components from different – co-verification sources (IP market) – co-design process integration and optimization • Numerous constraints and design objectives – design optimization and co-synthesis • Reduced and overlapping design cycles 1

Co-design of embedded Co-design advantages systems • Explore different design alternatives in the • Design of dedicated computing and control architectural design space systems • Tune HW to SW and vice-versa • Embedded controllers • Reduce the system design time – On-line control of manufacturing process • Support coherent design specification at the – Robots guidance and control system-level – Aircraft, automobile and ship control • Facilitate the re-use of HW and SW parts • Data processing and communication systems • Provide integrated environment for the synthesis – Telecom and validation of HW and SW components – Radio-navigation 22/05/2006 SFM'06-HW 7 22/05/2006 SFM'06-HW 8 Co-design of embedded HDL motivation systems • Design of dedicated HW parts – Different design styles: • Co-processors, embedded cores, ASIPs, ... Design – Widely varying design scale complexity • Design of dedicated SW parts – Special-purpose operating systems Time to Manufacturing Market costs – Drivers of peripheral devices 22/05/2006 SFM'06-HW 9 22/05/2006 SFM'06-HW 10 HDL motivation HDL motivation Does it really work? Classical design flow Functional Architect. SW Sys Sys Design Fab. Breadboard specif. specif develop. integration validation �������� ������������ ��������������� Functional specifications failures? Performance expectations missing? ������ Main reason: ����������� ����������� lacking of a concretely usable view ����������� of the complete system before the tape-out phase! Re-spins! ������������� ���� 22/05/2006 SFM'06-HW 11 22/05/2006 SFM'06-HW 12 2

State of the practice State of the practice • Co-simulation as a support of design (process) • “Executable” co-specification used as a basis for integration system validation – extension of simulation techniques to combined simulation of • Virtual prototyping hardware and software components – allows permanent control of hardware and software component – simulation based validation consistency – many commercial examples for different applications – supports early validation of reused component integration Statemate (i-Logix), MatrixX (ISI), MATLAB • Integration validation more costly with increasing level of (MathWorks) detail – RASSP program (DARPA) – current focus on co-simulation for lower levels of a design • Rapid prototyping with “hardware-in-the-loop” – simulation with models of specific processors, memories, busses, ... – hardware supported system emulation Þ real – reduction of accuracy mainly to improve simulation performance environment – examples: Mentor Seamless CVS, Viewlogic Eagle – often custom design State of the practice Specification languages • Executable co-specification problems • Different communities: – combination of domain specific languages – VLSI system design VHDL, VERILOG, Specchart, … and semantics – DSP COSSAP, SPW, … – integration of reused functions and – Continuous design MATLAB, MATRIXX, … components in abstract model – Synchronous system design Esterel, Lustre, Statechart – inclusion of non-functional constraints – Classical programming C, C++, Java, … – Functional and algebraic VDM, Z, B, Funmath, … – Structured design methods SART, OMT, … 22/05/2006 SFM'06-HW 15 22/05/2006 SFM'06-HW 16 Concepts for system level specification Example of specification Language • CONCURRENCY • SDL – different levels (bit, operation, statement, process, system) – well-suited for control-intensive, real-time – two types: data-driven, control-driven • HIERARCHY systems – needed for structured design methodologies – flow chart FSM, both graphics and text – Two types: behavior, structure – abstract data types • COMMUNICATION – data exchange between concurrent subsystems – dynamic process creation – two types: message passing, shared memory – synchronization via blocking, RPC • SYNCHRONIZATION – two models: synchronous, asynchronous – can monitor performance constraints 22/05/2006 SFM'06-HW 17 22/05/2006 SFM'06-HW 18 3

Simulation and debugging Example of specification Language requirements • StateCharts, SpecCharts • Embedded controllers: – graphical FSM of states and transitions – ASICs plus SW running on a processor – addition of hierarchical states for modeling complex – VHDL or Verilog plus C programs reactive behaviors – Weakly heterogeneous systems – SpecCharts adds • Embedded data processing and communication • behavioral completion • exceptions systems – may attach VHDL code to states and transitions arcs – ASICs plus SW running on a processor or ASIP – extended with arithmetics – Environmental modeling (e.g. telephone lines) – Easy to use for control-dominated systems – Strongly heterogeneous systems 22/05/2006 SFM'06-HW 19 22/05/2006 SFM'06-HW 20 Co-simulation Co-simulation • Desired features: • Simulate at the same time both hardware – Level of timing accuracy and software – Speed of simulation runs – Visibility of internal states • Two conflicting requirements: • Potential problems: – execute the software as fast as possible – Meaningful results are obtained with large SW – keep hardware and software simulations programs – Model availability synchronized so they interact as they will in – Strong heterogeneity requires specialized the target system. environment 22/05/2006 SFM'06-HW 21 22/05/2006 SFM'06-HW 22 Co-simulation paradigms Co-simulation paradigms • Weakly heterogeneous systems • Homogeneous modeling: – a) HDL simulators with processor model – HW models in HDL – b) Compiled SW – Processor model in HDL – c) HW emulation – SW in assembly code • Strongly heterogeneous systems • Usage of HDL simulator for the whole system – Require specialized simulation environments including the processor model (e.g. Ptolemy) – Communication mechanisms among domains • Simple method but quite inefficient and their corresponding schedulers 22/05/2006 SFM'06-HW 23 22/05/2006 SFM'06-HW 24 4

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.