Lecture 11 Logistics Midterm 1: ave 88, median 90, std 9. good - PDF document

Lecture 11 Logistics Midterm 1: ave 88, median 90, std 9. good job! HW4 due on Wednesday HW4 due on Wednesday Last lecture Multi-level logic Timing diagrams Today Time/space trade offs: Parallel prefix trees

Lecture 11 � Logistics � Midterm 1: ave 88, median 90, std 9. good job! � HW4 due on Wednesday � HW4 due on Wednesday � Last lecture � Multi-level logic � Timing diagrams � Today � Time/space trade offs: Parallel prefix trees � Adders Add � Ripple-carry � Carry-lookahead � Carry-select � The conclusion of combinational logic!!! CSE370, Lecture 12 11 1 Arithmetic circuits � General-purpose building blocks � Critical components in processor data paths � Adders � Adders � Multipliers � ALUs � Perform most computer instructions � Time ↔ space tradeoff � Fast circuits usually require more logic CSE370, Lecture 12 11 2

What do we mean by time/speed tradeoff?: Linear chains vs. trees � Lets say we want to implement an 8-input OR function with only 2-input gates Gates: 7 Max delay: 7 CSE370, Lecture 12 11 3 Linear chains vs. trees � Now consider the tree version G t Gates: 7 7 Max delay: 3 CSE370, Lecture 12 11 4

And now we change the problem slightly � Build a circuit that takes 8 single bit inputs and calculates the OR of the first 2, the OR of the first 3, the OR of the first 4, and so on, up to the OR of all 8 th OR f th fi t 4 d t th OR f ll 8 Gates: 7 Max delay: 7 CSE370, Lecture 12 11 5 The tree version of the prefix circuit Gates: 12 Max delay: 3 CSE370, Lecture 12 11 6

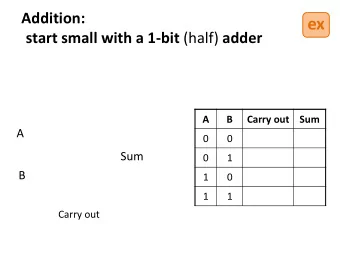

Binary half adder � 1-bit half adder A B S C out � Computes sum, carry-out 0 0 0 0 � No carry in � No carry-in 0 0 1 1 1 1 0 0 1 0 1 0 � Sum = A'B + AB' = A xor B 1 1 0 1 � Cout = AB XOR A Sum B 34 Sum A Half Adder B Cout AND2 A Cout B 35 CSE370, Lecture 12 11 7 Binary full adder � 1-bit full adder A B C in S C out 0 0 0 0 0 � Computes sum, carry-out 0 0 1 1 0 � Carry in allows cascaded adders � Carry-in allows cascaded adders 0 1 0 1 0 � Sum = Cin xor A xor B 0 1 1 0 1 � Cout = ACin + BCin + AB 1 0 0 1 0 1 0 1 0 1 XOR 1 1 0 0 1 A XOR B 32 1 1 1 1 1 Sum Cin 33 AND2 B Cin 11 A AND2 OR3 Sum Full A B Cout Adder Cin Cout 12 14 Cin AND2 A B 13 CSE370, Lecture 12 11 8

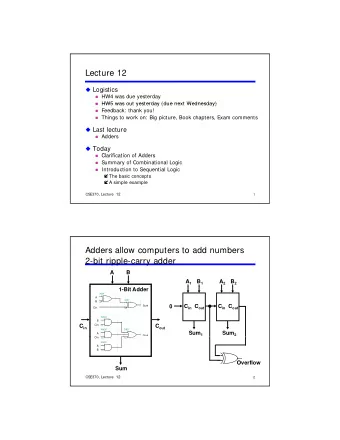

Full adder: Alternative implementation � Multilevel logic A B C in S C out C out � Slower 0 0 0 0 0 0 0 0 0 0 1 1 1 1 0 0 0 0 � Fewer gates � Fewer gates 0 1 0 1 0 0 � 2 XORs, 2 ANDs, 1 OR 0 1 1 0 1 1 1 0 0 1 0 0 Sum = (A ⊕ B) ⊕ Cin 1 0 1 0 1 1 1 1 0 0 1 1 Cout = ACin + BCin + AB 1 1 1 1 1 1 = (A ⊕ B)Cin + AB Half Adder Half Adder A xor B A xor B xor Cin Sum A Sum Sum AB Cout (A xor B)Cin B Cout Cin Cout CSE370, Lecture 12 11 9 2-bit ripple-carry adder A B A 1 B 1 A 2 B 2 1-Bit Adder XOR A XOR B 32 C in C out C in C out Sum 0 Cin 33 AND2 B C in Cin C out 11 AND2 OR3 Sum 1 Sum 2 A Cout Cin Ci 12 14 AND2 A B 13 Overflow Sum CSE370, Lecture 12 11 10

4-bit ripple-carry adder/subtractor � Circuit adds or subtracts � 2s complement: A – B = A + (–B) = A + B' + 1 A2 B2B2' A1 B1B1' A0 B0B0' A3 B3B3' Sel Sel Sel Sel 0 1 0 1 0 1 0 1 A B A B A B A B 0 � Add Cout Cin Cout Cin Cout Cin Cout Cin 1 � Subtract 1 � Subtract Sum Sum Sum Sum S3 S2 S1 S0 Overflow CSE370, Lecture 12 11 11 Problem: Ripple-carry delay � Carry propagation limits adder speed Cin XOR XOR @0 A S0 @2 XOR A0 @0 B 32 B0 C1 @2 Sum @2N Cin 33 @2N+1 A1 S1 @3 AND2 @0 B B1 C2 @4 @2N Cin 11 AND2 OR3 @2N 2 @2N+2 A2 A2 S2 @5 S2 @5 @0 @0 A A B2 C3 @6 Cout @2N Cin 12 14 AND2 @0 A A3 S3 @7 B3 Cout @8 @0 B 13 C out takes two gate delays C in arrives late CSE370, Lecture 12 11 12

Ripple-carry adder timing diagram � Critical delay � Carry propagation � 1111 + 0001 = 10000 is worst case � 1111 + 0001 = 10000 is worst case S0, C1 Valid S1, C2 Valid S2, C3 Valid S3, C4 Valid T0 T2 T4 T6 T8 CSE370, Lecture 12 11 13 One solution: Carry lookahead logic Cin S0 @2 A0 B0 � Compute all the carries in parallel C1 @3 � Derive carries from the data inputs S1 @4 A1 � Not from intermediate carries B1 � Use two-level logic C2 @3 � Compute all sums in parallel S2 @4 A2 B2 C3 @3 C3 @3 S3 @4 A3 B3 C4 @3 C4 @3 CSE370, Lecture 12 11 14

Full adder: getting Pi an Gi Half Adder Half Adder A xor B A xor B xor Cin A Sum Sum AB AB Cout Cin(A xor B) Cin(A xor B) B B Cout Cin Cout XOR XOR Ai Pi Si Bi 36 38 AND2 AND2 AND2 AND2 Ai Gi Bi 37 39 OR2 Ci Ci+ 1 40 CSE370, Lecture 12 11 15 Carry-lookahead logic � Carry generate: G i = A i B i � Generate carry when A = B = 1 � Carry propagate: P i = A i xor B i � Propagate carry-in to carry-out when (A xor B) = 1 � Sum and Cout in terms of generate/propagate: � S i = A i xor B i xor C i = P i xor C i i i � C i+ 1 = A i B i + C i (A i xor B i ) = G i + C i P i CSE370, Lecture 12 11 16

Carry-lookahead logic (cont’d) � Re-express the carry logic in terms of G and P C 1 = G 0 + P 0 C 0 C = G + P C = G + P G + P P C C 2 = G 1 + P 1 C 1 = G 1 + P 1 G 0 + P 1 P 0 C 0 C 3 = G 2 + P 2 C 2 = G 2 + P 2 G 1 + P 2 P 1 G 0 + P 2 P 1 P 0 C 0 C 4 = G 3 + P 3 C 3 = G 3 + P 3 G 2 + P 3 P 2 G 1 + P 3 P 2 P 1 G 0 + P 3 P 2 P 1 P 0 C 0 � Implement each carry equation with two-level logic � Derive intermediate results directly from inputs � Rather than from carries � Allows "sum" computations to proceed in parallel CSE370, Lecture 12 11 17 Implementing the carry-lookahead logic Ai Logic complexity Pi @ 1 gate delay Bi increases with increases with Si @ 2 gate delays Ci adder size Gi @ 1 gate delay C0 C0 P0 C0 P0 C1 P1 P0 P2 G0 P1 P3 P2 G0 G0 P1 P1 C0 C0 P1 P1 P2 P0 P2 P1 P3 C3 G1 G1 G0 C2 P2 P1 P2 P3 C4 G2 G2 G1 P3 G3 CSE370, Lecture 12 11 18

Cascaded carry-lookahead adder � 4 four-bit adders with internal carry lookahead � Second level lookahead extends adder to 16 bits 4 4 4 4 4 4 4 4 A[15-12] B[15-12] A[11-8] B[11-8] A[7-4] B[7-4] A[3-0] B[3-0] C12 C8 C4 C0 4-bit Adder 4-bit Adder 4-bit Adder 4-bit Adder @0 P G P G P G P G 4 4 4 4 S[15-12] S[11-8] S[7-4] S[3-0] @8 @8 @7 @4 @3 @2 @2 @3 @2 @3 @2 @3 @5 @5 @4 P3 G3 P2 G2 C2 P1 G1 C1 P0 G0 C3 C16 C0 C4 C0 Lookahead Carry Unit @4 @0 P3-0 G3-0 @3 @5 CSE370, Lecture 12 11 19 Carry lookahead logic summary � Compute all the carries in parallel Cin � Derive carries from the data inputs S0 @2 � Not from intermediate carries � Not from intermediate carries A0 B0 � Use two-level logic C1 @3 � Compute all sums in parallel S1 @4 A1 � Cascade simple adders to make B1 C2 @3 large adders S2 @4 A2 � Speed improvement B2 � 16-bit ripple-carry: ~ 32 gate delays 16 bit i l 32 t d l C3 @3 C3 @3 S3 @4 � 16-bit carry-lookahead: ~ 8 gate delays A3 B3 � Issues C4 @3 C4 @3 � Complex combinational logic CSE370, Lecture 12 11 20

Another solution: Carry-select adder � Redundant hardware speeds carry calculation � Compute two high-order sums while waiting for carry-in (C4) � Select correct high-order sum after receiving C4 � Select correct high-order sum after receiving C4 C8 0 4-bit adder adder [7:4] low C8 1 4-bit adder adder [7:4] high 1 0 1 0 1 0 1 0 1 0 C0 C4 4-Bit Adder five [3:0] 2:1 muxes C8 S7 S6 S5 S4 S3 S2 S1 S0 CSE370, Lecture 12 11 21 Scaling of carry-select adders � Size: roughly twice the size of a ripple-carry Delay: delay through a 4-bit ripple-carry plus the multiplexor path highlighted in blue (3 2-1 lti l th hi hli ht d i bl (3 2 1 multiplexors, in this example) CSE370, Lecture 12 11 22

We've finished combinational logic... � What you should know � Twos complement arithmetic � Truth tables � Truth tables � Basic logic gates � Schematic diagrams � Timing diagrams � Minterm and maxterm expansions (canonical, minimized) � de Morgan's theorem � AND/OR to NAND/NOR logic conversion � K-maps, logic minimization, don't cares � K maps, logic minimization, don t cares � Multiplexers/demultiplexers � PLAs/PALs � ROMs � Adders CSE370, Lecture 12 11 23

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.