Learning Outcomes I understand what gates are used to design half - PowerPoint PPT Presentation

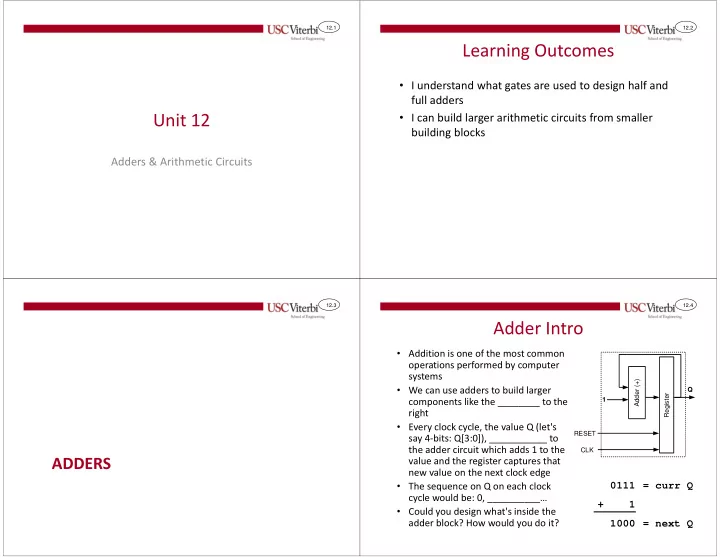

12.1 12.2 Learning Outcomes I understand what gates are used to design half and full adders Unit 12 I can build larger arithmetic circuits from smaller building blocks Adders & Arithmetic Circuits 12.3 12.4 Adder Intro

12.1 12.2 Learning Outcomes • I understand what gates are used to design half and full adders Unit 12 • I can build larger arithmetic circuits from smaller building blocks Adders & Arithmetic Circuits 12.3 12.4 Adder Intro • Addition is one of the most common operations performed by computer systems Adder (+) • We can use adders to build larger Q Register components like the ________ to the 1 right • Every clock cycle, the value Q (let's RESET say 4-bits: Q[3:0]), ___________ to the adder circuit which adds 1 to the CLK ADDERS value and the register captures that new value on the next clock edge • The sequence on Q on each clock 0111 = curr Q cycle would be: 0, __________… + 1 • Could you design what's inside the adder block? How would you do it? 1000 = next Q

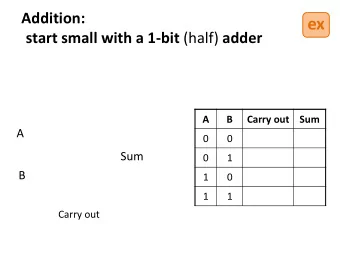

12.5 12.6 Adder Intro Adder Intro • What if we had to add ______ • Idea : Build a circuit that performs two 4-bit numbers, X[3:0] and _____ column of addition and then Y[3:0]? Do we have the use ______________ of those 0110 = X techniques to build such a circuits to perform the overall 4-bit 0110 = X circuit directly? addition + 0111 = Y + 0111 = Y • _______________ • Let's start by designing a circuit that 1101 1101 adds 2-bits: X and Y that are in the – ________________________ same column of addition – ________________________ X Y Half C out Adder S 12.7 12.8 Addition – Half Adders Problem With Half Adders C out • We’d like to use one • Addition is done in columns 110 110 – Inputs are a bit from X and bit from Y, both adder circuit for each 0110 = X from the same column 0110 = X column of addition – Outputs are the Sum Bit and Carry-Out (C out ) + 0111 = Y + 0111 = Y • Design a Half-Adder (HA) circuit that • Problem: takes in X and Y and outputs S and C out 1101 1101 – No place for _________ Sum • Use the truth table to find the gate of half adder to connect 0 1 implementation to the ___________ 0 1 1 1 X Y • Solution X Y X Y X Y C out S Half C out 0 Half Half – Redesign adder circuit to C out Adder C out 0 0 0 0 0 1 Adder Adder S include an _________ 0 1 0 1 S S input for the ________ 1 0 0 1 1 1 0 1 1 1 0

12.9 12.10 Addition – Full Adders Addition – Full Adders C out C in • Find the minimal 2-level implementations for Cout and S… • Add a Carry-In input(C in ) 110 • New circuit is called a 0110 = X X Y C in C out S Full Adder (FA) + 0111 = Y 0 0 0 0 0 1101 0 0 1 0 1 X Y C in C out S 0 1 0 0 1 0 1 0 1 1 1 0 0 0 0 0 0 1 0 0 0 1 X Y 0 0 1 0 1 1 0 1 1 0 0 1 0 0 1 Full 1 1 0 1 0 1 C out C in 0 Adder 0 1 1 1 0 1 1 1 1 1 1 0 0 0 1 S 1 0 1 1 0 Recall a 2-input XOR can be 0 1 1 0 1 0 written in SOP as F = x'y + xy' 1 1 1 1 1 12.11 12.12 XOR and XNOR Gates Full Adder Logic • Recall a 2-input XOR can be written in SOP as F = x'y + xy' • S = ____________________ • A 2-input XNOR can be written in SOP as F = x'y' + xy – Recall: XOR is defined as true when ODD number of inputs are X true…exactly when the sum bit X F F Y Y should be 1 Z Z True if an _____ # of inputs are true True if an _____ # of inputs are true • Cout = ___________________ X Y Z F XY X Y Z F XY 00 01 11 10 – Carry when sum is 2 or more (i.e. Z 00 01 11 10 Z 0 0 0 0 0 0 0 1 0 2 6 4 0 2 6 4 0 1 0 1 when at least 2 inputs are 1) 0 0 1 1 0 0 1 0 0 1 0 1 0 0 0 1 0 1 0 1 0 0 1 3 7 5 – Circuit is just checking all 1 3 7 5 0 1 1 0 0 1 1 1 1 0 1 0 1 0 1 0 1 1 1 0 0 1 1 0 0 0 combinations of 2 inputs 1 0 1 0 1 0 1 1 F = X xor Y xor Z F = X xor Y xor Z 1 1 0 0 1 1 0 1 1 1 1 1 1 1 1 0 A checkerboard K-map corresponds to either an XOR or XNOR

12.13 12.14 Addition – Full Adders (1) Addition – Full Adders (2) • Use 1 Full Adder for each column of addition • Connect bits of top number to X inputs 0110 0110 + 0111 + 0111 0 1 1 0 X Y X Y X Y X Y X Y X Y X Y X Y Full Full Full Full Full Full Full Full C out C in C out C in C out C in C out C in C out C in C out C in C out C in C out C in Adder Adder Adder Adder Adder Adder Adder Adder S S S S S S S S 12.15 12.16 Addition – Full Adders (3) Addition – Full Adders (4) • Connect bits of bottom number to Y inputs • Be sure to connect first C in to 0 0110 = X 0110 = X + 0111 = Y + 0111 = Y 0 0 1 1 1 1 0 1 0 0 1 1 1 1 0 1 X Y X Y X Y X Y X Y X Y X Y X Y Full Full Full Full Full Full Full Full 0 C out C in C out C in C out C in C out C in C out C in C out C in C out C in C out C in Adder Adder Adder Adder Adder Adder Adder Adder S S S S S S S S

12.17 12.18 Addition – Full Adders (5) Addition – Full Adders (6) • Use 1 Full Adder for each column of addition • Use 1 Full Adder for each column of addition 00 100 0110 = X 0110 = X + 0111 = Y + 0111 = Y 1 01 0 0 1 1 1 1 0 1 0 0 1 1 1 1 0 1 X Y X Y X Y X Y X Y X Y X Y X Y 0 1 0 Full Full Full Full Full Full Full Full C out C in C out C in C out C in C out C in 0 C out C in C out C in C out C in C out C in 0 Adder Adder Adder Adder Adder Adder Adder Adder S S S S S S S S 1 0 1 12.19 12.20 Addition – Full Adders (7) Addition – Full Adders (8) • Use 1 Full Adder for each column of addition • Use 1 Full Adder for each column of addition 1100 01100 0110 = X 0110 = X + 0111 = Y + 0111 = Y 101 1101 0 0 1 1 1 1 0 1 0 0 1 1 1 1 0 1 X Y X Y X Y X Y X Y X Y X Y X Y 1 1 0 0 1 1 0 Full Full Full Full Full Full Full Full 0 0 C out C in C out C in C out C in C out C in C out C in C out C in C out C in C out C in Adder Adder Adder Adder Adder Adder Adder Adder S S S S S S S S 1 0 1 1 1 0 1

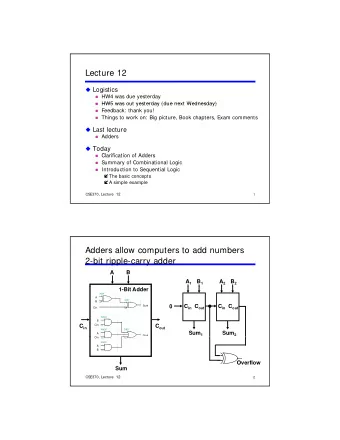

12.21 12.22 4-bit Adders Performing Subtraction • We can create a component to perform 4-bit addition • To subtract 0101 = X - 0011 = Y – ________ 0010 A 3 A 2 A 1 A 0 = A – ________ + B 3 B 2 B 1 B 0 = B S 4 S 3 S 2 S 1 S 0 = S A 3 B 3 A 2 B 2 A 1 B 1 A 0 B 0 X Y X Y X Y X Y C out C in Full Full Full Full 4-bit Adder C out C in C out C in C out C in C out C in Adder Adder Adder Adder S 3 S 2 S 1 S 0 S S S S 12.23 12.24 Device vs. System Labels • When using hierarchy (i.e. building blocks) to design a circuit be sure to show both device and system labels – Device Labels: Signal names used __________ the block • Placeholder names the designer/manufacturer of the block uses to indicate which input/output is which to the outside user (Names may vary; read the manual) – System labels: Signal names used __________ the block • ______________ signals from the circuit being built and given by the designer • Can have the same name as the device label if such a signal name exists at the outside level Analogy: Formal and Actual parameters EXERCISES 1. a and b are like device labels and X3 X2 X1 X0 Y3 Y2 Y1 Y0 indicate the names used inside a block. Device Labels: 2. x and y are like system labels and Indicate which represent the actual values to be used. input/output is which inside int div(int a, int b) { int s = a/b; the bock. 4-bit Adder 0 (GND) return s; } int main() System Labels: { Actual signals from int x=10, y=2; the circuit being built int s = div(x,y); S3 S2 S1 S0 }

12.25 12.26 Building an 8-bit Adder Adding Many Bits • Use (2) 4-bit adders to build an 8-bit adder to add X=X[7:0] • You know that an FA and Y= Y[7:0] and produce a sum, S=[7:0] and a carry-out, C8. adds X + Y + Ci – Label the inputs and outputs and make appropriate connections • Use FA and/or HA components to add 4 X Y individual bits: Full C out C in A + B + C + D Adder S 12.27 12.28 Adding 3 Numbers Mapping Algorithms to HW • Wherever an • Add X[3:0] + Y[3:0] + Z[3:0] to produce if..then..else B[3:0] 4-bit Adder F[?:0] using the Adder statement is used 0101 Circuit I 0 Z[3:0] adders shown plus usually requires a Y any FA and HA A[3:0] Adder I 1 S mux Circuit components you 0010 need – if(A[3:0] > B[3:0]) A[3:0] Comparison • Z = A+2 Circuit A>B B[3:0] – else 4-bit Adder • Z = B+5

12.29 12.30 Mapping Algorithms to HW Adder / Subtractor • Wherever an • If sub == 1 B[3:0] I 0 if..then..else – Z = X[3:0]-Y[3:0] Y • Else statement is used A[3:0] I 1 S Adder – Z = X[3:0]+Y[3:0] usually requires a Circuit 0101 Z[3:0] I 0 mux Y 0010 I 1 – if(A[3:0] > B[3:0]) S • Z = A+2 A>B – else A[3:0] Comparison • Z = B+5 Circuit B[3:0] 12.31 12.32 Adder / Subtractor Another Example • Go back and optimize the muxes by determining • Design a circuit that takes a 4-bit binary what logic function they are actually performing SUB 4-bit Adder Input number, X, and two control signals, A5 and M1 • If sub == 1 and produces a 4-bit result, Z, such that: A5 M1 B3 B2 B1 B0 0 0 – Z = X[3:0]-Y[3:0] • Z = X + 5, when A5,M1 = 1,0 0 1 • Else • Z = X – 1, when A5,M1 = 0,1 1 0 • Z = X, when A5,M1 = 0,0 – Z = X[3:0]+Y[3:0] 1 1 d d d d SUB Yi Bi 0 0 0 1 1 0 1 1 SUB

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.