Previous Lecture Todays Lecture Slides for Lecture 30 ENEL 353: - PowerPoint PPT Presentation

ENEL 353 F13 Section 02 Slides for Lecture 30 slide 2/21 ENEL 353 F13 Section 02 Slides for Lecture 30 slide 3/21 Previous Lecture Todays Lecture Slides for Lecture 30 ENEL 353: Digital Circuits Fall 2013 Term Completion of an FSM

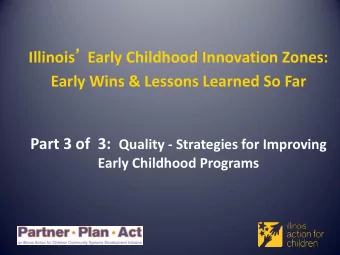

ENEL 353 F13 Section 02 Slides for Lecture 30 slide 2/21 ENEL 353 F13 Section 02 Slides for Lecture 30 slide 3/21 Previous Lecture Today’s Lecture Slides for Lecture 30 ENEL 353: Digital Circuits — Fall 2013 Term Completion of an FSM reverse-engineering example. Completion of next-state and output logic design for the Introduction to timing of sequential logic. Steve Norman, PhD, PEng Mealy FSM solution to example sequence detection problem. Timing parameters for DFFs, and implications of those Factoring of FSMs. Electrical & Computer Engineering parameters for timing of synchronous sequential circuits. Schulich School of Engineering Reverse-engineering an FSM: Given an FSM circuit, finding a University of Calgary word description of what the FSM does. Related reading in Harris & Harris: Sections 3.4.5–3.4.6, 20 November, 2013 Section 3.5 to the end of 3.5.2. slide 5/21 slide 6/21 slide 4/21 ENEL 353 F13 Section 02 Slides for Lecture 30 ENEL 353 F13 Section 02 Slides for Lecture 30 (This picks up from where the S 2 S 1 S 0 A S ′ 2 S ′ 1 S ′ Completion of the example FSM derivation Introduction to timing of sequential logic 0 previous lecture ended.) The next 0 0 0 0 0 0 0 problem three steps are: 0 0 0 1 0 0 1 For a synchronous sequential circuit design, some of the major ◮ Use next-state and output 0 0 1 0 0 0 1 timing concerns are . . . equations to create 0 0 1 1 0 1 0 ◮ What are sufficient conditions on the D input of a DFF to next-state and output tables. 0 1 0 0 0 1 0 0 1 0 1 0 1 1 The final three steps are: ensure reliable operations of the DFF? (This is called the (The next-state table is 0 1 1 0 0 1 1 ◮ Rewrite next-state and output tables with state names. “dynamic discipline”.) ready for us on this slide, to 0 1 1 1 1 0 0 ◮ Given timing specifications for DFFs and a desired clock save us all some boredom.) ◮ Draw state transition diagram. 1 0 0 0 1 0 0 period T C , what do those things say about maximum ◮ Reduce the next-state table ◮ State in words what the FSM does. 1 0 0 1 0 0 0 delays in combinational elements in the circuit? to eliminate unreachable 1 0 1 0 0 0 0 ◮ What can go wrong if D inputs of DFFs go 0 → 1 or states. 1 0 1 1 0 0 0 Let’s work through these steps. 1 → 0 at the wrong time? ◮ Assign each valid state bit 1 1 0 0 0 0 0 combination a name. 1 1 0 1 0 0 0 Section 3.5 of Harris & Harris is excellent on these topics. 1 1 1 0 0 0 0 Please read it carefully, more than once! Let’s perform the last two of the 1 1 1 1 0 0 0 above steps. ENEL 353 F13 Section 02 Slides for Lecture 30 slide 7/21 ENEL 353 F13 Section 02 Slides for Lecture 30 slide 8/21 ENEL 353 F13 Section 02 Slides for Lecture 30 slide 9/21 Review: The static discipline The dynamic discipline Setup and hold times for DFFs The dynamic discipline has to do with rules about the timing CLK t setup t hold of transitions on input signals to sequential devices such as latches and flip-flops. This idea was introduced very early in the course. (See D Q CLK Section 1.6 of Harris and Harris.) If a sequential circuit design does not comply with the dynamic discipline, the circuit is likely to be unreliable or The static discipline says that for reliable operation of digital The setup time , t setup (just t s in some textbooks) is a short completely defective. circuit elements, voltages on inputs of circuit elements must time interval before a rising edge on CLK. not sit in the forbidden zone between V IL and V IH . Specifically, for D flip-flops, the dynamic discipline says: The hold time , t hold (just t h in some textbooks) is a short time (Of course, voltages are allowed to pass through the forbidden The D input to a DFF must not make a 0 → 1 interval after a rising edge on CLK. zone when making low-to-high or high-to-low transitions!) or 1 → 0 transition within an aperture time Proper DFF behaviour—Q copies D on rising edges of surrounding an an active clock edge. CLK—is guaranteed only if D does not change value within The aperture time , as we’ll see, is defined by two DFF timing the aperture time defined by the setup and hold times. parameters called the setup time and the hold time .

ENEL 353 F13 Section 02 Slides for Lecture 30 slide 10/21 ENEL 353 F13 Section 02 Slides for Lecture 30 slide 11/21 ENEL 353 F13 Section 02 Slides for Lecture 30 slide 12/21 Setup and hold times—example 1 Setup and hold times—example 2 Setup and hold times—example 3 Here there is a violation of the setup-and-hold-time rules The gold rectangles mark apertures defined by setup and around t 1 . hold times for a DFF. CLK CLK CLK D D D Q ? ? ? Q Q t 0 t 1 t 0 t 1 t 0 t 1 Here D changes after the aperture around t 1 is over, so Q What happens to Q after t 1 ? There are multiple remains 0 for the clock cycle following t 1 . Here D is stable through both apertures, so Q reliably takes possibilities , which we’ll get to later. values of 0 shortly after t 0 and 1 shortly after t 1 . For now, what’s important to know is that circuit behaviour following t 1 is unpredictable . slide 13/21 slide 14/21 slide 15/21 ENEL 353 F13 Section 02 Slides for Lecture 30 ENEL 353 F13 Section 02 Slides for Lecture 30 ENEL 353 F13 Section 02 Slides for Lecture 30 D flip-flop clock-to-Q delays: t ccq and t pcq t setup , t hold , t ccq , and t pcq , all on one timing diagram Where do DFF timing parameters come from? CLK CLK As mentioned as few lectures ago, the Q The range of possible clock-to-Q delays from as fast as t ccq to output of a DFF does not change at exactly output(s) as slow as t pcq reflects factors such as the same time as its input CLK signal D Q ◮ variation in V DD rises—there is a short delay. input(s) ◮ variation in temperature t ccq is the clock-to-Q contamination delay . It takes at least ◮ minor variations in physical dimensions and chemical t setup t hold this much time for a rising edge of CLK to cause a change composition of transistors t ccq in Q . ◮ various other physical factors. t pcq t pcq is the clock-to-Q propagation delay . It takes no more t setup and t hold are worst-case numbers over all allowable than this much time for a rising edge of CLK to cause a Let’s write down some notes about how to read this diagram. operating conditions for a circuit. change in Q . Image is Figure 3.37 from Harris D. M. and Harris S. L., Digital Design and Computer Architecture, 2nd ed. , c � 2013, Elsevier, Inc. ENEL 353 F13 Section 02 Slides for Lecture 30 slide 16/21 ENEL 353 F13 Section 02 Slides for Lecture 30 slide 17/21 ENEL 353 F13 Section 02 Slides for Lecture 30 slide 18/21 A generic piece of synchronous sequential logic Setup time constraint Hold time constraint Below is a small part of a larger synchronous sequential circuit. Registers R1 and R2 are collections of DFFs that all have the CLK CLK same t setup , t hold , t ccq , and t pcq . CLK D1 Q1 D2 Q2 C L D1 Q1 D2 Q2 C L D1 Q1 D2 Q2 R1 R2 C R1 R2 L Recall that T C stands for the clock period . Suppose there is a rising edge of CLK at time t 0 . What must R1 R2 Suppose there is a rising edge of CLK at time t 0 . What must be true so that there is no hold time violation at R2 at the The combinational element shown has contamination delay t cd be true so that there is no setup time violation at R2 at the same rising edge of CLK, also at time t 0 ? and propagation delay t pd . next rising edge of CLK, at time t 0 + T C ? Again, let’s do some simple math, then make some remarks. We’ll assume that signal D1 meets the setup and hold time Let’s do the simple math, then make some remarks. requirements of R1, and look at whether signal D2 meets the setup and hold time requirements of R2.

ENEL 353 F13 Section 02 Slides for Lecture 30 slide 19/21 ENEL 353 F13 Section 02 Slides for Lecture 30 slide 20/21 ENEL 353 F13 Section 02 Slides for Lecture 30 slide 21/21 Hold time constraint: Direct Q-to-D connection Remark about resettable, settable, and enabled Upcoming topics flip-flops CLK Let’s look at this special case, in which there is no The textbook doesn’t mention this, but it’s good to know. combinational delay between a D 1 Q 1 D 2 Q 2 Examples of timing calculations for synchronous sequential Q output of a DFF and the For DFFs with EN inputs, and/or synchronous reset or set logic. D input of another DFF. inputs, the EN, reset and set inputs have t setup and t hold FF1 FF2 Introduction to the concept of clock skew . parameters that are similar to the t setup and t hold parameters Let’s assume that the DFFs are identical, and that setup and Introduction to the concept of metastability . for the D input. hold time conditions are satisfied by the D 1 input to FF1. For DFFs with asynchronous reset or set inputs, the timing Related reading in Harris & Harris: Section 3.5.2–3.5.4. What must be true so that there is no hold time violation parameters for those inputs are typically a minimum width at FF2 at the same rising edge of CLK, also at time t 0 ? for a reset or set pulse , along with a minimum gap between when reset or set is turned off and a rising edge of the clock. Let’s do the very simple math, then make some remarks.

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.

![MARKDOWN SLIDES [EN] MARKDOWN SLIDES [EN] MARKDOWN SLIDES [EN] MARKDOWN SLIDES [EN] MARKDOWN](https://c.sambuz.com/818511/markdown-slides-en-markdown-slides-en-markdown-slides-en-s.webp)