Lecture 38 Last time: CMOS cascode transconductance amplifier - PowerPoint PPT Presentation

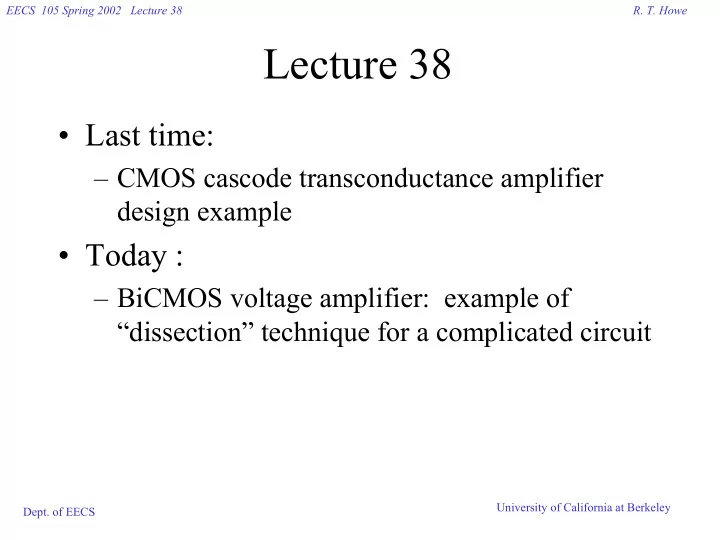

EECS 105 Spring 2002 Lecture 38 R. T. Howe Lecture 38 Last time: CMOS cascode transconductance amplifier design example Today : BiCMOS voltage amplifier: example of dissection technique for a complicated circuit

EECS 105 Spring 2002 Lecture 38 R. T. Howe Lecture 38 • Last time: – CMOS cascode transconductance amplifier design example • Today : – BiCMOS voltage amplifier: example of “dissection” technique for a complicated circuit University of California at Berkeley Dept. of EECS

EECS 105 Spring 2002 Lecture 38 R. T. Howe Multi-Stage Voltage Amplifier University of California at Berkeley Dept. of EECS

EECS 105 Spring 2002 Lecture 38 R. T. Howe Cutting Through the Complexity Two Approaches: 1. Eliminate “background” transistors to reduce clutter 2. Identify the “signal path” between the input and output University of California at Berkeley Dept. of EECS

EECS 105 Spring 2002 Lecture 38 R. T. Howe First Approach: Find I & V Sources University of California at Berkeley Dept. of EECS

EECS 105 Spring 2002 Lecture 38 R. T. Howe What’s Left? Voltage at base of Q 2 is set by totem pole University of California at Berkeley Dept. of EECS

EECS 105 Spring 2002 Lecture 38 R. T. Howe Second Approach: Find Signal Path University of California at Berkeley Dept. of EECS

EECS 105 Spring 2002 Lecture 38 R. T. Howe Identifying the Stages First stage (or two stages): CS/CB cascode Second stage (or two stages): CD/CC voltage buffer Why does this make sense for a voltage amplifier? University of California at Berkeley Dept. of EECS

EECS 105 Spring 2002 Lecture 38 R. T. Howe Find Key Two-Port Parameters Output resistance of cascode: { ( ) } = + R r || r ( 1 g r || R π out , CS / CB oc o 2 m 2 2 S 2 ( ) = = + r R r 6 1 g R oc up o m 6 S 6 University of California at Berkeley Dept. of EECS

EECS 105 Spring 2002 Lecture 38 R. T. Howe Two-Port Parameters (Cont.) University of California at Berkeley Dept. of EECS

EECS 105 Spring 2002 Lecture 38 R. T. Howe Output Resistance and Voltage Gain Source resistance of the CC stage is the output resistance of the CD stage (small) R 1 1 1 1 = = + = + ≈ S , CC R R out out , CC β β g g g g m 4 o m 4 m 3 o m 4 Open-circuit voltage gain A v (last two stages have nearly unity gain): ( ( ) ) = − β + A g r || r 1 g r v m 1 o o 2 o 6 m 6 o 7 University of California at Berkeley Dept. of EECS

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.