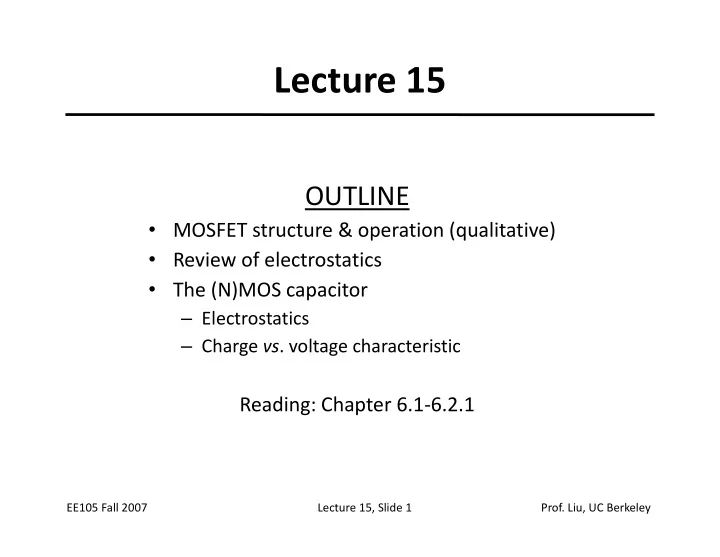

Lecture 15 OUTLINE MOSFET structure & operation (qualitative) - PowerPoint PPT Presentation

Lecture 15 OUTLINE MOSFET structure & operation (qualitative) Review of electrostatics The (N)MOS capacitor Electrostatics El t t ti Charge vs . voltage characteristic Reading: Chapter 6.1 6.2.1 EE105 Fall 2007

Lecture 15 OUTLINE • MOSFET structure & operation (qualitative) • Review of electrostatics • The (N)MOS capacitor – Electrostatics El t t ti – Charge vs . voltage characteristic Reading: Chapter 6.1 ‐ 6.2.1 EE105 Fall 2007 Lecture 15, Slide 1 Prof. Liu, UC Berkeley

The MOSFET GATE LENGTH, L g Metal-Oxide-Semiconductor OXIDE THICKNESS, T ox Field-Effect Transistor: Field-Effect Transistor: Gate Source Drain Substrate M. Bohr, Intel Developer JUNCTION DEPTH, X j Forum , September 2004 • Current flowing through the channel between the source and drain is controlled by the gate voltage. CURRENT � “N-channel” & “P-channel” MOSFETs V TH operate in a complementary manner “CMOS” “CMOS” = Complementary MOS C l t MOS |GATE VOLTAGE| EE105 Fall 2007 Lecture 15, Slide 2 Prof. Liu, UC Berkeley

N ‐ Channel MOSFET Structure Circuit symbol • The conventional gate material is heavily doped polycrystalline silicon (referred to as “polysilicon” or “poly ‐ Si” or “poly”) – Note that the gate is usually doped the same type as the source/drain Note that the gate is usually doped the same type as the source/drain, i.e. the gate and the substrate are of opposite types. • The conventional gate insulator material is SiO 2 . • To minimize current flow between the substrate (or “body”) • To minimize current flow between the substrate (or body ) and the source/drain regions, the p ‐ type substrate is grounded. EE105 Fall 2007 Lecture 15, Slide 3 Prof. Liu, UC Berkeley

Review: Charge in a Semiconductor • Negative charges: – Conduction electrons (density = n ) – Ionized acceptor atoms (density = N A ) • Positive charges: – Holes (density = p ) ( y p ) – Ionized donor atoms (density = N D ) • The net charge density [C/cm 3 ] in a semiconductor is ( ) ρ = − + − q p n N N D A • Note that p n N Note that p , n , N D , and N A each can vary with position. and N each can vary with position • The mobile carrier concentrations ( n and p ) in the channel of a MOSFET can be modulated by an electric field via V G . EE105 Fall 2007 Lecture 15, Slide 4 Prof. Liu, UC Berkeley

Channel Formation (Qualitative) V G < V TH • As the gate voltage ( V G ) is increased, holes are repelled away from the substrate surface are repelled away from the substrate surface. – The surface is depleted of mobile carriers. The charge density within the depletion region is determined by the dopant ion density. y p y • As V G increases above the threshold voltage V G ≥ V TH V TH , a layer of conduction electrons forms at V a layer of conduction electrons forms at the substrate surface. – For V G > V TH , n > N A at the surface. � The surface region is “inverted” to be n ‐ type. � Th f i i “i t d” t b t The electron inversion layer serves as a resistive path ( channel ) for current to flow between the heavily doped ( i e highly conductive) source and drain regions flow between the heavily doped ( i.e. highly conductive) source and drain regions. EE105 Fall 2007 Lecture 15, Slide 5 Prof. Liu, UC Berkeley

Voltage ‐ Dependent Resistor • In the ON state, the MOSFET channel can be viewed as a resistor. • Since the mobile charge density within the channel depends on the gate voltage, the channel resistance is voltage ‐ dependent. EE105 Fall 2007 Lecture 15, Slide 6 Prof. Liu, UC Berkeley

Channel Length & Width Dependence • Shorter channel length and wider channel width each yield lower channel resistance, hence larger drain current. – Increasing W also increases the gate capacitance, however, which limits circuit operating speed (frequency). EE105 Fall 2007 Lecture 15, Slide 7 Prof. Liu, UC Berkeley

Comparison: BJT vs. MOSFET • In a BJT, current ( I C ) is limited by diffusion of carriers from the emitter to the collector. – I C increases exponentially with input voltage ( V BE ), because the V BE V / e carrier concentration gradient in the base is proportional to T • In a MOSFET current ( I ) is limited by drift of carriers from the • In a MOSFET, current ( I D ) is limited by drift of carriers from the source to the drain. – I D increases ~linearly with input voltage ( V G ), because the carrier concentration in the channel is proportional to ( V G ‐ V TH ) In order to understand how MOSFET design parameters affect MOSFET In order to understand how MOSFET design parameters affect MOSFET performance, we first need to understand how a MOS capacitor works... EE105 Fall 2007 Lecture 15, Slide 8 Prof. Liu, UC Berkeley

MOS Capacitor • A metal ‐ oxide ‐ semiconductor structure can be considered as a parallel ‐ plate capacitor, with the top plate being the positive plate, the gate insulator being the dielectric, and the p ‐ type semiconductor substrate being the negative plate. • The negative charges in the semiconductor (for V G > 0) are The negative charges in the semiconductor (for V G > 0) are comprised of conduction electrons and/or acceptor ions. In order to understand how the potential and charge distributions I d t d t d h th t ti l d h di t ib ti within the Si depend on V G , we need to be familiar with electrostatics... EE105 Fall 2007 Lecture 15, Slide 9 Prof. Liu, UC Berkeley

Gauss’ Law ρ ρ is the net charge density ∇ E ⋅ = ε ε ε is the dielectric permittivity � If the magnitude of electric field changes, there must be charge! • In a charge ‐ free region, the electric field must be constant. • Gauss’ Law equivalently says that if there is a net electric field leaving a region there must be positive charge in that region: leaving a region, there must be positive charge in that region: ρ ∫ ∫ ∇ ⋅ = E dV dV ε ρ ρ V V Q Q ∫ ∫ = ∫ ∫ ∫ ∫ ∇ ⋅ = ⋅ dV dV E dV d E dS d ε ε V V S Q The integral of the electric field over a ∫ ∫ ⋅ = E dS closed surface is proportional to the ε charge within the enclosed volume h ithi th l d l EE105 Fall 2007 Lecture 15, Slide 10 Prof. Liu, UC Berkeley

Gauss’ Law in 1 ‐ D ρ dE ∇ ⋅ = = E ε ε dx dx ρ = ε dE dx ε ρ x ( x ' ) x ∫ = + E ( x ) E ( x ) dx ' ε 0 x 0 0 • Consider a pulse charge distribution: E E ( x ( x ) ) ρ ( x ) X 0 d x x X X 0 0 − d qN A EE105 Fall 2007 Lecture 15, Slide 11 Prof. Liu, UC Berkeley

Electrostatic Potential • The electric field (force) is related to the potential (energy): ρ ρ 2 dV dV d d V V ( ( x x ) ) ( ( x x ) ) = − ⇒ = − E ε 2 dx dx – Note that an electron (– q charge) drifts in the direction of increasing Note that an electron ( q charge) drifts in the direction of increasing potential: dV = − = − F e qE q dx E ( x ( ) ) V ( x ( ) ) ρ ( x ) X 0 d x x x X X 0 0 0 0 X X − d qN d A EE105 Fall 2007 Lecture 15, Slide 12 Prof. Liu, UC Berkeley

Boundary Conditions • Electrostatic potential must be a continuous function. Otherwise, the electric field (force) would be infinite. • Electric field does not have to be continuous, however. Consider an interface between two materials: ∆ x ∫ ε ⋅ = − ε + ε = ε E dS E S E S Q E ( ) 1 1 2 2 inside 1 1 ⎯ ⎯ → ⎯ If Q If Q 0 0 , then th ∆ x → inside 0 ε S E ( ) − ε + ε = 2 2 E S E S 0 1 1 2 2 ε E = 1 2 ε E 2 1 Discontinuity in electric displacement ε E � charge density at interface! EE105 Fall 2007 Lecture 15, Slide 13 Prof. Liu, UC Berkeley

MOS Capacitor Electrostatics • Gate electrode: – Since E ( x ) = 0 in a metallic material, V ( x ) is constant . ( ) , ( ) • Gate ‐ electrode/gate ‐ insulator interface: – The gate charge is located at this interface. � E ( x ) changes to a non ‐ zero value inside the gate insulator. � E ( ) h t l i id th t i l t • Gate insulator: – Ideally, there are no charges within the gate insulator. y, g g � E ( x ) is constant, and V ( x ) is linear . • Gate ‐ insulator/semiconductor interface: – Since the dielectric permittivity of SiO 2 is lower than that of Si th di l t i itti it f SiO i l th th t f Si, E ( x ) is larger in the gate insulator than in the Si. • Semiconductor: – If ρ ( x ) is constant (non ‐ zero), then V ( x ) is quadratic . EE105 Fall 2007 Lecture 15, Slide 14 Prof. Liu, UC Berkeley

MOS Capacitor: V GB = 0 • If the gate and substrate materials are not the same (typically the case), there is a built ‐ in potential (~1V across the gate insulator). ), p ( g ) – Positive charge is located at the gate interface, and negative charge in the Si. – The substrate surface region is depleted of holes, down to a depth X do ρ ( ) ( x ) X do x 0 V ( x ) V S o S,o Q dep x x 0 -t ox X do EE105 Fall 2007 Lecture 15, Slide 15 Prof. Liu, UC Berkeley

Flatband Voltage, V FB • The built ‐ in potential can be “cancelled out” by applying a gate voltage that is equal in magnitude (but of the opposite polarity) as the built ‐ in potential. This gate voltage is called the flatband voltage because the resulting potential profile is flat. ρ ρ ( x ( x ) ) x -t t ox 0 V ( x ) x There is no net charge ( i.e. ρ ( x )=0) in the semiconductor under for V the semiconductor under for V GB = V FB . = V -t ox 0 EE105 Fall 2007 Lecture 15, Slide 16 Prof. Liu, UC Berkeley

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.