Lecture 15 Logistics HW4 is due today HW5 posted today HW5 posted - PDF document

Lecture 15 Logistics HW4 is due today HW5 posted today HW5 posted today Exam questions: to me Class feedback Last lecture Adders Today More on Adder timing issues (hard!) M Add ti i i (h d!) Summary

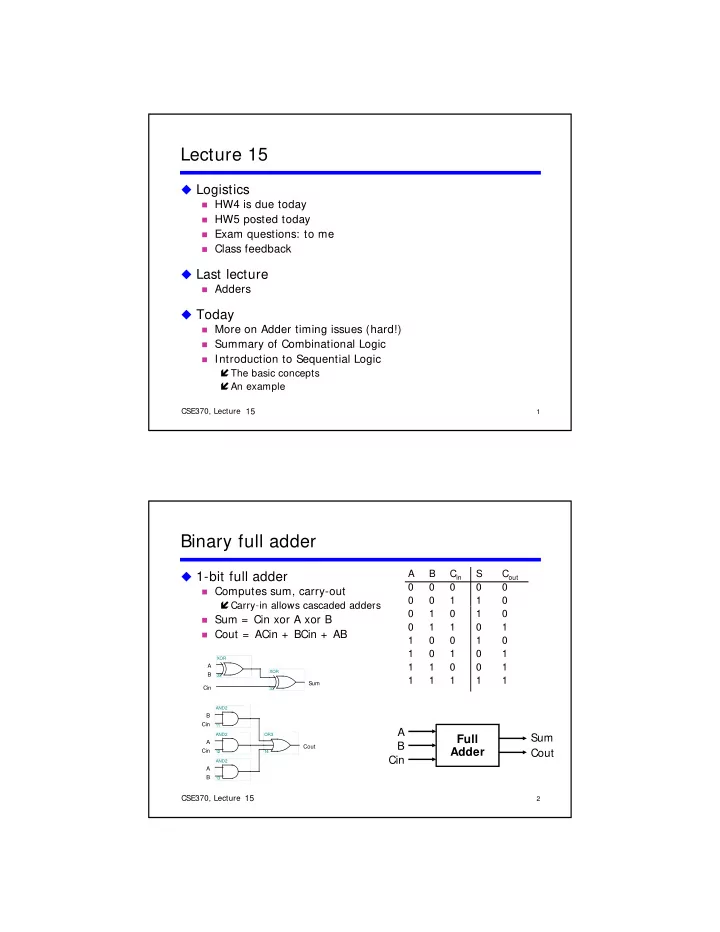

Lecture 15 � Logistics � HW4 is due today � HW5 posted today � HW5 posted today � Exam questions: to me � Class feedback � Last lecture � Adders � Today � More on Adder timing issues (hard!) M Add ti i i (h d!) � Summary of Combinational Logic � Introduction to Sequential Logic � The basic concepts � An example CSE370, Lecture 13 15 1 Binary full adder � 1-bit full adder A B C in S C out 0 0 0 0 0 � Computes sum, carry-out 0 0 1 1 0 � Carry in allows cascaded adders � Carry-in allows cascaded adders 0 1 0 1 0 � Sum = Cin xor A xor B 0 1 1 0 1 � Cout = ACin + BCin + AB 1 0 0 1 0 1 0 1 0 1 XOR 1 1 0 0 1 A XOR B 32 1 1 1 1 1 Sum Cin 33 AND2 B Cin 11 A AND2 OR3 Sum Full A B Cout Adder Cin Cout 12 14 Cin AND2 A B 13 CSE370, Lecture 13 15 11 2

Problem: Ripple-carry delay � Carry propagation limits adder speed 111 0111 A XOR XOR @0 A + 0001 B C0 XOR @0 B -------------- 32 1000 0000 Sum 0100 0110 @2N Cin 33 ???? . S0 @2 @2N+1 A0 B0 C1 @2 Except when N=0 AND2 @0 B @2N Cin 11 A1 S1 @3 B1 C2 @4 AND2 OR3 @2N+2 @2N 2 @0 @0 A A Cout @2N Cin 12 14 A2 S2 @5 AND2 B2 C3 @6 @0 A @0 B 13 C out takes two gate delays A3 S3 @7 C in arrives late B3 Cout @8 CSE370, Lecture 13 15 11 3 Speeding up the adder � Need to find a way to “predict” Cout for all bits 0 � Without knowing what Cin is � Without knowing what Cin is Cout is always 0 C t i l 0 + 0 0 -------- Predict Cout Cout is 0 if Cin is 0 0 Cout is 1 if Cin is 1 + 1 -------- Call this PROPAGATE Predict Cout � Let’s try all cases: Cout is 0 if Cin is 0 1 Cout is 1 if Cin is 1 + 0 � A = 0, B = 0 but not sure of Cin , -------- Predict Cout � A = 0, B = 1 but not sure of Cin 1 Cout is always 1 + 1 Call this GENERATE � A = 1, B = 0 but not sure of Cin -------- Predict Cout � A = 1, B = 1 but not sure of Cin CSE370, Lecture 13 15 11 4

Solution: Create a carry lookahead logic Getting Pi an Gi AND2 B XOR Cin 11 Pi A A AND2 OR3 XOR B 32 A Cout Sum Cin 12 14 Cin 33 AND2 A Gi B 13 � Carry generate: G i = A i B i for i-th bit � Generate Cout when A = B = 1 � Carry propagate: P i = A i xor B i for i-th bit � Propagate Cin to Cout when (A xor B) = 1 � So, Cout = G + PCin C i+ 1 = G i + P i C i CSE370, Lecture 13 11 15 5 One Solution: Carry lookahead logic � Get Pi (propagate) and Gi (generate) C0 @0 XOR Pi A A @1 @1 XOR B 32 @2 S0 @2 A0 P0 Sum @3 B0 G0 C1 @2 Cin 33 @4 AND2 A1 P1 S1 @3 B G1 @3 B1 C2 @4 Cin 11 AND2 OR3 A @ @4 A2 A2 P2 P2 S2 @5 S2 @5 Cout Cout Cin 12 14 G2 B2 C3 @6 @3 AND2 C 2 = G 1 + P 1 C 1 = G 1 + P 1 G 0 + P 1 P 0 C 0 @4 A Gi A3 P3 S3 @7 C 3 = G 2 + P 2 C 2 B 13 G3 B3 C4@8 = G 2 + P 2 G 1 + P 2 P 1 G 0 + P 2 P 1 P 0 C 0 C 1 = G 0 + P 0 C 0 @3 C 4 = G 3 + P 3 C 3 = G 3 + P 3 G 2 + P 3 P 2 G 1 + P 3 P 2 P 1 G 0 + P 3 P 2 P 1 P 0 C 0 CSE370, Lecture 13 15 6

We've finished combinational logic... � Negative numbers in binary � Truth tables � Basic logic gates � Basic logic gates � Schematic diagrams � Minterm and maxterm expansions (canonical, minimized) � de Morgan's theorem � AND/OR to NAND/NOR logic conversion � K-maps, logic minimization, don't cares � Multiplexers/demultiplexers � PLAs/PALs / � ROMs � Multi-level logics � Timing diagrams We had no way to store memory: When the input changed, the output changed � Hazards � Adders Next: Sequential logic can store memory… CSE370, Lecture 13 11 15 7 Sequential Logic (next 5 weeks!) � We learn the details � Latches, flip-flops, registers (storage) � Shift registers, counters (we can count now!) � Shift registers counters (we can count now!) � State machines (when we can store, we have states) � Moore and Mealy machines (types of state machines) � Timing and timing diagrams � timing more important than combinational logic � Synchronous and asynchronous inputs � Metastability (problem!) CSE370, Lecture 13 15 8

The “WHY” slide � Learning sequential logic � Having the ability to hold memory is important. If you couldn’t use your prior knowledge stored in the memory, you wouldn’t be very smart (and same goes for a computer). CSE370, Lecture 13 15 9 Sequential versus combinational A C B B clock Apply fixed inputs A, B When the clock ticks, the output becomes available Observe C Wait for another clock tick Ob Observe C again C i Combinational: C will stay the same Sequential: C may be different CSE370, Lecture 13 15 10

Sequential versus combinational � Combinational systems are memoryless � Outputs depend only on the present inputs Inputs Outputs System � Sequential systems have memory � Outputs depend on the present and the previous inputs Inputs System Outputs Feedback CSE370, Lecture 13 15 11 Synchronous sequential systems � Memory holds a system’s state � Changes in state occur at specific times � A periodic signal times or clocks the state changes � A periodic signal times or clocks the state changes � The clock period is the time between state changes A C B State changes occur clock at rising edge of clock pulsewidth duty cycle = pulsewidth/ period (here it is 50% ) clock period CSE370, Lecture 13 15 12

Steady-state abstraction � Outputs retain their settled values � The clock period must be long enough for all voltages to settle to a steady state before the next state change settle to a steady state before the next state change A C B clock Clock hides transient behavior clock C Settled value CSE370, Lecture 13 15 13 What did I just say about sequential logic? � Has clock � Synchronous = clocked � Exception: Asynchronous � Exception: Asynchronous � Has state � State = memory � Employs feedback � Assumes steady-state signals � Signals are valid after they have settled � Signals are valid after they have settled � State elements hold their settled output values CSE370, Lecture 13 15 14

Example: A sequential system � Door combination lock � Enter three numbers in sequence and the door opens � When one number is entered press ‘enter’ � When one number is entered, press enter � If there is an error the lock must be reset � After the door opens the lock must be reset � Inputs: Sequence of numbers, reset, enter � Outputs: Door open/close � Memory: Must remember the combination We will go through the motion of designing a real system We will teach details of “how” to do these steps in the next few weeks CSE370, Lecture 13 15 15 Understand the problem � Consider I/O and unknowns � How many bits per input? � How many inputs in sequence? � How many inputs in sequence? � How do we know a new input is entered? � How do we represent the system states? new value reset clock open/closed CSE370, Lecture 13 15 16

Implement using sequential logic � Behavior � Clock tells us when to look at inputs � After inputs have settled � After inputs have settled � Sequential: Enter sequence of numbers � Sequential: Remember if error occurred � A diagram may be helpful new value reset � Assume synchronous inputs � State sequence � Enter 3 numbers serially � Remember if error occurred b f d clock � All states have outputs � Lock open or closed open/closed CSE370, Lecture 13 15 17 A diagram (called finite-state diagram) � States: 5 � Inputs: reset, new, results of � Each state has outputs comparisons � Assume synchronous inputs y p � Outputs: open/closed � O t t / l d We use state diagrams to represent sequential logic ERR System transitions between closed finite numbers of states C1!= value C2!= value C3!= value & new & new & new & new S1 S2 S3 OPEN reset closed closed closed open C1= = value C2= = value C3= = value & new & new & new not new not new not new CSE370, Lecture 13 15 18

Separate data path and control � Data path � Control � Stores combination � Finite state-machine controller � Compares inputs with � Compares inputs with � Control for data path � Control for data path combination � State changes clocked new reset C1 C2 C3 4 4 4 mux control multiplexer multiplexer 4 controller clock value comparator equal 4 open/closed CSE370, Lecture 13 15 19 Refine diagram; generate state table ERR � Refine state diagram to closed include internal structure not equal not equal not equal & new not equal & new & new S1 S2 S3 OPEN closed closed closed reset open mux= C1 equal mux= C2 equal mux= C3 equal & new & new & new not new not new not new next reset reset new new equal equal state state state state mux mux open/closed open/closed � Generate 1 – – – S1 C1 closed state table 0 0 – S1 S1 C1 closed 0 1 0 S1 ERR – closed 0 1 1 S1 S2 C2 closed ... 0 1 1 S3 OPEN – open ... CSE370, Lecture 13 15 20

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.