14:332:231 DIGITAL LOGIC DESIGN Ivan Marsic, Rutgers University - PDF document

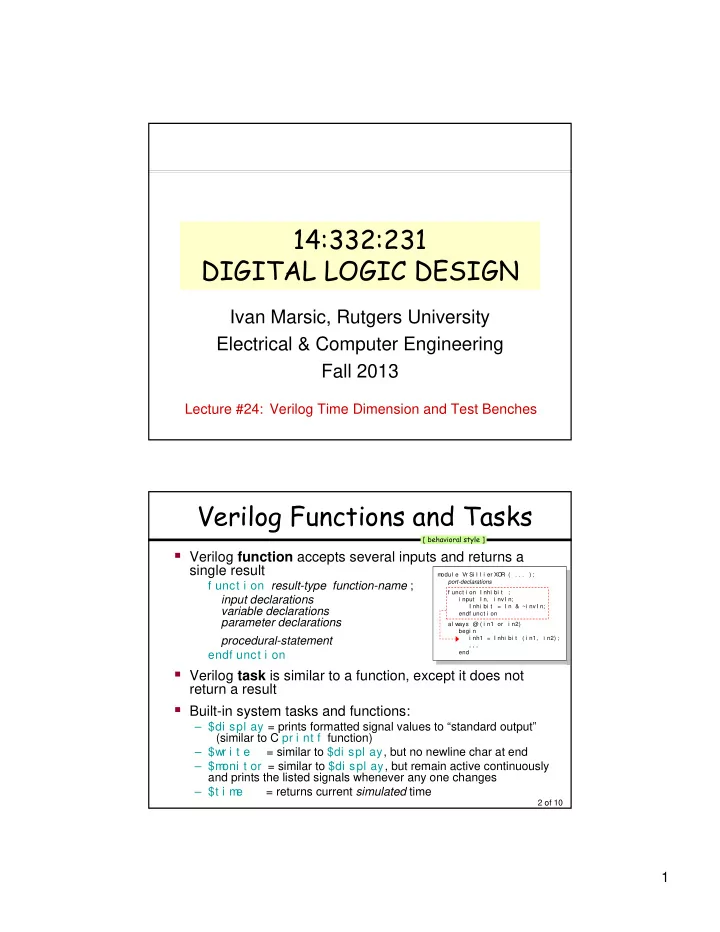

14:332:231 DIGITAL LOGIC DESIGN Ivan Marsic, Rutgers University Electrical & Computer Engineering Fall 2013 Lecture #24: Verilog Time Dimension and Test Benches Verilog Functions and Tasks [ behavioral style ] Verilog function accepts

14:332:231 DIGITAL LOGIC DESIGN Ivan Marsic, Rutgers University Electrical & Computer Engineering Fall 2013 Lecture #24: Verilog Time Dimension and Test Benches Verilog Functions and Tasks [ behavioral style ] Verilog function accepts several inputs and returns a single result m odul e Vr Si l l i er XO R ( . . . ) ; m odul e Vr Si l l i er XO R ( . . . ) ; port-declarations f unct i on result-type function-name ; port-declarations f unct i on I nhi bi t ; f unct i on I nhi bi t ; input declarations i nput I n, i nvI n; i nput I n, i nvI n; I nhi bi t = I n & ~i nvI n; variable declarations I nhi bi t = I n & ~i nvI n; endf unct i on endf unct i on parameter declarations al ways @ ( i n1 or i n2) al ways @ ( i n1 or i n2) begi n begi n procedural-statement i nh1 = I nhi bi t ( i n1, i n2) ; i nh1 = I nhi bi t ( i n1, i n2) ; . . . . . . . . . . . . endf unct i on end end Verilog task is similar to a function, except it does not return a result Built-in system tasks and functions: – $di spl ay = prints formatted signal values to “standard output” (similar to C pr i nt f function) – $wr i t e = similar to $di spl ay, but no newline char at end – $m oni t or = similar to $di spl ay, but remain active continuously and prints the listed signals whenever any one changes – $t i m e = returns current simulated time 2 of 10 1

Abstract Model Functionality [ behavioral style ] Abstract functionality is represented using procedures m odul e Ful l Adder ( i nput wi r e a, Begin with the keywords i nput wi r e b, i nput wi r e ci , i ni t i al or al ways out put r eg sum , co) ; – An i ni t i al procedure i ni t i al will execute once, beginning at simulated begi n time zero sum = 0; co = 0; – al ways procedures end model the continuous operation of hardware al ways @ ( a or b or ci ) Procedures contain begi n programming { co, sum } = a + b + ci ; statements end Multiple statements are endm odul e grouped with begi n and end 3 of 10 Procedural Block Activation All concurrent statements (procedures) automatically become active at time zero Time 0 i ni t i al i ni t i al al ways @ ( a or b) al ways @ ( posedge cl k) i ni t i al i ni t i al al ways @ ( a or b) al ways @ ( posedge cl k) begi n begi n begi n begi n begi n begi n begi n begi n a = 0; sum = 0; sum = a + b; q <= sum ; a = 0; sum = 0; sum = a + b; q <= sum ; b = 0; end end end b = 0; end end end #10 a = 1; #10 a = 1; . . . . . . end end Note: Verilog procedures are not like software subroutines, which must be called in order to be activated 4 of 10 2

Verilog Time Scale [ Verilog [ Verilog time dimension ] time dimension ] Default time scale is 1 ps (picoseconds), but can be changed using the `timescale compiler directive ` t i m escal e time-unit / time-precision – Example: ` t i m escal e 1 ns / 100 ps m odul e Vr pr i m edl y ( N, F) ; . . . / / W aker l y, Tabl e 5- 97, page 330 assi gn #2 N3L_No = ~N[ 3] ; 2 ns delay for the assi gn statement’s operation In procedural blocks of code, delays specified by writing # symbol and a delay number: – At the start of an al ways block (seen in the next slide) – After the = or <= symbol in a procedural assignment 5 of 10 Controlling Verilog Procedures [ Verilog [ Verilog time dimension ] time dimension ] i ni t i al and al ways procedures may contain 3 types of timing: 1. Time based delays — the # token – Delays execution of the next statement for a specific amount of time al ways / / del ayed f or 2 si m ul at i on t i m e uni t s #2 sum = a + b; 2. Edge sensitive delays — the @ token – Delays execution of the next statement until a change occurs on a signal al ways / / del ayed unt i l posi t i ve edge of cl ock @ ( posedge cl ock) sum <= a + b; 3. Level sensitive delays — the wai t keyword – Delays execution of the next statement until a logic test evaluates as TRUE al ways / / del ayed unt i l ' enabl e' becom es ' 1' wai t ( enabl e == 1) sum = a + b; Each time control delays execution of the next statement or statement group 6 of 10 3

Verilog Test Benches Unit under test (UUT) = the entity/module being tested – Also called Device under test (DUT) Verilog Test Bench consists of: – UUT – UUT stimulus, to provide inputs to the UUT – UUT monitor, to capture and analyze the UUT output Verilog Test Bench UUT Verilog UUT Stimulus UUT Monitor inputs outputs 7 of 10 Example Verilog Test Bench (1) select Unit under test: mux2 in0 0 (described in Lecture #23) out in1 1 / * 2- i nput m ul t i pl exor t est bench #1 * / / * 2- i nput m ul t i pl exor i n gat es * / m odul e m ux2 ( i n0, i n1, sel ect , out ) ; ` t i m escal e 1 ns / 100 ps i nput i n0, i n1, sel ect ; m odul e m ux2_t b1 ( ) ; out put out ; wi r e s0, w0, w1; wi r e m _out ; not ( s0, sel ect ) ; r eg m _sel , m _i n0, m _i n1; and ( w0, s0, i n0) , ( w1, sel ect , i n1) ; or ( out , w0, w1) ; m ux2 m 2_uut ( m _i n0, m _i n1, m _sel , m _out ) ; endm odul e / / m ux2 i ni t i al begi n Two concurrent statements: m _i n0 = 1' b0; Instance statement m _i n1 = 1' b0; i ni t i al procedure m _sel = 1' b0; Both automatically become $di spl ay ( " t i m e: % d, out put : % d" , $t i m e, m _out ) ; active at time zero #5 / / wai t 5 ns bef or e cont i nui ng The i ni t i al procedure m _i n0 = 1' b1; changes the input m _sel = 1' b1; values for UUT as it $di spl ay ( " t i m e: % d, out put : % d" , $t i m e, m _out ) ; runs continuously $f i ni sh; / / t ask cal l ends si m ul at i on end Note blocking assignments endm odul e / / m ux2_t b1 8 of 10 4

Example Verilog Test Bench (2) select Generating Test Vectors in0 0 out in1 1 / * 2- i nput m ul t i pl exor t est bench #2 * / / * 2- i nput m ul t i pl exor i n gat es * / m odul e m ux2 ( i n0, i n1, sel ect , out ) ; ` t i m escal e 1 ns / 100 ps i nput i n0, i n1, sel ect ; m odul e m ux2_t b2 ( ) ; out put out ; wi r e s0, w0, w1; wi r e m _out ; not ( s0, sel ect ) ; r eg [ 2: 0] t est _vect or s; / / 3- bi t wi de t est vect or and ( w0, s0, i n0) , i nt eger i ; ( w1, sel ect , i n1) ; or ( out , w0, w1) ; endm odul e / / m ux2 m ux2 m 2_uut ( . i n0( t est _vect or s[ 2] ) , . i n1( t est _vect or s[ 1] ) , Now, all the data is . sel ect ( t est _vect or s[ 0] ) , . out ( m _out ) ) ; stored in “test_vectors.” The most significant i ni t i al begi n / / i ni t i al i ze al l var i abl es bit, is assigned to “in0”, t est _vect or s = 3' b000; the next to “in1” and end the last to “select”. i ni t i al begi n In the second f or ( i =0; i <7; i =i +1) begi n i ni t i al block, we #5 / / wai t 5 ns bef or e cont i nui ng generate all the test t est _vect or s = t est _vect or s + 1; vectors, 000 through $di spl ay ( " t i m e: % d, out put : % d" , $t i m e, m _out ) ; 111, in a f or loop. end Note that the #5 waits end 5 ns before going to endm odul e / / m ux2_t b2 the next test vector. 9 of 10 Self-Checking Test Bench SystemVerilog asser t statement checks if specified condition is true; if not, it executes the el se statement The $er r or system task prints and error message describing the assertion failure / * 2- i nput m ul t i pl exor t est bench #3 * / ` t i m escal e 1 ns / 100 ps m odul e m ux2_t b3 ( ) ; wi r e m _out ; r eg m _sel , m _i n0, m _i n1; m ux2 m 2_uut ( m _i n0, m _i n1, m _sel , m _out ) ; i ni t i al begi n m _i n0 = 1' b0; m _i n1 = 1' b0; m _sel = 1' b0; asser t ( m _out === 0 ) el se $er r or ( " 000 f ai l ed" ) ; #5 / / wai t 5 ns m _i n0 = 1' b1; m _sel = 1' b1; / / sel ect s m _i n1, whi ch i s 1' b0 asser t ( m _out === 0 ) el se $er r or ( " 101 f ai l ed" ) ; $f i ni sh; end endm odul e / / m ux2_t b3 10 of 10 5

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.