14:332:231 DIGITAL LOGIC DESIGN Ivan Marsic, Rutgers University - PDF document

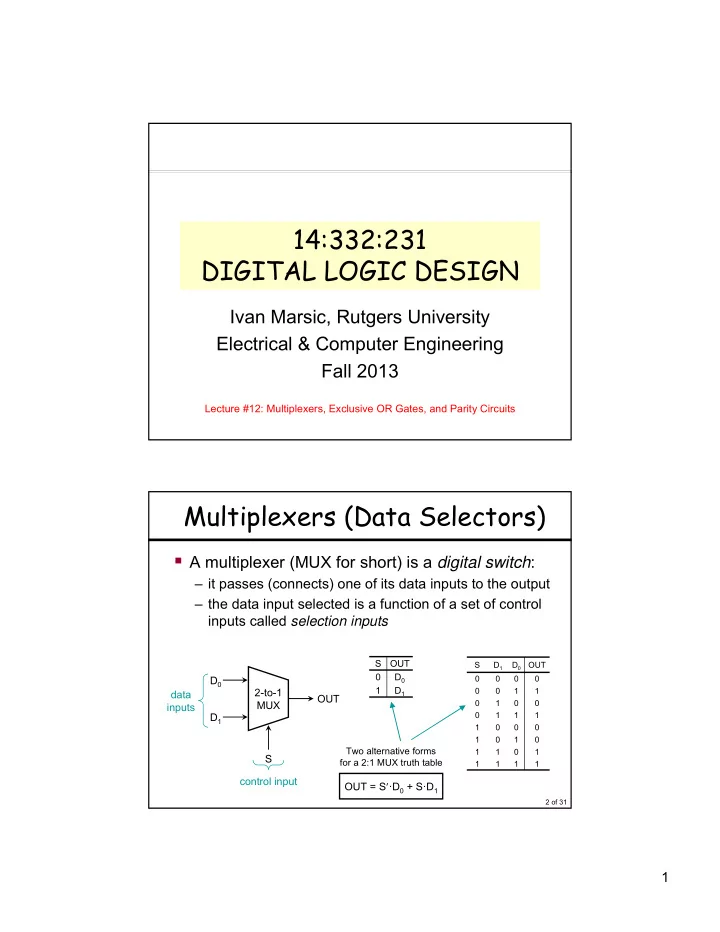

14:332:231 DIGITAL LOGIC DESIGN Ivan Marsic, Rutgers University Electrical & Computer Engineering Fall 2013 Lecture #12: Multiplexers, Exclusive OR Gates, and Parity Circuits Multiplexers (Data Selectors) A multiplexer (MUX for short)

14:332:231 DIGITAL LOGIC DESIGN Ivan Marsic, Rutgers University Electrical & Computer Engineering Fall 2013 Lecture #12: Multiplexers, Exclusive OR Gates, and Parity Circuits Multiplexers (Data Selectors) A multiplexer (MUX for short) is a digital switch : – it passes (connects) one of its data inputs to the output – the data input selected is a function of a set of control inputs called selection inputs S OUT S D 1 D 0 OUT 0 D 0 0 0 0 0 D 0 1 D 1 2-to-1 0 0 1 1 data OUT 0 1 0 0 MUX inputs D 1 0 1 1 1 1 0 0 0 1 0 1 0 Two alternative forms 1 1 0 1 S for a 2:1 MUX truth table 1 1 1 1 control input OUT = S ·D 0 + S·D 1 2 of 31 1

Multiplexers Do Selecting Selecting of data or information is a critical function in digital systems and computers Circuits that perform selecting have: – A set of n information inputs D i from which the selection is made – A set of k control (select) lines for making the selection – A single output D 0 0 D 1 1 D 2 2 n ≤ 2 k inputs D 3 3 OUT . . . D n –1 n –1 k-1 .. 1 0 S k–1 … S 1 S 0 k select lines 3 of 31 Multiplexer Analogy D 0 0 D 1 1 Out D 2 2 D 3 3 1 0 (Source: F. Vahid, “Digital Design”, J. Wiley, 2007) S 1 S 0 4 of 31 2

Example Uses of Multiplexers In computers to select among signals To implement command: X 0 Y Z if A=0 then Z=X·Y 1 else Z=X Y A Trip controller in a car to display mileage, time, speed, etc. clock Display 4-to-1 MUX odometer 0 speed 1 2 mileage 3 1 0 S 0 S 1 Push button 5 of 31 Multiplexer Structure Switch circuit 1D0 equivalent 1D1 1Y Multiplexer is 1D n –1 unidirectional 2D0 2D1 2Y multiplexer 2D n –1 enable EN s select SEL b D0 b D1 b D0 b Y b b D n –1 D1 b data n data Y sources output b SEL EN D n –1 6 of 31 3

Example: 4-to-1-line Multiplexer Expression for OUT: OUT = S 1 ·S 0 ·D 0 + S 1 ·S 0 ·D 1 + S 1 ·S 0 ·D 2 + S 1 ·S 0 ·D 3 M 0 M 1 M 2 M 3 S 1 S 0 OUT 0 0 D 0 2 k – 1 0 1 D 1 or: OUT = ∑ M j ·D j 1 0 D 2 j = 0 1 1 D 3 Circuit implementation: Sum-of-Products – 4 AND gates (4 product terms) – 2-to-4 line decoder (to generate the minterms) 7 of 31 Example: 4-to-1-line Multiplexer 2-to-2 2 -line decoder 2 2 × 2 AND-OR D 0 D 1 D 2 D 3 M 0 Decoder M 1 S 0 OUT M 2 S 1 M 3 8 of 31 4

General Multiplexer Equation A general logic equation for a multiplexer output: n 1 iY EN M j iDj j 0 Logical sum of product terms Variable iY is a particular output bit (1 ≤ i ≤ b) Mj is a minterm j of the s select inputs 9 of 31 Gate Level Implementation of MUXs positive logic: negative logic: D 1 D 1 ■ 2:1 MUX S S OUT OUT D 0 D 0 D 0 D 0 D 1 D 1 OUT OUT D 2 D 2 D 3 D 3 ■ 4:1 MUX S 0 S 0 S 1 S 1 10 of 31 5

Multiplexer Standard Packaging IC has limited number of pins (16) n·b + b + s + 1 ≤ 16 – 2 n data inputs b bits per input in out SEL EN s select inputs (n+1)·b + log 2 n ≤ 13 b n s 1 8 3 (12) 8 input 1 bit 74x151 2 4 2 (12) dual 4 input 2 bit 74x153 4 2 1 (13) quad 2 input 4 bit 74x157 11 of 31 Truth table of 74x151 Truth table for 74x151 8-input, 1-bit multiplexer Only “control” inputs are listed under “Inputs” Outputs specified as 0” or “1”, or a simple logic function of “data” inputs (e.g., D0 or D0 ) Inputs Outputs EN_L S2 S1 S0 Y Y_L 1 x x x 0 1 0 0 0 0 D0 D0 0 0 0 1 D1 D1 0 0 1 0 D2 D2 D3 0 0 1 1 D3 D4 0 1 0 0 D4 D5 0 1 0 1 D5 0 1 1 0 D6 D6 0 1 1 1 D7 D7 12 of 31 6

74x151 8-input 1-bit Multiplexer 74x151 (7) EN_L S0 S1 S2 S0 S1 S2 (4) logic diagram D0 (3) D1 and (2) D2 logic symbol (1) D3 (5) Y (6) (15) Y_L D4 (14) 74x151 D5 7 EN 11 (13) S0 D6 10 S1 9 S2 (12) 5 4 D7 D0 Y 3 6 D1 Y 2 D2 (11) 1 D3 S0 15 D4 14 D5 (10) S1 13 D6 12 D7 (9) S2 13 of 31 74x157 2-input 4-bit Multiplexer 74x157 selects between two 4-bit inputs 74x157 15 EN 1 S 2 1D0 4 1Y 3 1D1 5 2D0 7 2Y 6 2D1 11 3D0 9 3Y 10 3D1 14 4D0 12 4Y 13 4D1 14 of 31 7

74x157 2-input 4-bit Multiplexer 74x157 truth table: Inputs Outputs EN_L S 1Y 2Y 3Y 4Y 1 x 0 0 0 0 0 0 1D0 2D0 3D0 4D0 74x157 0 1 1D1 2D1 3D1 4D1 15 EN 1 S 2 1D0 4 1Y 3 1D1 5 2D0 7 2Y 6 2D1 11 3D0 9 3Y 10 3D1 14 4D0 12 4Y 13 4D1 15 of 31 Cascading/Expanding Multiplexers Large multiplexers can be made by cascading smaller ones alternative 8:1 D0 implementation mux D1 4:1 D2 mux D0 8:1 2:1 D3 D1 2:1 mux mux OUT mux D4 D2 2:1 4:1 D5 D3 mux 4:1 D6 mux OUT mux D7 D4 2:1 D5 mux S1 S0 S2 D6 2:1 D7 Control signals S1 and S0 simultaneously choose mux one of D0, D1, D2, D3 and one of D4, D5, D6, D7 S0 S2 S1 Control signal S2 chooses which of the upper or lower mux's output to gate to OUT 16 of 31 8

Cascading/Expanding Multiplexers Combining four 74x151s to make a 32-to-1 multiplexer 74x138 3-to-8 decoder used as 2-to-4 decoder for two high-order bits to enable one of 74x151s 17 of 31 Multiplexers as General-purpose Logic A 2 n :1 multiplexer can implement any function of n variables 1 0 – with the variables used as control inputs and 0 1 1 2 – the data inputs tied to 0 or 1 0 3 F 8:1 MUX 0 4 0 5 1 6 Example: 1 7 S2 S1 S0 F(A,B,C) = M 0 + M 2 + M 6 + M 7 A B C = A'·B'·C' + A'·B·C' + A·B·C' + A·B·C = A'·B'·C'·(1) + A'·B'·C·(0) + A'·B·C'·(1) + A'·B·C·(0) + A·B'·C'·(0) + A·B'·C·(0) + A·B·C'·(1) + A·B·C·(1) OUT = A'·B'·C'·I0 + A'·B'·C·I1 + A'·B·C'·I2 + A'·B·C·I3 + A·B'·C'·I4 + A·B'·C·I5 + A·B·C'·I6 + A·B·C·I7 18 of 31 9

Multiplexers as General-purpose Logic Generalization : data inputs can also be tied to variables not just 0’s an 1’s I 0 I 1 … I n –1 I n F four possible 0 configurations . . . . 0 0 1 1 n –1 mux control of truth table variables 1 . . . . 0 1 0 1 rows can be expressed as single mux data I n 0 I n 1 a function of I n variable 19 of 31 Multiplexers as Function Generators We can generate the four possible Z values (0, 1, Z, Z ) and realize the function with half the values Realizing F = ∑ X,Y,Z (0,3,5,6) with a 4-input multiplexer: 74x153 I 0 I 1 … I n –1 I n (14) A Y (2) X B 74x04 (1) Row X Y Z F 1G (1) (6) (2) Z 1C0 0 0 0 0 1 Z (5) 1C1 U1 (7) 1 0 0 1 0 1Y F (4) 1C2 2 0 1 0 0 (3) 1C3 Z (15) 3 0 1 1 2G 1 (10) 2C0 4 1 0 0 0 (11) Z 2C1 (9) 5 1 0 1 2Y unused 1 (12) 2C2 (13) 6 1 1 0 1 2C3 Z U2 7 1 1 1 0 20 of 31 10

4-variable Function using 8-input Multiplexer Realizing F = ∑ N 0 ,N 1 ,N 2 ,N 3 (1,2,3,5,7,11,13) with an 8-input multiplexer: +5V Row N 3 N 2 N 1 N 0 F 0 0 0 0 0 0 74x151 N 0 R 1 0 0 0 1 1 (7) EN 2 0 0 1 0 1 (11) 1 N 1 A 3 0 0 1 1 1 (10) N 2 B 4 0 1 0 0 0 (9) N 0 N 3 C 5 0 1 0 1 1 (4) (5) N 0 D0 Y F 6 0 1 1 0 0 (3) (6) N 0 D1 Y 7 0 1 1 1 1 (2) D2 8 1 0 0 0 0 (1) D3 0 9 1 0 0 1 0 (15) D4 10 1 0 1 0 0 (14) D5 N 0 11 1 0 1 1 1 (13) D6 12 1 1 0 0 0 (12) D7 N 0 U1 13 1 1 0 1 1 14 1 1 1 0 0 0 15 1 1 1 1 0 21 of 31 Demultiplexers Route a single input to one of many outputs, as a function of a set of control inputs y 0 y 1 y 2 1:8 y 3 x y 4 demux y 5 y 6 y 7 3 s[2:0] 22 of 31 11

Demultiplexers Demultiplexer function is just the inverse of multiplexer’s A binary decoder with enable input can be used as a demultiplexer 23 of 31 Demultiplexer Analogy A MUX driving a bus and a demultiplexer receiving the bus multiplexer demultiplexer SRCA DSTA SRCB DSTB BUS SRCC DSTC SRCZ DSTZ SRC SEL DEST SEL SRCA DSTA SRCB DSTB BUS SRCC DSTC MUX DMUX SRCZ DSTZ SRC SEL DEST SEL 24 of 31 12

Exclusive-OR Gates Exclusive-OR (XOR) gate is a 2-input gate whose output is “1” if exactly one of its input is “1” – or: XOR gate produces a “1” output if its inputs are different Exclusive-NOR (XNOR) or Equivalence just opposite—produces output “1” if its inputs are the same X X Y XOR: X Y = X ·Y + X·Y Y XNOR: (X Y) = X·Y + X ·Y X (X Y) Y 25 of 31 Exclusive-OR Gates Truth table and gate-level implementation AND-OR implementation: X F = X Y X Y (X Y) Y X Y (XOR) (XNOR) 0 0 0 1 three-level NAND implementation: 0 1 1 0 1 0 1 0 X 1 1 0 1 F = X Y Y (X·Y) · (X+Y) = (X +Y ) · (X+Y) = X ·Y + Y ·X 26 of 31 13

XOR versus XNOR (X Y) = (X ·Y + X·Y ) = (X + Y ) · (X + Y) = X·X + X ·Y + X·Y + Y ·Y = X·Y + X ·Y X X out out … the circuit XOR = XOR (X ·Y + X·Y) = X ·Y + X·Y X X out out … the circuit XNOR = XNOR X ·Y + X·Y X 1 = X·0 + X ·1 = X 27 of 31 Equivalent Symbols for XOR/XNOR XOR gates XNOR gates Simple rule: – Any two signals (inputs or output) of an XOR or XNOR gate may be complemented w/o changing the resulting logic function X 0 = X X 1 = X 28 of 31 14

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.