14:332:231 DIGITAL LOGIC DESIGN Ivan Marsic, Rutgers University - PDF document

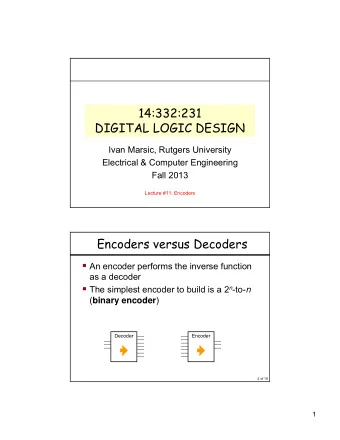

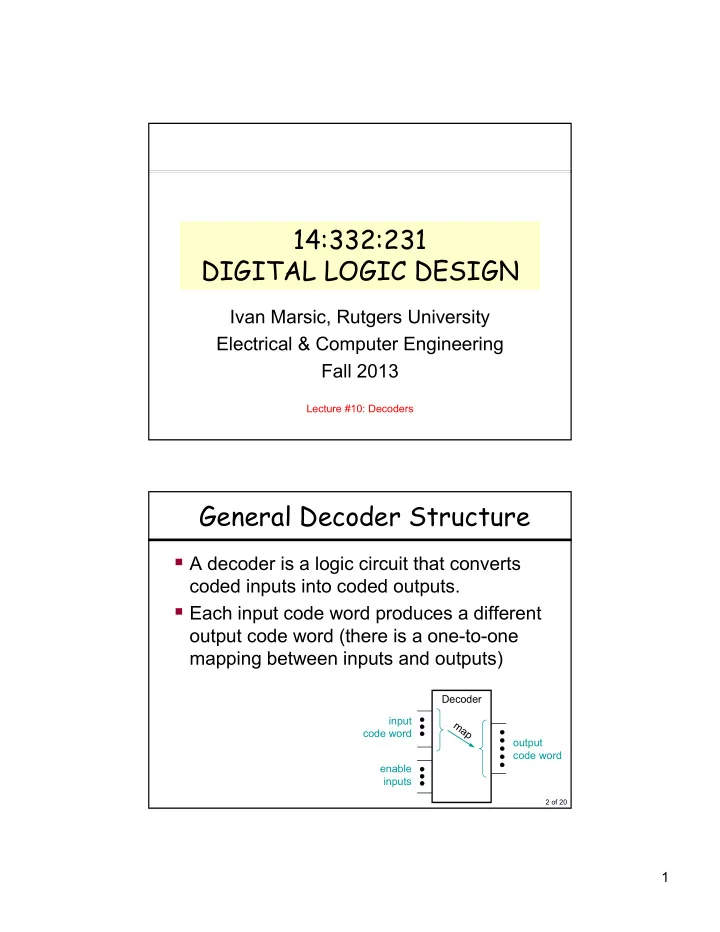

14:332:231 DIGITAL LOGIC DESIGN Ivan Marsic, Rutgers University Electrical & Computer Engineering Fall 2013 Lecture #10: Decoders General Decoder Structure A decoder is a logic circuit that converts coded inputs into coded outputs.

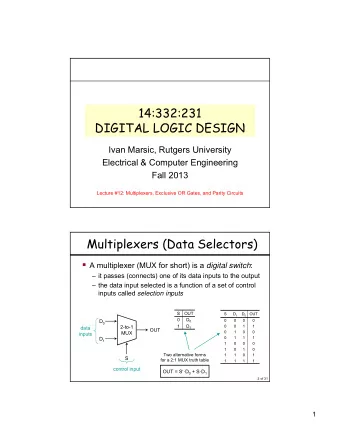

14:332:231 DIGITAL LOGIC DESIGN Ivan Marsic, Rutgers University Electrical & Computer Engineering Fall 2013 Lecture #10: Decoders General Decoder Structure A decoder is a logic circuit that converts coded inputs into coded outputs. Each input code word produces a different output code word (there is a one-to-one mapping between inputs and outputs) Decoder input m a code word p output code word enable inputs 2 of 20 1

Decoder Example BCD to seven-segment decoder – has 4-bit BCD as input code and the “seven-segment code” as its output code g f Vcc a b decoder a a f b b g c BCD d code e e f c g d ( ) BCD = binary-coded decimal e d Gnd c dp 3 of 20 Binary Decoder Accepts a n -bit binary input code and generates a 1-out- of-2 n output code Used to activate exactly one of 2 n outputs based on n -bit input value Examples: 2-to-4, 3-to-8, 4-to-16, etc. Note: BCD to seven-segment decoder is NOT a binary decoder – Because multiple outputs active simultaneously Binary decoders are n -bit input simple and general; binary combination Decoder (“code”) can be used to #1 build general decoders m a (shown later) p index number of an output line enable #2 n inputs 4 of 20 2

Gate Level Implementation of Decoders active-high active-low enable: enable: G G_L O0 O0 ■ 1:2 decoders S S O1 O1 active-high active-low enable: enable: G_L G O0 O0 O1 O1 O2 O2 O3 O3 ■ 2:4 decoders S0 S0 S1 S1 5 of 20 How It Works ■ 2:4 decoder: – input combination: “00” – input combination: “10” – output: O 0 – output: O 2 G G O0 O0 O1 O1 O2 O2 O3 O3 S0 S0 S1 S1 0 0 1 0 6 of 20 3

Binary 2-to-4 Decoder 2-to-4 Inputs Outputs decoder EN I1 I0 Y3 Y2 Y1 Y0 I0 Y0 Y1 I1 0 x x 0 0 0 0 Y2 1 0 0 0 0 0 1 EN Y3 1 0 1 0 0 1 0 1 1 0 0 1 0 0 1 1 1 1 0 0 0 Note “x” (don’t care) notation. Note that the outputs of the decoder correspond to the minterms : Y i = m i e.g., Y0 = I1 · I0 – Y1 = I1 · I0 – etc. 7 of 20 MSI 2-to-4 Decoder ( * COMPARE TO Wakerly, 4th edition, Figure 6-32(b), page 385 ) (4) Y0_L (1) EN (5) Y1_L (6) Y2_L (2) I0 (7) (3) Y3_L I1 ■ Input buffering (less load on input circuit) ■ NAND gates (faster operation) 8 of 20 4

Complete 74x139 Decoder (4) 1Y0_L 74x139 (1) 1G_L (5) 1 4 1Y0 1Y1_L 1G 5 1Y1 2 6 1A 1Y2 (6) 3 1Y2_L 7 1B 1Y3 (2) 1A (7) 12 15 2Y0 (3) 1Y3_L 2G 1B 11 2Y1 14 10 2Y2 2A 13 9 2B 2Y3 (12) 2Y0_L (15) 2G_L (11) 2Y1_L Two 2-to-4 decoders (10) 2Y2_L in a single packaging (14) 2A (9) (13) 2Y3_L 2B ( * COMPARE TO 74x138 3-to-8 decoder, described next ) 9 of 20 74x138: 3-to-8 decoder Commercially available MSI 3-to-8 decoder – Note that its outputs are active low » because TTL and CMOS inverting gates are faster than non-inverting gates 74x138 outputs 6 15 G1 Y0 5 14 G2A Y1 4 13 G2B Y2 ■ Logic equations for internal output 12 Y3 signals include “enable” signals. 11 Y4 ■ Example: 1 A 10 Y5 Y5 = G1 · G2A · G2B · C · B · A 2 B 9 Y6 3 C 7 Y7 select enable 10 of 20 5

Truth Table for a 3-to-8 Decoder Inputs Outputs G1 G2A_L G2B_L C B A Y7_L Y6_L Y5_L Y4_L Y3_L Y2_L Y1_L Y0_L 0 x x x x x 1 1 1 1 1 1 1 1 x 1 x x x x 1 1 1 1 1 1 1 1 x x 1 x x x 1 1 1 1 1 1 1 1 1 0 0 1 1 1 1 1 1 1 0 0 0 0 1 0 0 1 1 1 1 1 1 1 0 0 1 0 1 0 0 1 1 1 1 1 1 1 0 1 0 0 1 0 0 1 1 1 1 1 1 1 0 1 1 0 1 0 0 1 1 1 1 1 1 1 1 0 0 0 1 0 0 1 1 1 1 1 1 1 1 0 1 0 1 0 0 1 1 1 1 1 1 1 1 1 0 0 1 0 0 1 1 1 1 1 1 1 1 1 1 0 ■ Because of the inversion bubbles, we have the following relations between internal and external signals G2A = G2A_L Y5 = Y5_L etc. 11 of 20 3-to-8 Decoder Logic Diagram (NOR gate) (15) Y0_L (14) Y1_L (6) G1 (13) Y2_L (4) G2A_L (5) (12) Y3_L G2B_L (11) Y4_L (10) Y5_L (1) A (9) (2) Y6_L B (3) (7) Y7_L C 12 of 20 6

Decoder Cascading ■ Decoders can be cascaded hierarchically to decode larger code words 74x138 +5V R 6 G1 15 Y0 DEC0_L 14 5 Y1 G2A DEC1_L 4 13 Y2 DEC2_L G2B 12 Y3 DEC3_L ■ Example: 11 Y4 DEC4_L 1 A N0 10 Y5 Design a 4-to-16 decoder using DEC5_L 2 B N1 9 Y6 DEC6_L 74x128s (3-to-8 decoders) 3 C N2 7 Y7 DEC7_L N3 U1 EN_L 74x138 6 15 Y0 G1 DEC8_L 5 14 G2A Y1 DEC9_L 13 4 Y2 DEC10_L G2B 12 Y3 DEC11_L 11 Y4 DEC12_L 1 10 A Y5 DEC13_L 2 B 9 Y6 DEC14_L 3 C 7 Y7 DEC15_L U2 13 of 20 More Cascading 74x138 6 15 Y0 DEC0_L G1 5-to-32 decoder 5 14 Y1 DEC1_L G2A 13 4 Y2 DEC2_L G2B 12 Y3 DEC3_L 11 Y4 DEC4_L N0 1 10 A Y5 DEC5_L 2 N1 B 9 Y6 DEC6_L 3 C 7 Y7 DEC7_L N2 U2 74x138 6 15 Y0 DEC8_L G1 14 5 Y1 DEC9_L G2A 13 4 Y2 DEC10_L G2B 12 Y3 DEC11_L 11 Y4 DEC12_L 1 10 74x139 A Y5 DEC13_L 2 9 B Y6 DEC14_L EN0X7_L 3 1 4 Y0 7 EN3_L 1G C EN8X15_L Y7 DEC15_L 5 Y1 EN16X23_L U3 6 2 Y2 N3 1A EN24X31_L 74x138 3 7 Y3 N4 1B 6 15 DEC16_L G1 Y0 U1 5 14 DEC17_L Y1 G2A 13 4 DEC18_L Y2 G2B 12 DEC19_L Y3 11 Y4 DEC20_L 1 10 A Y5 DEC21_L EN1 2 9 B Y6 DEC22_L EN2_L 3 C 7 Y7 DEC23_L U4 74x138 6 15 Y0 DEC24_L G1 5 14 Y1 DEC25_L G2A 4 13 Y2 DEC26_L G2B 12 Y3 DEC27_L 11 Y4 DEC28_L 1 10 A Y5 DEC29_L 2 B 9 Y6 DEC30_L 3 C 7 Y7 DEC31_L U5 14 of 20 7

Decoder Applications Microprocessor memory systems – Selecting different banks of memory Microprocessor input/output systems – Selecting different devices Microprocessor instruction decoding – Enabling different functional units Memory chips – Enabling different rows of memory depending on address Lots of other applications 15 of 20 Decoders as General-Purpose Logic n -to-2 n decoders can implement any function of n variables – with the variables used as control inputs – the appropriate minterms summed to form the function 3-to-8 A ·B ·C Y0 decoder generates decoder A ·B ·C Y1 appropriate minterm Y2 A ·B·C based on control signals (it A I0 A ·B·C Y3 “decodes” control signals) B I1 Y4 A·B ·C C I2 Y5 A·B ·C Y6 A·B·C EN Y7 A·B·C 16 of 20 8

Decoders as General-Purpose Logic ■ F1 = A ·B·C ·D + A ·B ·C·D + A·B·C·D ■ F2 = A·B·C ·D + A·B·C A ·B ·C ·D Y0 4-to-16 A ·B ·C ·D Y1 decoder Y2 A ·B ·C·D ■ F3 = A + B + C + D F1 A ·B ·C·D Y3 A ·B·C ·D Y4 A ·B·C ·D Y5 Y6 A ·B·C·D A ·B·C·D A I0 Y7 A·B ·C ·D B I1 Y8 Y9 A·B ·C ·D C I2 F2 A·B ·C·D Y10 D I3 A·B ·C·D Y11 Y12 A·B·C ·D A·B·C ·D Y13 A·B·C·D Y14 EN F3 Y15 A·B·C·D 17 of 20 Customized Decoder Circuit CS_L RD_L A2 A1 A0 Output(s) to Assert Truth table 1 x x x x none x 1 x x x none 0 0 0 0 0 BILL_L, MARY_L 0 0 0 0 1 MARY_L, KATE_L 0 0 0 1 0 JOAN_L 0 0 0 1 1 PAUL_L 0 0 1 0 0 ANNA_L 0 0 1 0 1 FRED_L 0 0 1 1 0 DAVE_L 0 0 1 1 1 KATE_L 74x138 BILL_L +5V 74x08 R 6 1 15 G1 Y0 3 MARY_L 5 2 14 G2A CS_L Y1 U2 4 13 G2B Y2 RD_L JOAN_L 12 Y3 PAUL_L 11 Y4 ANNA_L Circuit diagram 1 A 10 A0 Y5 FRED_L 2 B A1 9 Y6 DAVE_L 3 C A2 7 74x08 Y7 4 6 U1 KATE_L 5 U2 18 of 20 9

Decoder-Based Circuits Designing a circuit for the logic function X XY F = ∑ X,Y,Z (0,2,3,5): 00 01 11 10 Z (a) Karnaugh map; (a) 0 0 2 6 4 X ·Z 1 1 (b) NAND-based minimal sum-of-products; 1 1 3 7 5 Z 1 1 (c) decoder-based canonical sum. X·Y ·Z X ·Y Y 74x04 74x00 Z 1 2 1 Z 3 2 U1 (X ·Z ) 74x138 +5V U2 R 74x00 6 15 74x10 G1 74x00 Y0 X 3 3 4 74x20 4 1 5 14 X 6 6 G2A Y1 4 F 5 U1 2 13 5 4 Y2 6 G2B Y F 12 4 U2 U3 Y3 74x04 (X ·Y) 11 5 Y Y4 U2 5 6 1 A 10 Z Y5 74x00 2 1 B U1 Y 9 Y6 (X·Y ·Z) 12 3 2 C X 7 Y7 13 U3 (b) (c) U1 19 of 20 Multiple Decoding w/ a Single Decoder 74x08 74x138 1 +5V 12 2 R H = ∑ X,Y,Z (2,4,5) 13 6 15 G1 Y0 U2 5 14 G2A Y1 74x08 13 4 Y2 G2B 3 6 12 4 Y3 G = ∑ X,Y,Z (0,1,3) 5 11 Y4 U2 1 A 10 Z Y5 74x08 2 B Y 9 Y6 11 3 C X 8 7 10 F = ∑ X,Y,Z (3,6,7) Y7 9 U2 U1 20 of 20 10

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.