14:332:231 DIGITAL LOGIC DESIGN Ivan Marsic, Rutgers University - PDF document

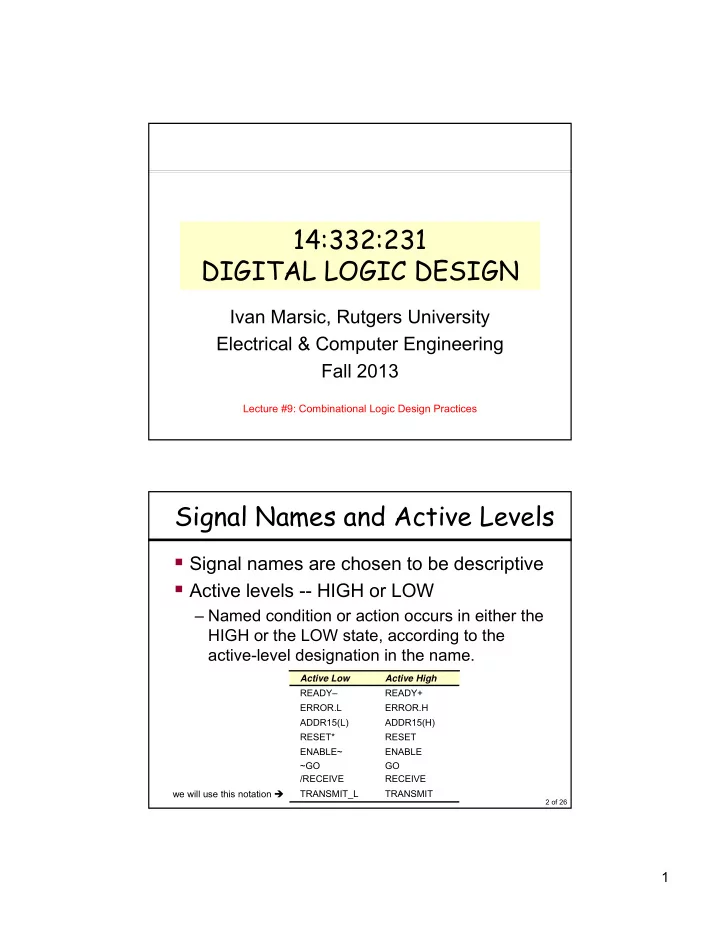

14:332:231 DIGITAL LOGIC DESIGN Ivan Marsic, Rutgers University Electrical & Computer Engineering Fall 2013 Lecture #9: Combinational Logic Design Practices Signal Names and Active Levels Signal names are chosen to be descriptive

14:332:231 DIGITAL LOGIC DESIGN Ivan Marsic, Rutgers University Electrical & Computer Engineering Fall 2013 Lecture #9: Combinational Logic Design Practices Signal Names and Active Levels Signal names are chosen to be descriptive Active levels -- HIGH or LOW – Named condition or action occurs in either the HIGH or the LOW state, according to the active-level designation in the name. Active Low Active High READY– READY+ ERROR.L ERROR.H ADDR15(L) ADDR15(H) RESET* RESET ENABLE~ ENABLE ~GO GO /RECEIVE RECEIVE we will use this notation TRANSMIT_L TRANSMIT 2 of 26 1

Errors and Active Levels HIGH when error occurs Logic ERROR Circuit LOW when error occurs ERROR_L ERROR Logic Circuit ERROR1_L 3 of 26 Flat Schematic Structure Page 1 Page 2 Page 3 Page 4 Page 5 Page 6 4 of 26 2

Hierarchical Schematic Structure Page 1 Page 2 Page 3 Page 4 Page 5 Page 6 5 of 26 Buffer A buffer is a gate with the function F = X: X F In terms of Boolean function, a buffer is the same as a wire connection! So why use it? – A buffer is an electronic amplifier used to improve circuit voltage levels and increase the speed of circuit operation. 6 of 26 3

Gate Symbols [ recall Lecture #4 ] X Y OR (X Y) NOR X Y AND (X Y) NAND X BUFFER X INVERTER 7 of 26 DeMorgan Equivalent Symbols [ Lecture #4 ] OR NOR AND “bubble-to-bubble design” NAND BUFFER INVERTER Which symbol to use? Answer depends on signal names and active levels 8 of 26 4

Example Schematic A 74HCT00 X = A_L·B + A·B_L 74HCT04 1 M1_L 3 B_L 1 2 2 74HCT00 U1 U3 10 8 X 9 74HCT04 74HCT00 A_L U1 3 4 4 M2_L 6 5 U3 B U1 74HCT00 13 M3_L 11 74HCT00 C 4 U1 5 Y 5 74HCT00 1 U2 M4_L 3 2 Y = A_L·C + B·C U2 HCT = high-speed CMOS TTL compatible 9 of 26 Circuit Timing causality and propagation delay: Circuit block diagram: GO shorter GO READY READY t RDY t RDY ENB DAT DAT longer t DAT t DAT ENB (enable) is constant minimum and maximum delays: GO READY t RDYmin t RDYmax DAT t DATmin t DATmax another graph for the ENB input … 10 of 26 5

Timing Diagrams for “Data” Signals Certain and uncertain transitions: write is on “0” WRITE_L DATAIN must be stable DATAOUT old new data t setup t OUTmin t hold t OUTmax Sequences of values on an 8-bit bus: CLEAR count is on “1” COUNT STEP[7:0] FF 00 01 02 03 11 of 26 Gates w/ Special I/O Characteristics Schmitt-trigger inputs ( Wakerly, Section 3.7.2, page 130 ) – A special circuit that uses feedback internally to shift the switching threshold depending on whether the input is changing LOW-to- HIGH or HIGH-to-LOW (“hysteresis”) Three-state outputs ( Wakerly, Section 3.7.3, page 132 ) – Output has a third electrical state (not logic state), called high- impedance , Hi-Z , or floating state – In this state, the output behaves as if it isn’t even connected to the circuit—the device output “floats” as if it weren’t even there Open-drain (open collector) outputs ( Wakerly, Section 3.7.4, page 133 ) – The output usually comprises an external pull-up resistor, which raises the output voltage when the transistor is turned off – Can be rated to withstand a higher voltage than the chip supply voltage – Commonly used to drive devices such as Nixie tubes, vacuum fluorescent displays, relays or motors that require higher operating voltages than the usual 5-Volt logic supply 12 of 26 6

Open-drain (open-collector) outputs p -channel transistor provides active pull-up of the output voltage on a LOW-to-HIGH transition Omitted in gates with open-drain outputs (see NAND gate below) [called “open-collector” in TTL] Example use: driving a light-emitting diode (LED) V CC V CC A B Z Q 1 Q 2 I LED = 10 mA R L L off off open Z L H off on open LED Z A H L on off open Q 2 H H on on L A Q 2 V OLmax = 0.37 V B Q 2 A B Q 2 Z B V CC – V OL – V LED R = I LED Open-drain CMOS NAND gate Driving an LED with an open-drain output 13 of 26 Schmitt-Trigger Inverter It has a hysteresis (difference between the two thresholds) of 0.8 Volts between the low-to-high and high-to-low inputs. V OUT 5.0 a regular inverter HIGH input-output 3.5 transfer characteristic: undefined 1.5 LOW 0 V IN V OUT Schmitt-trigger 0 1.5 3.5 5.0 V T – V T+ LOW undefined HIGH input-output 5.0 transfer characteristic: Schmitt-trigger inverter logic symbol: 0.0 V IN 0 2.1 2.9 5.0 14 of 26 7

Device Operation w/ Noisy Inputs V IN noisy, slowly- 5.0 changing input: V T+ = 2.9 V T = 2.5 V T– = 2.1 0 t V OUT HIGH ordinary inverter: LOW t V OUT HIGH Schmitt-trigger inv.: ( 0.8 V hysteresis ) LOW t 15 of 26 Enabling Function Enabling permits an input signal to pass through a circuit to an output Disabling blocks an input signal from passing through to an output, replacing it with a fixed value The value on the output when it is disable can be Hi-Z (as for three-state buffers and transmission gates, described next ), “0”, or “1” X F EN – When disabled, “0” output – When disabled, “1” output X F EN 16 of 26 8

Three-State Buffers (a.k.a. Drivers) For the symbol and truth table, Symbol: IN is the data input , and EN, EN the control input . IN OUT For EN = 0, regardless of the value on IN (denoted by X), the output value is Hi-Z. Truth table: For EN = 1, the output value follows the input value. EN IN OUT Variations: L L Hi-Z – Data input, IN, can be inverted L H Hi-Z – Control input, EN, can be H L L inverted by addition of “bubbles” to signals. H H H EN EN OUT = IN · EN IN IN OUT OUT (logic function, but ignores non-logic connectivity control) 17 of 26 Different Flavors of Three-State EN_L OUT_L EN_L OUT_L EN_L = 1 IN = x OUT = Hi-Z 74x126 74x125 18 of 26 9

Three-State Logic Circuit Normally, a logic circuit will not operate correctly if the outputs of two or more gates or other logic devices are directly connected to each other (multiple drivers conflict – “fighting”) Use of three-state logic permits the outputs of two or more gates or other logic devices to be connected together Data Selection Function: If S = 0, OL = IN0, else OL = IN1 Performing data selection with 3-state buffers: IN0 OL EN0 S OL = IN0 · S + IN1 · S IN1 EN1 Because EN0 = S and EN1 = S, one of the two buffer outputs is always Hi-Z. ( Recall: when a device output is Hi-Z, it “floats” as if it weren’t even there ) 19 of 26 8 Sources Sharing a 3-state Party Line We can tie multiple outputs together, if at most one at a time is driven. 1-bit party line P Q 74x138 SELP_L R 6 15 G1 Y0 EN1 SELQ_L SDATA 5 14 G2A EN2_L Y1 SELR_L 4 13 G2B Y2 EN3_L SELS_L S 12 Y3 SELT_L 11 Y4 1 SELU_L A 10 SSRC0 Y5 T 2 SELV_L B SSRC1 9 Y6 3 C SELW_L SSRC2 7 Y7 U V W a decoder circuit … will be described later 20 of 26 10

Timing Considerations Timing considerations for the three-state party line SSRC[20] 7 0 1 2 3 EN1 EN2_L, EN3_L SDATA W P Q R S max(t pLZmax , t pHZmax ) min(t pZLmin , t pZHmin ) dead time 21 of 26 Three-State Drivers octal three-state buffer (1) G1_L logic diagram logic symbol (19) G2_L 74x541 1 (2) (18) G1 A1 Y1 19 G2 2 18 A1 Y1 (3) (17) 3 17 A2 Y2 A2 Y2 4 16 A3 Y3 5 15 A4 Y4 6 14 (4) (16) A5 Y5 A3 Y3 7 13 A6 Y6 8 12 A7 Y7 9 11 (5) (15) A8 Y8 A4 Y4 (6) (14) A5 Y5 (7) (13) A6 Y6 (8) (12) A7 Y7 Note that enable inputs G1_L and G2_L simultaneously enable all eight buffers (9) (11) (i.e., all 8 inputs) — used in bus-based A8 Y8 applications, described next … 22 of 26 11

Buses ■ Tristate bus connecting multiple chips: Processor 8 from bus 8 to bus EN1 Shared bus Memory from bus 8 to bus EN2 Video from bus 8 to bus EN3 23 of 26 Buses - Example Microprocessor 74x541 RD_L Input Port 1 1 READ G1 SEL1_L 19 INSEL1 G2 SEL2_L INSEL2 DB0 2 18 DB0 D0 A1 Y1 INSEL3 DB1 DB1 3 17 D1 Y2 A2 DB2 4 16 DB2 D2 A3 Y3 DB3 5 15 DB3 D3 Y4 A4 User DB4 6 14 DB4 D4 Inputs A5 Y5 DB5 7 13 DB5 D5 A6 Y6 DB6 12 DB6 8 D6 A7 Y7 DB7 9 11 DB7 D7 A8 Y8 74x541 Input Port 2 1 G1 19 G2 2 18 DB0 A1 Y1 3 17 DB1 A2 Y2 16 DB2 4 Y3 A3 5 15 DB3 A4 Y4 User DB4 driver application 6 14 Inputs Y5 A5 7 13 DB5 A6 Y6 DB6 8 12 Y7 A7 9 11 DB7 A8 Y8 DB[0:7] 24 of 26 12

Three-State Transceivers logic diagram octal three-state transceiver C1 (19) logic symbol G_L 74x245 (1) DIR 19 G C2 1 DIR 2 18 A1 B1 (2) (18) 3 17 A1 B1 A2 B2 4 16 A3 B3 5 15 A4 B4 DIR=1: 6 14 A5 B5 7 (3) (17) 13 A-to-B A2 B2 A6 B6 8 12 A7 B7 9 11 DIR=0: A8 B8 B-to-A (4) (16) A3 B3 (5) (15) A4 B4 enable direction (6) (14) A5 B5 direction of G_L DIR C1 C2 transfer (7) (13) 1 x 0 0 disconnected A6 B6 0 0 B A 0 1 (8) (12) A7 B7 0 1 A B 1 0 (9) (11) A8 B8 25 of 26 Transceiver Application Example use of bidirectional transceiver 74x245 to control the direction of data transfer on bidirectional buses Bus A 74x245 ENTFR_L 19 DIR=1: G ATOB 1 DIR A-to-B Control 2 18 A1 B1 Circuits 3 17 A2 B2 4 16 A3 B3 5 15 A4 B4 6 14 A5 B5 7 13 A6 B6 DIR=0: 8 12 A7 B7 9 11 B-to-A A8 B8 Bus B 26 of 26 13

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.