The MOS Transistor With With Bulk Bulk V DD GND NMOS PMOS G - PowerPoint PPT Presentation

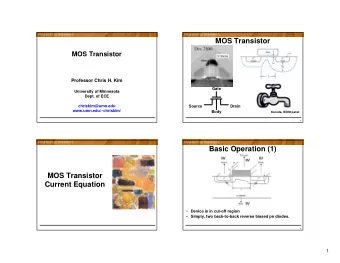

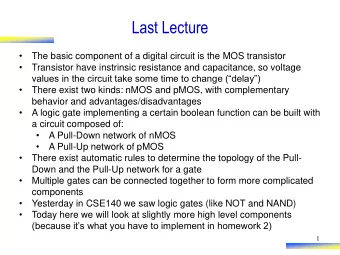

Digital IC Design The Devices NMOS PMOS Drain Drain Source S Gate + Gate Source Drain The MOS Transistor With With Bulk Bulk V DD GND NMOS PMOS G G S S D D D D S S p + p + p + n + n + n + n - p - 2 Important

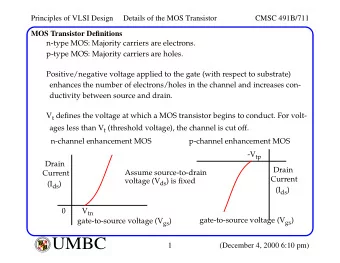

Digital IC Design The Devices NMOS PMOS Drain Drain Source S Gate + Gate Source Drain The MOS Transistor With With Bulk Bulk V DD GND NMOS PMOS G G S S D D D D S S p + p + p + n + n + n + n - p - 2 Important Dimensions I D as a function of V DS Technology Resistive operation development: Gate Linear V GS =5V Slope due to Region g Drain Source Source channel length 1993: 0.6 um W modulation V DS = V GS -V T 2003: 65 nm t ox 2013: 18 nm? V GS =4V I D Saturation L L V GS 3V V GS =3V The technology is “Diode area” 1 2 3 4 5 named after the V DS [V] gate length L 3 4 1

Problem 1 MOS Model for Long Channels Widely used model for manual calculations Given the data in the table for an NMOS transistor with k ´ =20 μ A/V2, calculate VT0, λ , and W/L. l l t VT0 λ d W/L ´ k W ≥ = 2 + λ - ; ( - ) (1 ) n V V V I V V V DS GS T D 2 GS T DS L I D ( μ A) V GS (V) V DS (V) V SB (V) 2 W V < = + λ - ; ´ (( - ) - )(1 ) DS V V V I k V V V V 1 3 5 0 1210 DS GS T D n GS T DS 2 DS L 2 5 5 0 4410 3 5 10 0 5292 = μ ´ k C Often added to n n ox avoid discontinuity = + γ φ + φ ( -2 - -2 ) V V V 0 T T F F SB 5 6 υ ( ) Velocity Saturation I D versus V DS sat I D (mA) ξ ( ) V DS forms a horizontal E-field 0.5 An increased E-field leads to higher electron velocity V GS -V T = 2.5 - 0.43 = 2.07 V Long channel Long-channel ξ ξ ( ( ) ) However at a critical E-field , the velocity saturates due However at a critical E field the velocity saturates due c 0.4 device to collisions with other atoms V GS = V DD = 2.5 5 m 0.3 υ ≈ 10 for both electrons and holes Short-channel sat s For both 0.2 device Source Source Drain Drain V DSAT = 0.63 V n + n + 0.1 V DS (V) V DS establish a horizontal E-field 0 p - 0 0.5 1.0 1.5 2.0 2.5 7 8 2

I D versus V DS Model for Manual Analysis Linear I D (V GS ) Quadratic I D (V GS ) V DS = V GS - V T A first order model for the velocity y 0 6 0.6 0 25 0.25 V GS = 2.5 saturated region: I D (mA) I D (mA) 0.5 V GS = 2.5 0.2 2 V GS = 2.0 0.4 W V V GS = 2.0 = μ − − 0.15 (( ) ) DSAT I C V V V 0.3 DSAT n ox GS T DSAT V GS = 1.5 2 L 0.1 0.2 V GS = 1.5 V GS = 1.0 0 05 0.05 GS 0.1 V GS = 1.0 0 0 0 0.5 1 1.5 2 2.5 0 0.5 1 1.5 2 2.5 V DS (V) V DS (V) Long Channel Short Channel 9 10 Problem 7 Conclusions - Static Behavior Long channel I D [uA] 1800 device 1600 lambda=120/1200=0.1 2 1400 W V Linear Region I D =1200 dI D /dV DS =60/0.5=120 = − − ´ (( ) ) 1200 DS I k V V V 1000 D n GS T DS V DS < V GS -V T 2 2 L L DS GS T 800 800 V GS =2V lambda=50/500=0.1 600 I D =500 dI D /dV DS =50/1=50 400 200 ´ k W 0 Saturated Region = − 2 + λ 0 0.5 1 1.5 2 2.5 3 ( ) (1 ) n I V V V V DS [V] D 2 GS T DS V DS > V GS -V T L Sqrt(I D ) 40 x V GS [V] V GS [V] I D [uA] I D [uA] Sqrt(I D ) Sqrt(I D ) V DS =3V 1 50 7,07 = + γ − φ + − − φ V T =0.5V x ( 2 2 ) V V V 20 Threshold Voltage 2 500 22,36 0 T T F SB F 3 1600 40,00 x V GS 1 2 3 11 12 3

Three Regions Conclusions - Static Behavior Short channel device V DSAT 2 W V = ' − − + λ (( ) )(1 ) Resistive DS I k V V V V = 2 V D n GS T DS DS V 2 2 0.15 0 15 (mA) (mA) L L I I GS GS D Velocity ' k W Linear = − + λ ( ) (1 2 ) Saturated 0.1 n saturated = I V V V 1.5 V V D 2 GS T DS L GS V DSAT = V GS -V T 1.06V 0.5 2 0.63= V GS -0.43 W V = − − + λ ' = (( ) )(1 ) Ve locity saturated 1 V DSAT I k V V V V V GS D n GS T DSAT 2 DS L V GS -V T (V) V Saturated DS 0 0 1 2 13 14 Problem 3a A Unified Model for Manual Analysis 250 2 W V 200 = − − + λ ' (( ) min )(1 ) I k V V V V min D n GS T DS 2 150 L Id [uA] 100 50 = = − min( min( , , ) ) V V V V V V V V V V min 0 0 GS T DS DSAT 0 0,5 1 1,5 2 2,5 3 Vds [V] Vgs = 1 Vgs = 1,75 Vgs = 2,5 Saturation Voltage 15 16 4

A PMOS Transistor Transistor Model for Manual Analysis Velocity saturation is less pronounced for PMOS due to lower mobility I ( A) I D (mA) 0 V GS = -1.0V -0.02 Assume all V GS = -1.5V variables -0.04 negative! negative! V V GS = -2.0V = -2 0V -0.06 -0.08 V GS = -2.5V -0.1 -2.5 -2 -1.5 -1 -0.5 0 V DS (V) 17 18 MOS Dynamic Behavior MOS Capacitances Source Gate Drain Equivalent switching resistance C GS C GD t ox V GS ≥ V T V V n + n + I D I D V GS = V DD V GS = V DD C G R C SB C DB on S D Bulk Cap. R mid R mid R 0 R 0 Junction Cap. V DS V DS V DD /2 V DD /2 V DD V DD Overlap Cap. X d 19 20 5

Junction Capacitance Channel Capacitance (Table 3-4) To Bulk To Source To Drain Total Gate Cap. Drain/ Source Diffusion C GCB C GCS C GCD C G C Diff = C Bot + C SW C Diff C Bot C SW Bottom Bottom 0 0 Cutoff C OX W L C OX W L + 2 C 0 W 0 Resistive (1/2) C OX W L (1/2) C OX W L C OX W L + 2 C 0 W e t 0 0 Don’t count the wall Saturation (2/3) C OX W L (2/3) C OX W L + 2 C 0 W a G towards the channel s d Cut off: No channel ⇒ C GC = C GCB r a w l e o n T T n n a a h C Resistive: Channel ⇒ Divide C GC in two parts W Side Saturation: ≈ 2/ 3 of Channel to source Wall L s 21 22 Problem 8 BL1 BL2 GND 0.2x0.2 um Ts Cell Border RWL Tr Node Y Contact X Tw WWL Calculate the capacitance in node Y if it consists of the gate capacitance in Ts and the drain capacitance in Tw. C ox = 5 fF/um 2 , C j0 = 1.5 fF/um 2 , and C jsw0 = 0.25 fF/m 23 6

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.

![Transistor Channel Model [Farquhar and Hasler, 2004] Transistor HH Channel Model [Farquhar and](https://c.sambuz.com/897541/transistor-channel-model-s.webp)