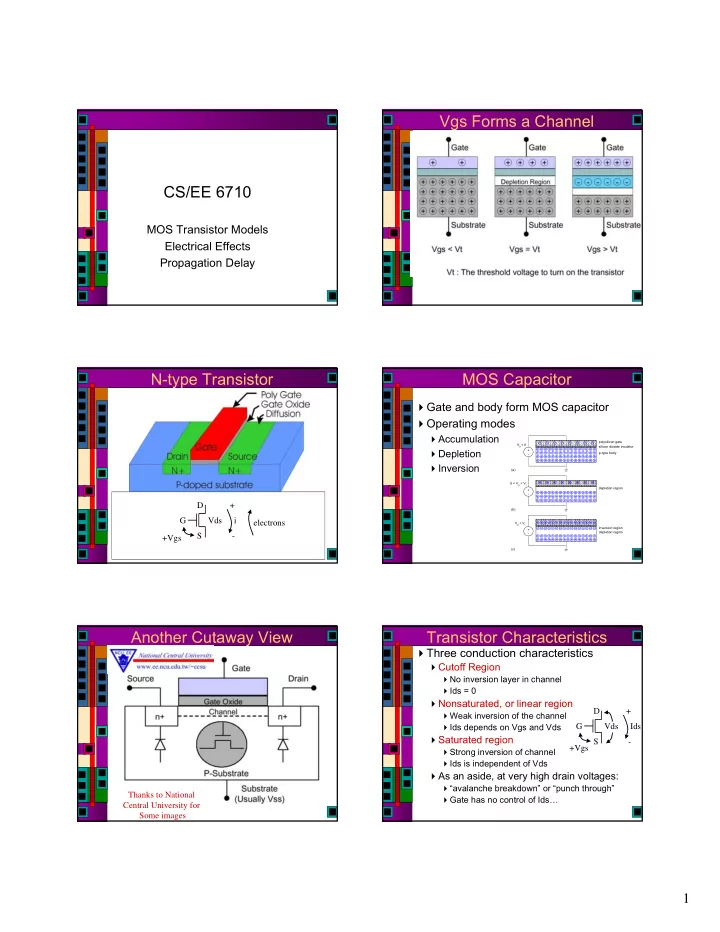

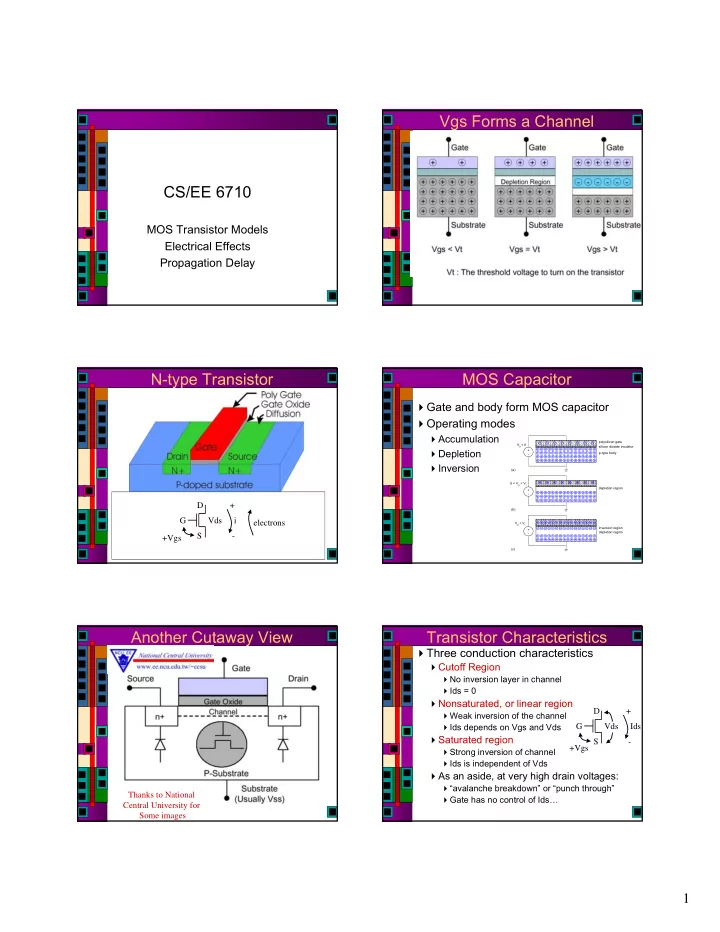

Vgs Forms a Channel CS/EE 6710 MOS Transistor Models Electrical Effects Propagation Delay N-type Transistor MOS Capacitor � Gate and body form MOS capacitor � Operating modes � Accumulation polysilicon gate V g < 0 silicon dioxide insulator � Depletion + p-type body - � Inversion (a) 0 < V g < V t depletion region + - D + (b) G Vds i electrons V g > V t inversion region + depletion region - S - +Vgs (c) Another Cutaway View Transistor Characteristics � Three conduction characteristics � Cutoff Region � No inversion layer in channel � Ids = 0 � Nonsaturated, or linear region D + � Weak inversion of the channel � Ids depends on Vgs and Vds G Vds Ids � Saturated region +Vgs S - � Strong inversion of channel � Ids is independent of Vds � As an aside, at very high drain voltages: � “avalanche breakdown” or “punch through” Thanks to National � Gate has no control of Ids… Central University for Some images 1

nMOS Cutoff: Vgs<Vt Basic N-Type MOS Transistor � Conditions for the regions of operation � No channel � Cutoff: If Vgs < Vt, then Ids is essentially 0 � I ds = 0 � Vt is the “Threshold Voltage” � Linear: If Vgs>Vt and Vds < (Vgs – Vt) then Ids depends on both Vgs and Vds V gs = 0 V gd + g + - - � Channel becomes deeper as Vgs goes up s d � Saturated: If Vgs>Vt and Vds > (Vgs – Vt) n+ n+ then Ids is essentially constant (Saturated) p-type body b D + G Vds Ids electrons S - +Vgs nMOS Linear: Vgs>Vt, small Vds Transistor Gain � β is the MOS transistor gain factor � Channel forms � β = ( με /t ox )(W/L) � Current flows V gs > V t V gd = V gs + g + from d to s Layout dependent - - s d Process-dependent � e - from s to d V ds = 0 n+ n+ � μ = mobility of carriers p-type body � I ds increases with b � Note that N-type is twice as good as P-type V ds � ε = permittivity of gate insulator V gs > V t V gs > V gd > V t + g + � ε = 3.9 ε 0 for SiO 2 ( ε 0 = 8.85x10 -14 F/cm) - - d I ds � Similar to linear s � T ox = thickness of gate oxide n+ n+ 0 < V ds < V gs -V t resistor p-type body � Also, ε /t ox =C ox The oxide capacitance b � β = ( μ C ox )(W/L) = k’(W/L) = KP(W/L) � Increase W/L to increase gain nMOS Saturation: Vds>Vgs-Vt Example � Channel pinches off � We will be using a 0.6 μ m process for � Conduction by drift because of positive drain your project voltage � From AMI Semiconductor � Electrons are injected into depletion region � t ox = 100 Å 2.5 V gs = 5 � I ds independent of V ds � μ = 350 cm 2 / V*s 2 � We say that the current saturates � V t = 0.7 V 1.5 V gs = 4 I ds (mA) � Similar to current source 1 � Plot I ds vs. V ds V gs = 3 0.5 V gs = 2 � V gs = 0, 1, 2, 3, 4, 5 V gs > V t V gs = 1 V gd < V t g + + 0 - - 0 1 2 3 4 5 � Use W/L = 4/2 λ d I ds s V ds n+ n+ V ds > V gs -V t ⎛ − ⎞ p-type body • ⋅ 14 ⎛ ⎞ W 3.9 8.85 10 W W ( ) β = μ = = μ 2 C 350 ⎜ ⎟ ⎜ ⎟ 120 A V / b ⋅ − ox 8 ⎝ ⎠ L ⎝ 100 10 ⎠ L L 2

“Saturated” Transistor N-type Pass Transistors � In the 0 < (Vgs – Vt) < Vds case � Ids Current is effectively constant � Channel is “pinched off” and conduction is 5v 4.0v 0.0v accomplished by drift of carriers � Voltage across pinched off channel (I.e. G 5v Vds) is fixed at Vgs – Vt � This is why you don’t use an N-type to pass 1’s! � Another option is a “keeper” transistor fed back � High voltage is degraded by Vt from the output � If Vt is 1.0v, 5v in one side, 4.0v out the other � This pulls the internal node high when the output is 0 5v 4.0v S D � But is disconnected when output is high G � Make sure the size is right… 5v Aside: N-type Pass Transistors N-type Pass Transistors � In practice, they are used fairly often, but be aware of what you’re doing A � For example, read/write circuits in a Out ~S Register File B * S � If it weren’t for the threshold drop, N-type WE pass transistors (without the P-type RE0 transmission gate) would be nice RE1 � 2-way Mux Example… D0 D1 Write Data Read Data N-type Pass Transistors Back to the Saturated Transistor � What influences the constant Ids in the saturated case? 5v 4.0v 0.0v � Channel length � Channel width G 5v � Threshold voltage Vt � One one hand, the degraded high voltage from � Thickness of gate oxide the pass transistor will be restored by the � Dielectric constant of gate oxide inverter � Carrier mobility μ � On the other hand, the P-device may not turn � Velocity Saturation off completely resulting in extra power being used 3

Threshold Voltage: Vt Ids Curves � The Vgs voltage at which Ids is essentially 0 � Vt = .67v for nmos and -.92v for pmos in our process � Tiny Ids is exponentially related to Vgs, Vds � Take 5720/6720 for “subthreshold” circuit ideas � Vt is affected by � Gate conductor material � Gate insulator material � Gate insulator thickness � Channel doping � Impurities at Si/insulator interface � Voltage between source and substrate (Vsb) 2 nd Order Effect: Body Effect P-type Transistor � A second order effect that raises Vt � Recall that Vt is affected by Vsb (voltage between source and substrate) � Normally this is constant because of common substrate � But, when transistors are in series, Vsb (Vs – Vsubstrate) may be changed S + -Vgs Vt2 Vsb2 = 0 G Vsd i holes Vt2 > Vt1 - Vt1 D Vsb1 = 0 Basic DC Equations for Ids P-type Transistor � Cutoff Region D + � Vgs < Vt, Ids = 0 G Vds Ids � Linear Region S - +Vgs � 0 < Vds < (Vgs – Vt) Ids = β [(Vgs – Vt)Vds – Vds 2 /2] � Note that this is only “linear” if Vds 2 /2 is very small, I.e. Vds << Vgs –Vt � Saturated Region � 0 < (Vgs – Vt) < Vds Ids = β [(Vgs – Vt) 2 /2] 4

2 nd Order Effect: Velocity Saturation P-type Transistors � Source is Vdd instead of GND � With weak fields, current increases � Vsg = (Vdd - Vin), Vsd = (Vdd -Vout), linearly with lateral electric field Vt is negative -Vgs � At higher fields, carrier drift velocity rolls � Cutoff: (Vdd-Vin) < -Vt, Ids=0 S + off and saturates Vsd i G � Due to carrier scattering � Linear Region - � Result is less current than you think! D � (Vdd-Vout) < (Vdd - Vin + Vt) � For a 2 μ channel length, effects start Ids = β [(Vdd-Vin+Vt)(Vdd-Vout) – (Vdd-Vout) 2 /2] around 4v Vdd � Saturated Region � For 180nm, effects start at 0.36v Vdd! � ((Vdd - Vin) + Vt) < (Vdd - Vout) Ids = β [(Vdd -Vin + Vt) 2 /2] 2 nd Order Effect: Velocity Saturation Pass Transistor Ckts � When the carriers reach their speed limit in silicon… V V V DD DD DD � Channel lengths have been scaled so that V V DD DD V vertical and horizontal EM fields are large DD and interact with each other Vertical field ~ 5x10 6 V/cm V DD V gs = 0 V gd + g + - - V s d DD n+ n+ V SS p-type body Horiz field = ~10 5 V/cm b 2 nd Order Effect: Velocity Saturation Pass Transistor Ckts � When the carriers reach their speed limit in silicon… V V V DD DD DD � Means that relationship between Ids and V V DD DD V Vgs is closer to linear than quadratic DD V s = V DD -V V DD -V tn V DD -V tn V DD -V tn � Also the saturation point is smaller than tn predicted � For example, 180nm process V DD V DD -V V s = |V tp | � 1 st order model = 1.3v tn V � Really is 0.6v V DD -2V DD tn V SS 5

2 nd Order Effect: Body Effect 2 nd Order Effect: Velocity Saturation � This is a basic difference between long- and short-channel devices � The strength of the horizontal EM field in a short channel device causes the carriers to reach their velocity limit early � Devices saturate faster and deliver less current than the quadratic model predicts 2 nd Order Effect: Body Effect 2 nd Order Effect: Velocity Saturation � Consider two devices with the same W/L � Consider an nmos transistor in a 180nm ratio in our process (Vgs=5v, Vdd=5v) process � 100/20 vs 4.6/1.2 � Nominal Vt of 0.4v � They should have the same current… � Body is tied to ground � Because of velocity saturation in the short- � How much does the Vt increase if the source channel device, it has 47% less current! is at 1.1v instead of 0v? � Because of the body effect, Vt increases by 0.28v to be 0.68v! 2 nd Order Effect: Body Effect 2 nd Order Effect � A second order effect that raises Vt � Recall that Vt is affected by Vsb (voltage between source and substrate) � Normally this is constant because of common substrate � But, when transistors are in series, Vsb (Vs – Vsubstrate) may be changed Vt2 Vsb2 = 0 Vt2 > Vt1 Vt1 Vsb1 = 0 6

2 nd Order Effect Inverter Switching Point � Inverter switching point is determined by ratio of β n/ β p � If β n/ β p = 1, then switching point is Vdd/2 � If W/L of both N and P transistors are equal � Then β n/ β p = μ n / μ p = electron mobility / hole mobility � This ratio is usually between 2 and 3 � Means ratio of W ptree /W ntree needs to be between 2 and 3 for β n/ β p = 1 � For this class, we’ll use W ptree /W ntree = 2 2 nd Order Effect Inverter Switching Point 2 nd Order Effect Inverter Operating Regions Linear Linear 7

Recommend

More recommend