UMBC A B M A L T F O U M B C I M Y O R T 1 - PowerPoint PPT Presentation

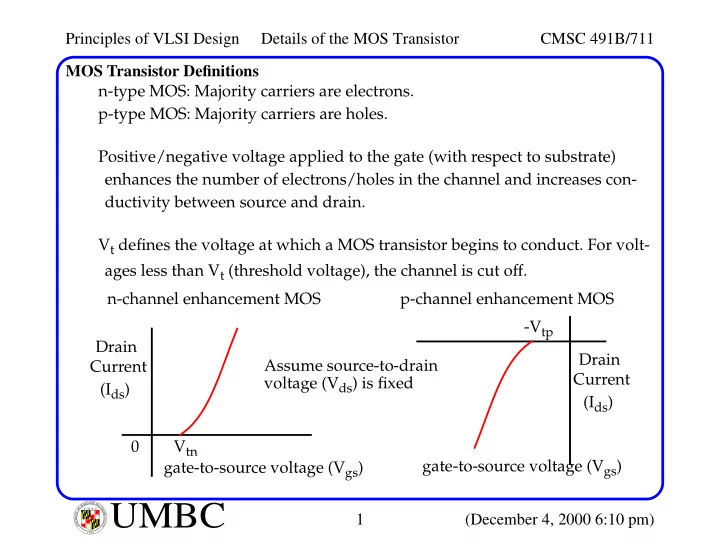

Principles of VLSI Design Details of the MOS Transistor CMSC 491B/711 MOS Transistor Definitions n-type MOS: Majority carriers are electrons. p-type MOS: Majority carriers are holes. Positive/negative voltage applied to the gate (with respect

Principles of VLSI Design Details of the MOS Transistor CMSC 491B/711 MOS Transistor Definitions n-type MOS: Majority carriers are electrons. p-type MOS: Majority carriers are holes. Positive/negative voltage applied to the gate (with respect to substrate) enhances the number of electrons/holes in the channel and increases con- ductivity between source and drain. V t defines the voltage at which a MOS transistor begins to conduct. For volt- ages less than V t (threshold voltage), the channel is cut off. n-channel enhancement MOS p-channel enhancement MOS -V tp Drain Drain Assume source-to-drain Current Current voltage (V ds ) is fixed (I ds ) (I ds ) 0 V tn gate-to-source voltage (V gs ) gate-to-source voltage (V gs ) L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 1 (December 4, 2000 6:10 pm) I E S R C E O V U I N N U T Y 1 6 9 6

Principles of VLSI Design Details of the MOS Transistor CMSC 491B/711 MOS Transistor Definitions In normal operation, a positive voltage applied between source and drain (V ds ). No current flows between source and drain (I ds = 0) with V gs = 0 because of back to back pn junctions. For n-MOS, with V gs > V tn , electric field attracts electrons creating channel. Channel is p-type silicon which is inverted to n-type by the electrons attracted by the electric field. V ds n-MOS V gs transistor I ds I ds GND Gate Source Drain Poly Gate Oxide n-channel Drain Source n+ n+ GND p-substrate L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 2 (December 4, 2000 6:10 pm) I E S R C E O V U I N N U T Y 1 6 9 6

Principles of VLSI Design Details of the MOS Transistor CMSC 491B/711 n-MOS Enhancement Transistor Physics Three modes based on the magnitude of V gs : accumulation, depletion and inversion. n-MOS transistor Accumulation Mode V gs = 0 - + Gate GND + V ds = 0 Source - Poly Drain - - - - - - + + + + + + + + + + + + + + GND + + + + + + + + + + + + + + + + + + + + + + + + + + L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 3 (December 4, 2000 6:10 pm) I E S R C E O V U I N N U T Y 1 6 9 6

Principles of VLSI Design Details of the MOS Transistor CMSC 491B/711 n-MOS Enhancement Transistor Physics V gs > 0 and V gs <= V t n-MOS transistor Depletion Mode - + Gate GND + V ds = 0 Source - depletion region Poly Drain - - - - - - + + + + + + + + GND + + + + + + + + + + + + + + + + + + + + + + + + V gs > V t n-MOS transistor - + Inversion Mode Gate GND + V ds = 0 Source - Poly Drain inversion region - - - - - - - - - - - - - - - - GND + + + + + + + + + + depletion region + + + + + + + + + + + + + + L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 4 (December 4, 2000 6:10 pm) I E S R C E O V U I N N U T Y 1 6 9 6

Principles of VLSI Design Details of the MOS Transistor CMSC 491B/711 n-MOS Enhancement Transistor With V ds non-zero, the channel becomes smaller closer to the drain. When V ds <= V gs - V t (e.g. V ds = 3V, V gs = 5V and V t = 1V), the channel reaches the drain (since V gd > V t ). This is termed linear , resistive or nonsaturated region. I ds is a function of both V gs and V ds . V gs > V t n-MOS transistor - + Inversion Mode Gate GND + V ds > 0 Source - Poly Drain inversion region GND p-substrate depletion region L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 5 (December 4, 2000 6:10 pm) I E S R C E O V U I N N U T Y 1 6 9 6

Principles of VLSI Design Details of the MOS Transistor CMSC 491B/711 n-MOS Enhancement Transistor When V ds > V gs - V t (e.g. V ds = 5V, V gs = 5V and V t = 1V), the channel is pinched off close to the drain (since V gd < V t ). This is termed saturated region. I ds is a function of V gs , almost independent of V ds . V gs > V t n-MOS transistor - + Inversion Mode Gate GND + V ds > 0 Source - Poly Drain inversion region - GND depletion region p-substrate V ds V gs - V t L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 6 (December 4, 2000 6:10 pm) I E S R C E O V U I N N U T Y 1 6 9 6

Principles of VLSI Design Details of the MOS Transistor CMSC 491B/711 MOS Enhancement Transistor MOS transistors can be modeled as a voltage controlled switch. I ds is an important parameter that determines the behavior, e.g., the speed of the switch. What are the parameters that effect the magnitude of I ds ? (Assume V gs and V ds are fixed, e.g. 5V). • The distance between source and drain (channel length). • The channel width. • The threshold voltage. • The thickness of the gate oxide layer. • The dielectric constant of the gate insulator. • The carrier (electron or hole) mobility. Summary of normal conduction characteristics: • Cut-off : accumulation, I ds is essentially zero. • Nonsaturated : weak inversion, I ds dependent on both V gs and V ds . • Saturated : strong inversion, I ds is ideally independent of V ds . L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 7 (December 4, 2000 6:10 pm) I E S R C E O V U I N N U T Y 1 6 9 6

Principles of VLSI Design Details of the MOS Transistor CMSC 491B/711 Threshold Voltage V t is also an important parameter. What effects its value? Most are related to the material properties. In other words, V t is largely deter- mined at the time of fabrication, rather than by circuit conditions, like I ds . For example, material parameters that effect V t include: The gate conductor material (poly vs. metal). The gate insulation material (SiO 2 ). The thickness of the gate material. The channel doping concentration. However, V t is also dependent on V sb (the voltage between source and substrate), which is normally 0 in dig- ital devices. Temperature: changes by -2mV/degree C for low substrate doping levels. L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 8 (December 4, 2000 6:10 pm) I E S R C E O V U I N N U T Y 1 6 9 6

Principles of VLSI Design Details of the MOS Transistor CMSC 491B/711 Threshold Voltage The expression for threshold voltage is given as: NA 2 ε SiqNA 2 φ b kT φ b 2 φ b Vt V fb - - - - - - - - - - - - - - = ln where = + - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - + q Ni Cox Ideal threshold voltage Flat band voltage Bulk potential and N A : Density of the carriers in the doped semiconductor substrate. N i : The carrier concentration of intrinsic (undoped) silicon. 10 cm 3 – × 10 ( ) Ni = 1.45 at 300 degrees K k: Boltzman’s constant. T: temperature. q: electronic charge. kT 25 mV (at 300 degrees K) - - - - - - = q ε Si : permittivity of silicon – 12 ε Si × 10 = 1.06 Farads/cm C ox : gate-oxide capacitance. ε ox Cox = - - - - - - - - tox L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 9 (December 4, 2000 6:10 pm) I E S R C E O V U I N N U T Y 1 6 9 6

Principles of VLSI Design Details of the MOS Transistor CMSC 491B/711 Threshold Voltage Threshold voltage (cont.): 2 ε SiqNA 2 φ b 2 φ b Vt V fb = + - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - + Cox Ideal threshold voltage Flat band voltage and Q fc φ ms V fb = – - - - - - - - - - - Cox where Q fc represents the fixed charge due to imperfections in silicon-oxide interface and doping. and φ ms is work function difference between gate material and silicon substrate ( φ gate - φ Si ). Typical values of V fb for n/p transistor is -0.9V (with N A = 10 16 cm -3 ) and -0.2V . (See text for examples). Typical values of V t for n and p-channel transistors are +/- 700mV. L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 10 (December 4, 2000 6:10 pm) I E S R C E O V U I N N U T Y 1 6 9 6

Principles of VLSI Design Details of the MOS Transistor CMSC 491B/711 Threshold Voltage From equations, threshold voltage may be varied by changing: The doping concentration (N A ). The oxide capacitance (C ox ). Surface state charge (Q fc ). As you can see, it is often necessary to adjust V t . Two methods are common: Change Q fc by introducing a small doped region at the oxide/substrate interface via ion implantation. Change C ox by using a different insulating material for the gate. A layer of Si 3 N 4 (silicon nitride) with a relative permittivity of 7.5 is com- bined with a layer of silicon dioxide (relative permittivity of 3.9). This results in a relative permittivity of about 6. For the same thickness dielectric layer, C ox is larger using the combined material, which lowers V t . L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 11 (December 4, 2000 6:10 pm) I E S R C E O V U I N N U T Y 1 6 9 6

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.