Slides for Lecture 25 ENEL 353: Digital Circuits Fall 2013 Term - PowerPoint PPT Presentation

Slides for Lecture 25 ENEL 353: Digital Circuits Fall 2013 Term Steve Norman, PhD, PEng Electrical & Computer Engineering Schulich School of Engineering University of Calgary 6 November, 2013 slide 2/17 ENEL 353 F13 Section 02 Slides

Slides for Lecture 25 ENEL 353: Digital Circuits — Fall 2013 Term Steve Norman, PhD, PEng Electrical & Computer Engineering Schulich School of Engineering University of Calgary 6 November, 2013

slide 2/17 ENEL 353 F13 Section 02 Slides for Lecture 25 Previous Lecture Building a D flip-flop out of two D latches in a “master-slave” configuration. The clock divider circuit—a simple application of a D flip-flop. Registers—storing multiple bits in collection of D flip-flops. Resettable flip-flops.

slide 3/17 ENEL 353 F13 Section 02 Slides for Lecture 25 Today’s Lecture Enabled flip-flops. The concept of synchronous sequential circuits . Introduction to finite state machines . Related reading in Harris & Harris: Section 3.3; Section 3.4 to the end of Section 3.4.1.

slide 4/17 ENEL 353 F13 Section 02 Slides for Lecture 25 Enabled D flip-flops D Q EN This kind of DFF is good for a circuit design in which it is useful to have a flip-flop sometimes hold its state for many clock cycles, rather than copy D on every single rising edge of the clock. Let’s write a precise description of the behaviour of an enabled DFF. Let’s show how an enabled DFF can be built using a “plain” DFF and a 2:1 multiplexer.

slide 5/17 ENEL 353 F13 Section 02 Slides for Lecture 25 Variations on enabled and resettable DFFs Here is a pretty obvious variation on the resettable DFF . . . On each rising edge of CLK, � D D Q if SET = 0 Q = s 1 if SET = 1 SET Many textbooks use the names PRESET and CLEAR instead of SET and RESET. Also note that the above is a synchronous SET—some DFFs have asynchronous SET and/or RESET. Some DFFs are designed to support two or all three of RESET, SET and EN inputs.

slide 6/17 ENEL 353 F13 Section 02 Slides for Lecture 25 The rest of Section 3.2 in Harris & Harris Section 3.2.7 presents and explains the most common present-day transistor-level designs for D latches and DFFs. We will not cover this topic in ENEL 353. If you are curious about this material, you will have to go back and read Section 1.7 before reading Section 3.2.7. Section 3.2.8 has a good example illustrating the difference between a D latch and a DFF. Check it out carefully!

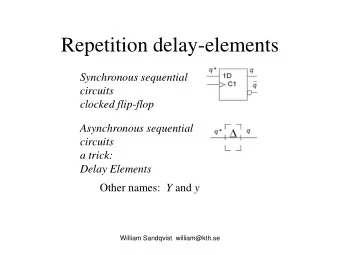

slide 7/17 ENEL 353 F13 Section 02 Slides for Lecture 25 Asynchronous sequential circuit examples Section 3.3.1 in Harris & Harris presents two sequential circuits with problematic behaviour: ◮ A ring oscillator made from 3 inverters. ◮ A D latch design that fails if delays within its components aren’t exactly right. In ENEL 353, we’re going to move on to synchronous sequential circuits, but it’s worth studying these examples to get an idea of the difficulties that can arise in sequential circuits that are not run by a clock signal .

slide 8/17 ENEL 353 F13 Section 02 Slides for Lecture 25 Synchronous sequential circuits A synchronous sequential circuit is a sequential logic system that ◮ has one or more bits of state ; and ◮ has its state updates controlled by a clock signal , so that the state updates are synchronized by the clock. Making digital systems synchronous is a very powerful design technique—the vast majority of digital circuits, including just about all practical computer processors, are synchronous sequential systems.

slide 9/17 ENEL 353 F13 Section 02 Slides for Lecture 25 Synchronous sequential circuit composition rules If a circuit satisfies these four rules, it is guaranteed to be a synchronous sequential circuit . . . 1. Every element in the circuit either is a register or is combinational. 2. At least one element is a register. 3. All registers receive the same clock signal. 4. Every cyclic path in the circuit passes through at least one register. Remark: The above conditions are sufficient but not necessary . There are designs that break some of these rules but still result in synchronous sequential circuits.

slide 10/17 ENEL 353 F13 Section 02 Slides for Lecture 25 Composition rules: Simplest possible example CLK Does a single D flip-flop, by itself, satisfy the D Q synchronous sequential circuit composition rules? 1. Every element in the circuit either is a register or is combinational. 2. At least one element is a register. 3. All registers receive the same clock signal. 4. Every cyclic path in the circuit passes through at least one register.

slide 11/17 ENEL 353 F13 Section 02 Slides for Lecture 25 Composition rules: Another simple example CLK1 Does the clock divider circuit satisfy the D Q CLK2 synchronous sequential circuit composition rules? 1. Every element in the circuit either is a register or is combinational. 2. At least one element is a register. 3. All registers receive the same clock signal. 4. Every cyclic path in the circuit passes through at least one register.

slide 12/17 ENEL 353 F13 Section 02 Slides for Lecture 25 More general examples, part 1 Which of these circuits satisfies all four synchronous sequential circuit composition rules? (a) CLK C C L L (b) CLK1 CLK2 C C C L L L

slide 13/17 ENEL 353 F13 Section 02 Slides for Lecture 25 More general examples, part 2 Which of these circuits satisfies all four synchronous sequential circuit composition rules? (c) CLK C C L L (d) CLK C L C L

slide 14/17 ENEL 353 F13 Section 02 Slides for Lecture 25 Finite state machines A k -bit finite state machine (FSM) is a synchronous sequential circuit that has a k -bit register at its centre . . . CLK D k − 1 = S ′ Q k − 1 = S k − 1 k − 1 Q k − 2 = S k − 2 D k − 2 = S ′ k − 2 . . . . . . D 1 = S ′ Q 1 = S 1 1 D 0 = S ′ Q 0 = S 0 0 How many different states can a k-bit FSM have?

slide 15/17 ENEL 353 F13 Section 02 Slides for Lecture 25 Important words on notation for FSM algebra Harris and Harris use S ′ i to mean “next state i ”, the value DFF i within the register of an FSM will get just after a rising clock edge. That is unfortunate, because A ′ means NOT( A ) in a large body of literature on digital systems. Many texts use something like Q * i for the value DFF i within the register of an FSM will get just after an active clock edge. For ENEL 353 in Fall 2013, it’s crucial to know that S ′ i means “the value state bit i will get just after a rising clock edge” and does not mean “the complement of S i ”.

slide 16/17 ENEL 353 F13 Section 02 Slides for Lecture 25 Moore machines and Mealy machines: Two kinds of FSM Let’s draw diagrams and make notes to distinguish these two types of finite state machine.

slide 17/17 ENEL 353 F13 Section 02 Slides for Lecture 25 Upcoming topics Finite state machines. Related reading in Harris & Harris: Section 3.4

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.

![MARKDOWN SLIDES [EN] MARKDOWN SLIDES [EN] MARKDOWN SLIDES [EN] MARKDOWN SLIDES [EN] MARKDOWN](https://c.sambuz.com/818511/markdown-slides-en-markdown-slides-en-markdown-slides-en-s.webp)