Repetition delay-elements Synchronous sequential circuits clocked - PowerPoint PPT Presentation

Repetition delay-elements Synchronous sequential circuits clocked flip-flop Asynchronous sequential circuits a trick: Delay Elements Other names: Y and y William Sandqvist william@kth.se Golden rule William Sandqvist william@kth.se

Repetition delay-elements Synchronous sequential circuits clocked flip-flop Asynchronous sequential circuits a trick: Delay Elements Other names: Y and y William Sandqvist william@kth.se

Golden rule William Sandqvist william@kth.se

Exitation table The asynchronous coded state table is called Excitationstable The stable states (those with next state = present state) will be ”encircled” Next state Present state SR = 00 01 10 11 y Y Y Y Y Y = y 0 0 0 1 0 1 1 0 1 0 William Sandqvist william@kth.se

Flowtable and Statediagram The Next state Present Output asynchronous Q state SR = 00 01 10 11 uncoded state A A A B A 0 B B A B A 1 table is called Flowtable SR 10 00 00 ⁄ ⁄ 01 A 0 B 1 10 11 01 11 William Sandqvist william@kth.se

William Sandqvist william@kth.se

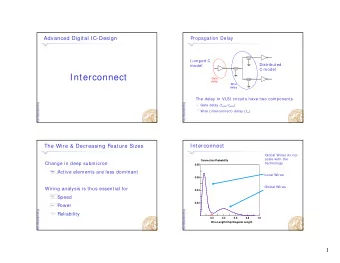

Hazard ”glitches” • When designing asynchronous circuits it can happen that you get spikes (glitches) on the signal values • This is due to the fact that different signaling pathways have different delay times • The phenomenon is called hazard and it can be eliminated by careful design William Sandqvist william@kth.se

Quickie Question … What time diagram corresponds best to the signal generated by the following gates at the rising edge? in Q 1 1 1 in in in 0 0 0 1 1 1 Q Q Q 0 0 0 Alt: A Alt: B Alt: C William Sandqvist william@kth.se

Quickie Question … What time diagram corresponds best to the signal generated by the following gates at the rising edge? in Q x 1 1 1 in in in 0 0 0 1 1 1 Q Q Q 0 0 0 1 x 0 Alt: B Alt: C Alt: A Option C does not take into Because of the delay in the inverters both account the delay of the inputs to the AND gate becomes 1 for a short time AND gate William Sandqvist william@kth.se

( A short reset pulse ) in Q The circuit is sometimes used to generate a short reset pulse. William Sandqvist william@kth.se

(A short reset pulse ) You have seen this before …. William Sandqvist william@kth.se

Different types of Hazard Static 0 → 0 Static 1 → 1 Dynamic 1 → 0 Dynamic 0 → 1 William Sandqvist william@kth.se

Static Hazard Static 0 → 0 Static 1 → 1 William Sandqvist william@kth.se

Exemple, Static Hazard • Hasard may occur at the following circuit at the transition of x 3 x 2 x 1 from 11 1 ↔ 11 0 x 2 p x 1 f q x 3 = + f x x x x 1 2 1 3 William Sandqvist william@kth.se

Timing diagram 1 x 2 p x 1 = + f x x x x f 1 2 1 3 q 1 x 3 x 1 x x 1 2 p x 3 00 01 11 10 0 1 q 1 1 1 1 f Hazard t William Sandqvist william@kth.se

Hazardfee circuit 1 x p x 1 2 x 1 p q 1 f q x 3 r r f Hazard-Cover t x x 1 2 x 3 00 01 11 10 = + + 0 1 f x x x x x x 1 2 1 3 2 3 1 1 1 1 William Sandqvist william@kth.se

How to avoid static hazard? • The possibility of static hazard is if two adjacent 1's are not covered by a own product term at SOP • Thus, one can remove the risk of static hazard by adding groupings so that all adjacent 1's are covered. William Sandqvist william@kth.se

Ex. Hazardfree groupings Are these groups enough for freedom of Hazard? f = + + f a d b cb William Sandqvist william@kth.se

Ex. Hazardfree groupings Are these groups enough for freedom of Hazard? f = + + f a d b cb Hasard cover William Sandqvist william@kth.se

Ex. Hazardfree groupings Are these groups enough for freedom of Hazard? f ? The Karnaugh-map ? is a doughnut! = + + f a d b cb William Sandqvist william@kth.se

Ex. Hazardfree groupings Are these groups enough for freedom of Hazard? f = + + + f a d b cb dc William Sandqvist william@kth.se

Ex. Hazardfree groupings Easy to miss ! f = + + + f a d b cb dc Hazard cover William Sandqvist william@kth.se

Ex. Hazardfree groupings With another variable order you can not miss! f = + + + f a d b cb dc Hazard cover William Sandqvist william@kth.se

Static hazard at POS? • If you have a POS implementation, you have to ensure that all adjacent 0's are covered by a separate sum term William Sandqvist william@kth.se

Dynamic Hazard? • A dynamic hazard causing several glitches at the output • A dynamic hazard is caused by the circuit’s structure Dynamic 1 → 0 Dynamic 0 → 1 William Sandqvist william@kth.se

Exemple, Dynamic Hazard • The following equation causes no hazard if it is implemented as an AND-OR structure = + + f x x x x x x 1 2 3 4 1 4 William Sandqvist william@kth.se

Exemple, Dynamic Hazard One gate delay • But if the equation is x implemented with the 1 following multi-level logic, , , x 2 x 3 x 4 it will exhibit dynamic a hazard b b c x 1 a f x d 2 c d x 3 f x 4 William Sandqvist william@kth.se

How to avoid Dynamic Hazard? • Dynamic hazard can be avoided with two- level logic • If a two-level circuit is free from static hazard, there is also no dynamic hazard! William Sandqvist william@kth.se

Quickie Question … What/which of the following circuits may cause hazard when x changes? x Alt: B x x Alt: A Alt: C William Sandqvist william@kth.se

Quickie Question … What/which of the following circuits may cause Risk for hazard when a=1 and b=0 hazard when x changes? The extra gate is not covering this case (but a=1 and b=1) x a Alt: B x x b not Hazard cover! Oooops! Alt: A Alt: C William Sandqvist william@kth.se

Quickie Question … Risk for hazard when a=1 and not Hazard cover! ba b=0 x 00 01 11 10 The extra gate does not cover this case (but a=1 and b=1) 0 1 1 1 1 1 1 a x no Hazard ba x b 00 01 11 10 0 1 1 Oooops! 1 1 1 1 Alt: C x b a William Sandqvist william@kth.se

When do one need to take Hazard into account? • In an asynchronous sequential circuit must the decoder for next state be without hazard! – Otherwise you could end up in an incorrect state • For combinatorical circuits hazard is not a problem because the output always will stabilize after a short time • In a synchronous sequential circuit hazard is no problem, as long as you respect setup- and hold- time ( during theese times hazard is allowed to happen! ) William Sandqvist william@kth.se

Avoid Hazard Static hazard is caused by omitted primimplicants Static 0 → 0 Static 1 → 1 Dynamic hazard can occur when implementing circuits with multi-level logic. Two- level logic circuits which are free of static hazard is also free from dynamic hazard. Dynamic 1 → 0 Dynamic 0 → 1 William Sandqvist william@kth.se

Output-spikes in asynchronous circuits Pres Next State Q state X=0 1 y 2 y 1 Y 2 Y 1 00 00 01 0 01 00 11 1 11 01 10 0 10 11 10 1 One can get the output spikes in an asynchronous sequential circuits when switching from one stable state to another by passing several unstable states (The phenomenon is no hazard!). William Sandqvist william@kth.se

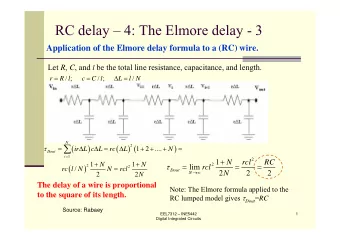

Metastability CMOS-circuit transferfunction (eg. inverter) V DD Output voltage ”1” T 1 V V x f T 2 ”0” ”0” ”1” Input voltage V x William Sandqvist william@kth.se

About metastability 1? Q 0? 1 D 0 1 0 C To understand what metastability is, we can imagine that the input signal D to a latch is very loaded and thus changes very slowly relative to the clock. Suppose further that the clock signal C changes just when D is at V DD /2. Then the latch will be locked at the value that happens to be on D . After some time the latchen will transfer to either ’1’ or ’0’. William Sandqvist william@kth.se

Om metastabilitet … This instability lasts until the transistors in the feedback pleases go to one or the other - but it can take time, and the time will depend on how close V DD /2 that the locking occurred. We can compare the situation with a ball that lies on top of a hill, or a pencil balanced on its tip. Minimum disruption will get the ball or the pen to fall to one side or the other. If Clk and D switches ? simultaneously, which value will Q be ? On which side will the ball fall down? ’0’ ’1’ William Sandqvist william@kth.se

Setup and Hold time (= metastability-protection) • To avoid simultaneously switching, setup and hold times must be guaranteed : D Clk Setup time is the time D must be stable before Clk changes its value Hold time is the time D must be stable after Clk has changed its value Setup Hold time If Setup and Hold time’s are met, then the flip-flop are guaranteed to behave nicely/deterministic! William Sandqvist william@kth.se

Asynchronous inputs? • Unfortunately, we can not always guarantee that the input is stable through the setup and hold-time • Suppose you connect a push button on the D input of a flip-flop – The user can press the button at any time, even during the setup and hold-time! – The risk is that the flip-flop ends up in a metastable state! William Sandqvist william@kth.se

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.