Lecture 22 Logistics HW7 is due on Friday Lab 8 this week Lab 8 - PDF document

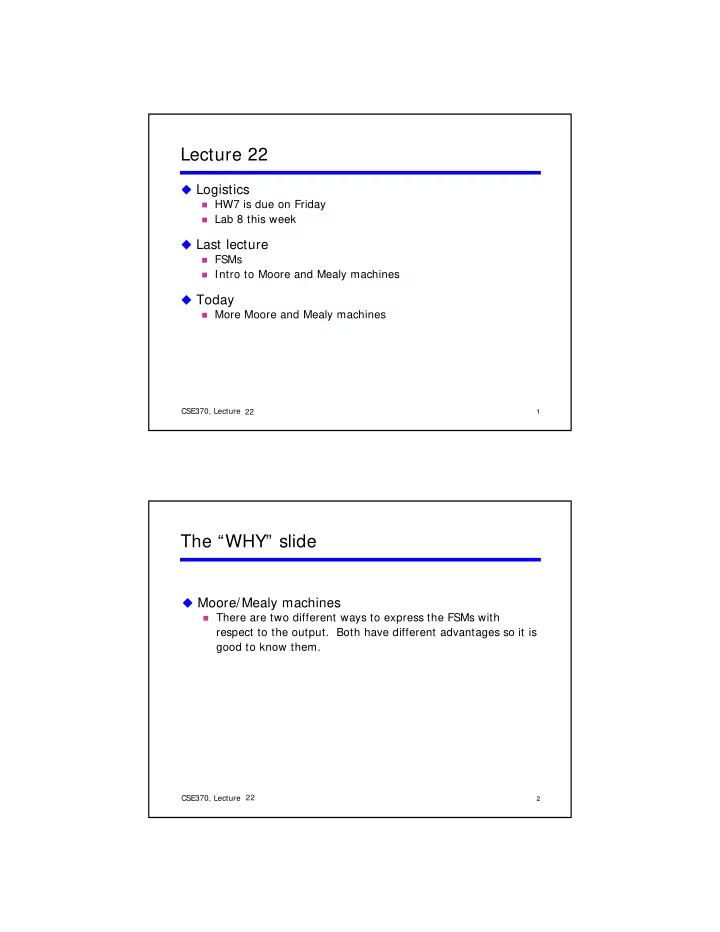

Lecture 22 Logistics HW7 is due on Friday Lab 8 this week Lab 8 this week Last lecture FSMs Intro to Moore and Mealy machines Today More Moore and Mealy machines CSE370, Lecture 19, 20 22 1 The WHY slide

Lecture 22 � Logistics � HW7 is due on Friday � Lab 8 this week � Lab 8 this week � Last lecture � FSMs � Intro to Moore and Mealy machines � Today � More Moore and Mealy machines CSE370, Lecture 19, 20 22 1 The “WHY” slide � Moore/Mealy machines � Moore/Mealy machines � There are two different ways to express the FSMs with respect to the output. Both have different advantages so it is good to know them. CSE370, Lecture 19, 20 22 2

Generalized FSM model: Moore and Mealy � Combinational logic computes next state and outputs � Next state is a function of current state and inputs � Outputs are functions of � Outputs are functions of � Current state ( Moore machine) � Current state and inputs ( Mealy machine) output Outputs Outputs logic Inputs Next-state Next State logic Current State CSE370, Lecture 19, 20 22 3 Moore versus Mealy machines Moore machine inputs Outputs are a function combinational of current state f t t t l logic for i f next state logic for reg outputs outputs Outputs change synchronously with state changes state feedback logic for Mealy machine inputs outputs outputs outputs Outputs depend on state Outputs depend on state combinational and on inputs reg logic for next state Input changes can cause immediate output changes (asynchronous ) state feedback CSE370, Lecture 19, 20 22 4

Comparing Moore and Mealy machines � Moore machines + Safer to use because outputs change at clock edge – May take additional logic to decode state into outputs – May take additional logic to decode state into outputs � Mealy machines + Typically have fewer states + React faster to inputs — don't wait for clock – Asynchronous outputs can be dangerous � We often design synchronous Mealy machines � Design a Mealy machine D i M l hi � Then register the outputs CSE370, Lecture 19, 20 22 5 Synchronous (registered) Mealy machine � Registered state and registered outputs � No glitches on outputs logic for reg inputs outputs outputs combinational reg logic for next state state feedback CSE370, Lecture 19, 20 22 6

Example 0 -> 1: Moore or Mealy? � Recognize A,B = 0,1 � Mealy or Moore? A out D Q B clock Q Registered Mealy (actually Moore) A out D Q Q B D Q clock Q Moore CSE370, Lecture 19, 20 22 7 FSM design procedure reminder � Counter-design procedure 1. State diagram 2. State-transition table 3. Next-state logic minimization 4. Implement the design � FSM-design procedure 1. State diagram 2. state-transition table 3. State minimization 4 4. State encoding State encoding 5. Next-state logic minimization 6. Implement the design CSE370, Lecture 19, 20 17 22 8

Example: A parity checker � Serial input string � OUT= 1 if odd # of 1s in input � OUT= 0 if even # of 1s in input � Let’s do this for Moore and Mealy CSE370, Lecture 19, 20 22 9 Example: A parity checker State diagram 1. Moore oo Mealy a y 0 0/0 0 Even Even [0] [0] 1 1 1/0 1/1 1 1 Odd Odd [1] [1] 0/1 CSE370, Lecture 19, 20 22 10

Example: A parity checker 1. State-transition table Moore Present Input Next Present State State Output Even 0 Even 0 Mealy Even 1 Odd 0 Odd 0 Odd 1 1 Present Input Next Present Odd 1 Even State State State State Output Output Even 0 Even 0 Even 1 Odd 1 Odd 0 Odd 1 Odd 1 Even 0 CSE370, Lecture 19, 20 22 11 Example: A parity checker 3. State minimization: Already minimized � Need both states (even and odd) � Use one flip flop � Use one flip-flop CSE370, Lecture 19, 20 22 12

Example: A parity checker Assignment 4. State encoding Even 0 Moore Odd 1 Present Input Next Present State State Output 0 0 0 0 0 1 1 0 Mealy 1 0 1 1 1 1 0 1 P Present Input Next Present t I t N t P t State State Output 0 0 0 0 0 1 1 1 1 0 1 1 1 1 0 0 CSE370, Lecture 19, 20 22 13 Example: A parity checker 5. Next-state logic minimization � Assume D flip-flops � Next state = (present state) XOR (present input) � Next state = (present state) XOR (present input) 6. Implement the design Mealy Output Moore D D Q Q D D Q Q Input Input Output Current State Q Q CLK CLK CSE370, Lecture 19, 20 22 14

Example: A vending machine � 15 cents for a cup of coffee � Doesn’t take pennies or quarters � Doesn t take pennies or quarters Reset � Doesn’t provide any change N Vending Open Coin Release Machine Sensor Mechanism FSM Last lecture D We had mix of Moore and Mealy Clock CSE370, Lecture 19, 20 17 22 15 A vending machine: Moore machine present inputs next present Reset state state D D N N state state output output 0¢ 0 0 0¢ 0 0 1 5¢ 0 0¢ 1 0 10¢ 0 1 1 – – N 5¢ 0 0 5¢ 0 0 1 10¢ 0 D 1 0 15¢ 0 5¢ 1 1 – – N 10¢ 0 0 10¢ 0 0 1 15¢ 0 1 0 15¢ 0 D 10¢ 1 1 – – 15¢ – – 15¢ 1 N + D 15¢ symbolic state table [open] CSE370, Lecture 19, 20 17 22 16

A vending machine: Mealy machine present inputs next present Reset state state D D N N state state output output 0¢ 0 0 0¢ 0 0 1 5¢ 0 0¢ 1 0 10¢ 0 1 1 – – N/0 5¢ 0 0 5¢ 0 0 1 10¢ 0 D/0 1 0 15¢ 1 5¢ 1 1 – – N/0 10¢ 0 0 10¢ 0 0 1 15¢ 1 1 0 15¢ 1 D/1 10¢ 1 1 – – 15¢ – – 15¢ 1 N + D/1 15¢ symbolic state table CSE370, Lecture 19, 20 17 22 17 A vending machine: State encoding Mealy Moore present state inputs next state present present state inputs next state present Q1 Q0 D N D1 D0 output Q1 Q0 D N D1 D0 output 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 1 0 0 1 0 1 0 1 0 1 0 0 1 0 1 0 0 1 1 – – – 1 1 – – – 0 1 0 0 0 1 0 0 1 0 0 0 1 0 0 1 1 0 0 0 1 1 0 0 1 0 1 1 1 1 0 1 1 0 1 1 – – – 1 1 – – – 1 1 0 0 0 0 0 0 1 1 0 0 0 0 1 0 0 0 1 0 0 0 1 1 1 1 0 1 1 1 0 1 0 1 1 1 1 0 1 1 0 1 1 – – – 1 1 – – – 1 1 – – 1 1 1 1 1 – – 1 1 1 CSE370, Lecture 19, 20 17 22 18

A vending machine: Logic minimization Moore Q1 Q1 D1 Q1 Open D0 0 0 1 1 0 1 1 0 0 0 1 0 0 0 1 1 1 1 1 1 N 1 0 1 1 N N 0 0 1 0 X X X X D D X X X X D X X 1 X 1 1 1 1 0 1 1 1 0 0 1 0 Q0 Q0 Q0 Mealy Q1 Q1 D1 Q1 Open D0 0 0 0 0 1 1 1 1 0 1 1 0 0 0 1 0 0 1 1 1 N 1 0 1 1 N N 0 0 1 1 X X X X D X X X X D D X X 1 X 1 1 1 1 0 1 1 1 0 1 1 1 Q0 Q0 Q0 CSE370, Lecture 19, 20 17 22 19 A vending machine: Implementation Mealy Moore CSE370, Lecture 19, 20 22 20

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.