Fast and Area Efficient Adder for Wide Data in Recent Xilinx FPGAs - PowerPoint PPT Presentation

Intro Prop Res Summary Fast and Area Efficient Adder for Wide Data in Recent Xilinx FPGAs Petter K allstr om and Oscar Gustafsson Link oping University Department of Computer Engineering 1 Intro Prop Res Summary Introduction

Intro Prop Res Summary Fast and Area Efficient Adder for Wide Data in Recent Xilinx FPGAs Petter K¨ allstr¨ om and Oscar Gustafsson Link¨ oping University Department of Computer Engineering 1

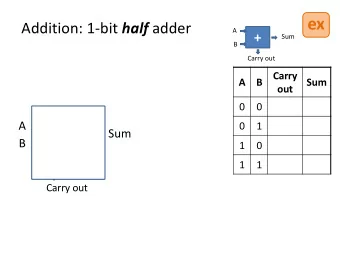

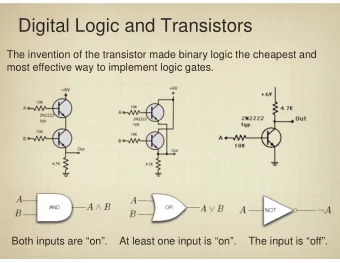

Intro Prop Res Summary Introduction The Virtex 6 basic cell. The normal adder. Large N gives long critical path. Each LUT6 controls the propagate and generate signal. 2

Intro Prop Res Summary Proposed Adder Decompose N into K LSBs and M MSBs. (cc) – K / 2 carry compr. cells (so) – K / 2 sum out cells (fa) – M normal full adder cells In total 2 K / 2 + M = N LUTs, i.e. no more than a normal adder. Optimum M = 36. The proposed approach. 3

Intro Prop Res Summary Result 5 ⋆ Normal adder ( M = N ) Critical path [ns] 4 ⋆ ⋆ M = 0 3 M = 56 M = 36 2 vs 1 0 32 64 96 128 160 192 224 256 Word length N [bits] Normal Proposed 4

Intro Prop Res Summary Summary The proposed adder architecture Twice the carry speed in parts of the adder without pipelining Same LUT count as a normal adder Efficient for long word lengths Thank you! 5

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.

![Problem 1 Design a Verilog 16-bit adder module module adder (A, B, sum); input [15:0] A, B;](https://c.sambuz.com/1025319/problem-1-design-a-verilog-16-bit-adder-module-module-s.webp)