Systems Ripple Carry Adder Shankar Balachandran* Associate - PowerPoint PPT Presentation

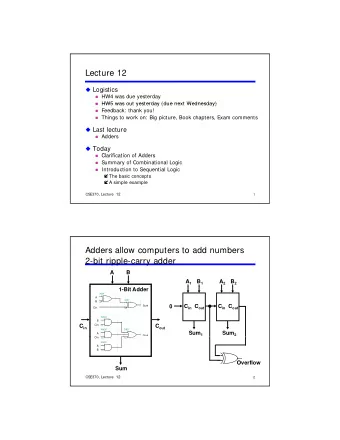

Spring 2015 Week 9 Module 50 Digital Circuits and Systems Ripple Carry Adder Shankar Balachandran* Associate Professor, CSE Department Indian Institute of Technology Madras *Currently a Visiting Professor at IIT Bombay Adders and

Spring 2015 Week 9 Module 50 Digital Circuits and Systems Ripple Carry Adder Shankar Balachandran* Associate Professor, CSE Department Indian Institute of Technology Madras *Currently a Visiting Professor at IIT Bombay

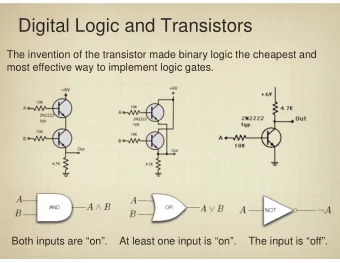

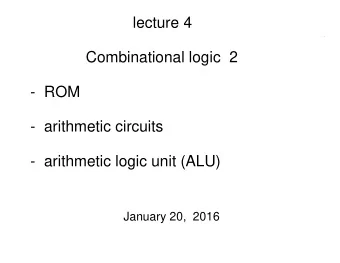

Adders and Subtracters The most basic arithmetic operation in a digital computer is addition. Half Adder is a combination circuit that performs addition of 2 bits. Inputs Outputs a b Carry Sum 0 0 0 0 Sum a b a b a b 0 1 0 1 Carry a b 1 0 0 1 1 1 1 0 Ripple Carry Adder 2

Half Adder Sum a b a b a b Carry a b Half adders cannot accept a carry input and hence it is not possible to cascade them to construct an n -bit binary adder. Ripple Carry Adder 3

Full Adder Full Adder is a combinational circuit that forms the arithmetic sum of three input bits. It is described by the following truth table: Inputs Outputs c b a C out Sum 0 0 0 0 0 0 0 1 0 1 0 1 0 0 1 0 1 1 1 0 1 0 0 0 1 1 0 1 1 0 1 1 0 1 0 1 1 1 1 1 Sum a b c a b c a b c a b c a b c C a b a c b c a b c a b out Ripple Carry Adder 4

Full Adder Implementation - 1 Sum a b c a b c a b c a b c a b c C a b a c b c a b c a b out b i a i a i s i b i Full Adder c i+1 c i (FA) c i+1 c i s i Full Adder at bit i Ripple Carry Adder 5

Full Adder Implementation - 2 A full adder can be implemented using 2 half adders and an OR gate a i s i b i c i+1 c i b i a i Full Adder c i+1 c i (FA) s i Ripple Carry Adder 6

Performance of a Full Adder Use a 2-input NAND gate implementation of a 1-bit full adder. Ripple Carry Adder 7

Ripple Carry Adder 4-bit Binary Adder: ( Sum = A + B ) A 4-bit binary adder can be implemented by cascading four 1-bit full adders as follows: Sum = ( s 3 s 2 s 1 s 0 ) Inputs: Outputs: A = ( a 3 a 2 a 1 a 0 ) B = ( b 3 b 2 b 1 b 0 ) Cout = c 4 Cin = c in = c 0 Ripple Carry Adder 8

Performance of an n -bit Ripple Carry Adder Carry ripples from input c o to output c n Worst case propagation delay for sum in terms of 2-input NAND gate delay (1 gd) is given by, n 2 t 5 2 3 5 2 n 2 3 2 n 4 sum i 1 Worst case propagation delay for carry output is given by, n 2 t delay for c 2 5 2 2 2 n 3 carry n 1 i 1 Therefore, propagation delay for an n-bit Ripple Carry Adder is O( n ). Ripple Carry Adder 9

Exercises Design a signed comparator for comparing two 4- bit 1’s complement numbers A and B If A > B, the circuit should produce 1 as output, otherwise 0 Design a signed comparator for comparing two 4-bit 2’s complement numbers A and B If A > B, the circuit should produce 1 as output, otherwise 0 Design an n - bit absolute (ABS) value generator for 2’s complement represented numbers, i.e., for an n -bit input, X , the output is | X | Ripple Carry Adder 10

End of Week 9: Module 50 Thank You Ripple Carry Adder 11

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.