MOS: Device Operation & Large Signal Model Lecture notes: Sec. - PowerPoint PPT Presentation

MOS: Device Operation & Large Signal Model Lecture notes: Sec. 4 Sedra & Smith (6 th Ed): Sec. 5.1-5.3 Sedra & Smith (5 th Ed): Sec. 4.1-4.3 F. Najmabadi, ECE65, Winter 2012 Operational Basis of a Field-Effect Transistor (1)

MOS: Device Operation & Large Signal Model Lecture notes: Sec. 4 Sedra & Smith (6 th Ed): Sec. 5.1-5.3 Sedra & Smith (5 th Ed): Sec. 4.1-4.3 F. Najmabadi, ECE65, Winter 2012

Operational Basis of a Field-Effect Transistor (1) Consider the hypothetical semiconductor below: (constructed similar to a parallel plate capacitor) Electrical contact Metal Insulator Dopent ions P-type semiconductor Holes (majority carries) F. Najmabadi, ECE65, Winter 2012

Operational Basis of a Field-Effect Transistor (2) If we apply a voltage v 1 between electrodes, a Depletion Region (no majority carrier) charge Q = C v 1 will appear on each capacitor plate. o The electric field is strongest at the interface with the insulator and charge likes to accumulate there. Holes are pushed away from the insulator interface forming a “depletion region”. Depth of depletion region increases with v 1. Inversion layer If we increase v 1 above a threshold value ( V t ), (“channel”) the electric field is strong enough to “pull” free electrons to the insulator interface. As the holes are repelled in this region, a “channel” is Depletion Region formed which contains electrons in the (no majority carrier) conduction band (“inversion layer”). Inversion layer is a “virtual” n-type material. F. Najmabadi, ECE65, Winter 2012

Operational Basis of a Field-Effect Transistor (3) We apply a voltage across the p-type semiconductor: (Assume current flows only in the n-type material, ignore current flowing in the p-type semiconductor) No inversion layer ( v 1 < V t ): With inversion layer ( v 1 > V t ): No current will flow A current will flow in the channel Current will be proportional to electron charge in the channel or ( v 1 − V t ) Magnitude of Current i 2 is controlled by voltage v 1 (a Transistor!) F. Najmabadi, ECE65, Winter 2012

Operational Basis of a Field-Effect Transistor (4) We need to eliminate currents flowing in the p-type, i.e., current flows only in the “channel” which is a virtual n-type. F. Najmabadi, ECE65, Winter 2012

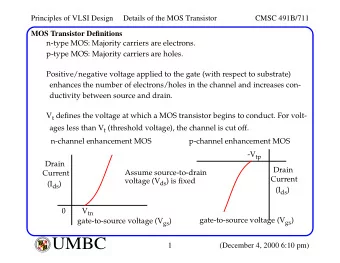

Channel width (L) is the smallest feature on the chip surface MOSFET “cartoons” for deriving MOSFET (or MOS): Metal-oxide field effect transistor MOSFET characteristics NMOS: n-channel enhancement MOS MOSFET implementation on a chip F. Najmabadi, ECE65, Winter 2012

NMOS i-v Characteristics (1) To ensure that body-source and body-drain junctions are reversed bias, we assume that Body and Source are connected to each other and v DS ≥ 0 . o We will re-examine this assumption later Without a channel, no current flows (“Cut-off”). For v GS > V tn , a channel is formed. The total charge in the channel is = = |Q| CV C WL (v -V ) ox GS tn = C C W L ox ε = ox C : Capacitanc e per unit area ox t ox t : Thickness of insulator ox ε : permitivit y of insulator ox ε = ε = × − 11 3 . 9 3 . 45 10 F/m (for SiO ) ox 0 2 F. Najmabadi, ECE65, Winter 2012

NMOS i-v Characteristics (2) v GS > V tn : a channel is formed! Apply a “small” voltage, v DS between drain & source. A current flow due to the “drift” of electrons in the n-channel: W = µ − i C ( v V ) v D n ox GS t , n DS L W = µ i C V v D n ox OV DS L Overdrive Voltage: = − V v V OV GS tn MOS acts as a resistance with its conductivity controlled by V OV (or v GS ). W = = µ i g v with g C V D DS DS DS n ox OV L F. Najmabadi, ECE65, Winter 2012

NMOS i-v Characteristics (3) When v DS is increased the channel becomes narrower near the drain (local depth of the channel depends on the difference between V OV and local voltage). Triode Mode [ ] W = µ − 2 i C V v 0 . 5 v D n ox OV DS DS L When v DS is increased further such that v DS = V OV , the channel depth becomes zero at the drain (Channel “pinched off”). When v DS is increased further, v DS > V OV , the Saturation Mode location of channel pinch-off remains close to the W = µ drain and i D remains approximately constant. 2 i 0 . 5 C V D n ox OV L F. Najmabadi, ECE65, Winter 2012

NMOS i-v Characteristics (4) For a given v GS (or V OV ) F. Najmabadi, ECE65, Winter 2012

NMOS i-v Characteristics Plot (1) NMOS i-v characteristics is a surface i = f ( v , v ) D GS DS * Plot for V t,n = 1 V and µ n C ox ( W/L ) = 2.0 m A/V 2 F. Najmabadi, ECE65, Winter 2012

NMOS i-v Characteristics Plot (2) Looking at surface with v GS axis pointing out of the paper* *Note: surface is truncated (i.e., v GS < 5 V) F. Najmabadi, ECE65, Winter 2012

NMOS i-v Characteristics Plots F. Najmabadi, ECE65, Winter 2012

Channel-Width Modulation The expression we derived for saturation region assumed that the pinch-off point remains at the drain and thus i D remains constant. In reality, the pinch-off point moves “slightly” away from the drain: Channel-width Modulation W ( ) = µ + λ 2 i 0 . 5 C V 1 v D n ox OV DS L λ = 1 / V A F. Najmabadi, ECE65, Winter 2012

Body Effect Recall that Drain-Body and Source-Body diodes should be reversed biased. o We assumed that Source is connected to the body ( v SB = 0) and v DS = v DB > 0 In a chip (same body for all NMOS), it is impossible to connect all sources to the body (all NMOS sources are connected together. Thus, the body (for NMOS) is connected to the largest negative voltage (negative terminal of the power supply). Doing so, changes the threshold voltage (called “Body Effect”) ( ) = + γ φ + − φ V V | 2 V | | 2 | tn tn , 0 F SB F In this course we will ignore body effect as well as other second- order effects such as velocity saturation. F. Najmabadi, ECE65, Winter 2012

p-channel Enhancement MOS (PMOS) A PMOS can be constructed analogous to an NMOS: (n-type body), heavily doped p-type source and drain. A virtual “p-type” channel is formed in a P-MOS (holes are carriers in the channel) by applying a negative v GS . i-v characteristic equations of a PMOS is similar to the NMOS with the exception: o Voltages are negative (we switch the terminals to have positive voltages: use v SG instead of v GS ). o Use mobility of holes, µ p , instead of µ n in the expression for i D F. Najmabadi, ECE65, Winter 2012

MOS Circuit symbols and conventions NMOS PMOS F. Najmabadi, ECE65, Winter 2012

MOS i-v Characteristics Equations: i D ( v GS , v DS ) & i G = 0 NMOS ( V OV = v GS – V tn , λ = 1 / V A ) ≤ = Cut - Off : V 0 i 0 OV D [ ] W ≥ ≤ = µ − 2 Triode : V 0 and v V i 0 . 5 C 2 V v v OV DS OV D n ox OV DS DS L W [ ] ≥ ≥ = µ + λ 2 Saturation : V 0 and v V i 0 . 5 C V 1 v OV DS OV D n ox OV DS L PMOS ( V OV = v SG – | V tp |, λ = 1 / | V A | )* ≤ = Cut - Off : V 0 i 0 OV D [ ] W ≥ ≤ = µ − 2 Triode : V 0 and v V i 0 . 5 C 2 V v v OV SD OV D p ox OV SD SD L [ ] W ≥ ≥ = µ + λ 2 Saturation : V 0 and v V i 0 . 5 C V 1 v OV SD OV D p ox OV SD L *Note: S&S defines | V OV |= v SG – | V t,p | and uses | V OV | in the PMOS formulas. F. Najmabadi, ECE65, Winter 2012

MOS operation is “Conceptually” similar to a BJT -- i D & v DS are controlled by v GS Controlled part: i D & v DS are set by transistor state (& outside circuit) Controller part: Circuit connected to GS sets v GS (or V OV ) A similar solution method to BJT: o Write down GS-KVL and DS-KVL, assume MOS is in a particular state, solve with the corresponding MOS equation and validate the assumption. MOS circuits are simpler to solve because i G = 0 ! However, we get a quadratic equation to solve if MOS in triode (check MOS o in saturation first!) F. Najmabadi, ECE65, Winter 2012

Example 1: In the circuit below, R D = 1 k, and V DD = 12 V. Compute v o for v i = 0, 6, and 12 V. ( µ n C ox ( W/L ) = 0.5 mA/V 2 , V t = 2 V, and λ = 0 ) = GS - KVL : v v i GS v = o v = = + = + DS 3 DS - KVL : V 12 R i v 10 i v DD D D DS D DS Part 1: v i = 0 = = < = → → = GS - KVL : v v 0 V 2 V Cut - off i 0 i GS t D = × + → = = 3 DS - KVL : 12 10 0 v v v 12 V DS o DS Part 2: v i = 6 V − = = > = → GS KVL : v v 6 V 2 V Not in Cut - off i GS t = − = V v V 4 V OV GS t ≥ = Assume Saturation : v V 4 V DS OV W − = µ = × × × = 2 3 2 i 0 . 5 C V 0 . 5 0 . 5 10 4 4 . 0 mA D n ox OV L = × × − + → = = 3 3 DS - KVL : 12 10 4 10 v v v 8 . 0 V DS o DS = > = → v 8 . 0 V V 4 V Assumption correct DS OV F. Najmabadi, ECE65, Winter 2012

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.