Lumped Element High Voltage MOS Model presented by Sebastian - PowerPoint PPT Presentation

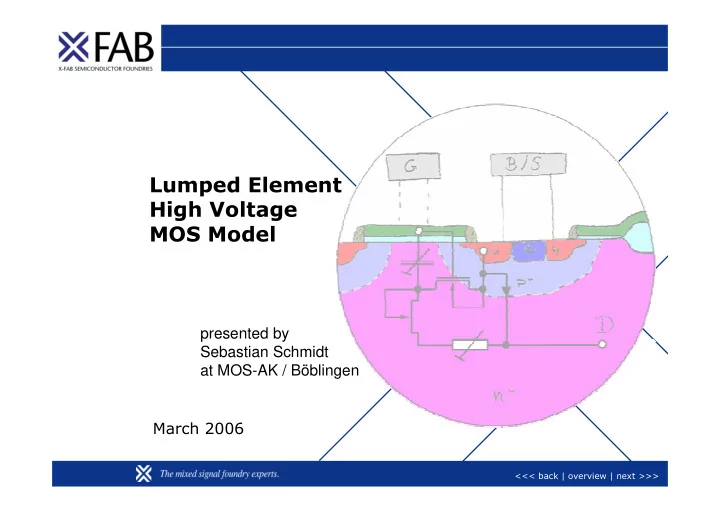

Lumped Element High Voltage MOS Model presented by Sebastian Schmidt at MOS-AK / Bblingen March 2006 <<< back | overview | next >>> Devices DC Model AC Model Test Bench Outlook Agenda (1) > > The Devices:

Lumped Element High Voltage MOS Model presented by Sebastian Schmidt at MOS-AK / Böblingen March 2006 <<< back | overview | next >>>

Devices DC Model AC Model Test Bench Outlook Agenda (1) > > The Devices: Types and Construction > DC Model: Mathematical considerations, types > AC Model: Non diode variable "gate" capacitance > Ring Oscillator Test Bench: A challenge for the simulator > Outlook 2 <<< back | overview | next >>>

Devices DC Model AC Model Test Bench Outlook Introduction > The goal is to show an extension to the BSIM3v3 model which can be simulated by a standard Spice simulator. > At the time of development a VerilogA formulation was not intended. > The model shows a more accurate description of the so called quasi saturation effect. > A better description of the LDDMOS drain overlap capacitance is considered. 3 <<< back | overview | next >>>

Devices DC Model AC Model Test Bench Outlook High Voltage Drain Extension MOS Cross Section SOURCE GATE DRAIN BULK P-WELL Si depth / µm N-WELL - 1E20 - 1E18 - 1E16 - 1E14 - 1E12 P-SUB position / µm watch the scaling 4 <<< back | overview | next >>>

Devices DC Model AC Model Test Bench Outlook Two Types of Drain Extension MOS Extension region at drain Circuit with drain resistance and parasitic elements (BJT, substrate resistance) Name: Extended Drain MOS XDMOS N-Well as drain extension 5 <<< back | overview | next >>>

Devices DC Model AC Model Test Bench Outlook Two Types of Lateral Diffused Drain MOS Diffused drain with lateral drain connection Name: LDDMOS or LDMOS Diffused drain with vertical drain connection XD_10 with up to 650 V LDMOS transistors Trench 6 <<< back | overview | next >>>

Devices DC Model AC Model Test Bench Outlook Agenda (2) > The Devices: Types and Construction > > DC Model: Mathematical considerations, types > AC Model: Non diode variable "gate" capacitance > Ring Oscillator Test Bench: A challenge for the simulator > Outlook 7 <<< back | overview | next >>>

Devices DC Model AC Model Test Bench Outlook First Generation HV MOS Model > MOS transistor with serial resistor VGS/V The model does not 12.0 take into account the quasi saturation effect. 9.67 G 7.33 Rds 5.0 D S MOS BSIM3V3 2.67 - good model accuracy for low gate voltages - drain current saturation effect at high VGS and VDS not included - fast simulation speed and good convergence 8 <<< back | overview | next >>>

Devices DC Model AC Model Test Bench Outlook Second Generation Behavioural HV MOS > MOS transistor with serial resistor and VGS/V voltage controlled voltage source 12.0 The quasi saturation is modeled with acceptable accuracy (green). 9.67 7.33 G Rds 5.0 D S MOS 2.67 BSIM3V3 - core devices MOS and Rds identical to HV model - several parameters for VCVS added - good model accuracy, error less than 10% - higher simulation time - simulation convergence problems more likely 9 <<< back | overview | next >>>

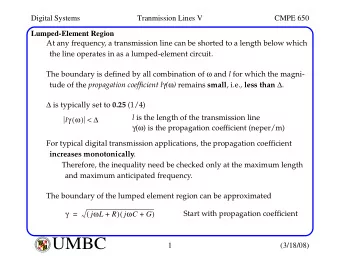

Devices DC Model AC Model Test Bench Outlook Function Requirement for the Voltage Source > Demands on the behavioral current function: – The function should be monotone (not necessarily). – The first and second derivative must be continuous. Function needed for the voltage source: R d Function Voltage drop @ resistor. 10 <<< back | overview | next >>>

Devices DC Model AC Model Test Bench Outlook Implementation: Controlled Voltage Source > Improved accuracy has its price: 3 auxiliary networks, 7 parameters, several additional elements 1f 8 9 g R d d s + - b evd evd = max(sgn(v(d,s)),0) * max(sgn(v(g,s)),0) * min(v(7)*v(6),v(d,s)) > Auxiliary Networks: main formula 5 TC network + - ev5 1M 6 + 7 R=1k ev - 1M tc1 =5.5E-3 0 tc2 =1.2E-5 ev5 = v(d,9) / ( v(7) + 1E-6 ) 0 0 ev = ( kp3 v(5) 3 + kp4 v(5) 4 + kp5 v(5) 5 ) * f( v(g,s),k1h,kgs ) * f limit ( v(d,s),kds ) 11 <<< back | overview | next >>>

Devices DC Model AC Model Test Bench Outlook Current Source Behavioural HV MOS > MOS transistor with serial resistor and voltage controlled current source 2 12 11 1 3 BSIM3v3 - core devices MOS and Rds identical to HV model - added fly back diode due to device construction - improved accuracy compared to the voltage source model - shorter simulation time - capacitance modeling difficult in case of LDDMOS 12 <<< back | overview | next >>>

Devices DC Model AC Model Test Bench Outlook Function Requirements for the Current Source The function for the current in the drain extension region Variations ... Resulting resistance must 13 <<< back | overview | next >>>

Devices DC Model AC Model Test Bench Outlook Behavioural Current Source Model > Less auxiliary sources, improved TC modeling. > More compact model, all effects in a few equations. > Improved convergence, fewer parameter (5). v(11,12) g I ( g11 ) = 1+ v(11,12) 2 / v(101) 2 v(102) * 1+ 2 1G 101 Gate Voltage influence: 1 I =f(v(2,3), a , b , c ) * v(102) 0 1f d R01 s 1 102 11 12 R=1 tc1' I = R02 g11 TC 3 tc1,tc2 tc2' 0 14 <<< back | overview | next >>>

Devices DC Model AC Model Test Bench Outlook Gm and Transconductance Example Id [1E-3] red: measured green: simulated 15 <<< back | overview | next >>>

Devices DC Model AC Model Test Bench Outlook Gds and Ron accuracy Ron.s [E+0] Ron.m Gds.s [E-3] Gds.m 16 <<< back | overview | next >>>

Devices DC Model AC Model Test Bench Outlook Self Heating > The below plot shows clear self heating: a "falling" current trace in the saturation region > To include this effect into the model, it needs a temperature node and additionaly ... > A thermal resistance / capacitance network. It's not yet implemented in the model. 17 <<< back | overview | next >>>

Devices DC Model AC Model Test Bench Outlook Introduction to Self Heating > Simple thermal network added for self heating: – Voltage [V] = Temperature [K] ^ – Current [I] = Thermal Current [J/s=W] ^ – Resistance [ Ω ] = Thermal Resistance [K/W] ^ – Capacitance [C/V] = Thermal Capacitance [J/K] ^ – Charge [C] = Energy [J=Ws] ^ > The thermal power equals the electrical power loss. Thermal T=V th R th -Dev Network R th -out P el-loss = I thermal C th -out 1G C th -Dev Thermal Node: this voltage goes Ambient + + - Device - into the formulas Temperature Temperature as temperature. 0 0 18 <<< back | overview | next >>>

Devices DC Model AC Model Test Bench Outlook Agenda (3) > The Devices: Types and Construction > DC Model: Mathematical considerations, types > > AC Model: Non diode variable "gate" capacitance > Ring Oscillator Test Bench: A challenge for the simulator > Outlook 19 <<< back | overview | next >>>

Devices DC Model AC Model Test Bench Outlook The Drain Overlap Capacitance Problem BULK/SOURCE GATE DRAIN A capacitance, which P-WELL depends strongly from the drain voltage, BULK/SOURCE GATE DRAIN Si depth / µm N-WELL develops if the gate overlaps the drain P-WELL extension region. Si depth / µm N-WELL - 1E20 This is true for the - 1E18 LDDMOS type MOS - 1E16 with Trench isolation. - 1E14 - 1E12 Fortunately it does - 1E20 not occur in the - 1E18 position / µm - 1E16 standard CMOS - 1E14 technologies, - 1E12 e.g. xc06. position / µm 20 <<< back | overview | next >>>

Devices DC Model AC Model Test Bench Outlook LDDMOS Capacitance Model > For the LDDMOS of the XD?10 technology a (variable) capacitance has to be added in the drain to gate path. > It can not be decided by CV measurement which node has to be occupied to get a good fitting transient respond. 2 ? ? ? 3 1 12 11 D BSIM3v3 21 <<< back | overview | next >>>

Devices DC Model AC Model Test Bench Outlook Improved CV Model This model is not yet implemented in X-FAB's HV models, ongoing work. This is the drain/gate overlap capactance, drain overlap which has a diode w/o channel like CV trace this is the reverse diode, which is easily modeled constant cap @ drain (purple) improved model (green) 22 <<< back | overview | next >>>

Devices DC Model AC Model Test Bench Outlook Drain Voltage dependent Capacitance Model g > The capacitance is modeled in an auxiliary circuit. The current is mirrored back into the current I cgd C gd 1 2 controlled current source between 1G the drain and gate node. > This is fine for stand alone AC 1f simulation but proved as not d R01 s 1 converging in the ring oscillator test. 11 12 g11 1 3 Dcgd D1 Cgd Cgd2 An alternative model is in development. + + - V=v(2,1) - 0V 1 D2 It uses function controlled I cgd sources instead of diodes to 0 modulate the CV characteristic. constant part accumulating 23 <<< back | overview | next >>>

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.