Introduction to Digital VLSI Design - PowerPoint PPT Presentation

Introduction to Digital VLSI Design VLSI Extraction Lecturer: Gil Rahav Semester B , EE Dept. BGU. Freescale Semiconductors Israel Introduction to Digital VLSI Slide 1

Introduction to Digital VLSI Design �יתר�פס� � ��ו�נכ�ת�ל�אובמ VLSI Extraction Lecturer: Gil Rahav Semester B’ , EE Dept. BGU. Freescale Semiconductors Israel Introduction to Digital VLSI Slide 1

Extraction • Extraction is a process of creating electrical representation (R&C) for layout interconnect Resistance & Capacitance • Extraction could be done in two ways: 1. transistor level extraction 2. cell level extraction Introduction to Digital VLSI Slide 2

Delay calculation Total delay = device delay + interconnect delay + slew rate Introduction to Digital VLSI Slide 3

Basic concepts Capacitance • Area (overlap) • Fringe (edge) • Nearbody (coupling) Introduction to Digital VLSI Slide 4

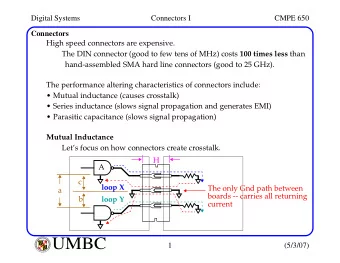

Parasitic Extraction What is parasitic capacitance? • Electrical side effect depends on the shape of the signal and its neighborhood. • Parasitic capacitance occurs both between geometries on a single layer and between geometries on different layers. Introduction to Digital VLSI Slide 5

What is parasitic resistance? • Electrical side effect depend on the shape of the signal and resistivity of the interconnect layer Introduction to Digital VLSI Slide 6

Grounding coupling capacitors 20 pF 20 pF 20 pF RC representation: 1. C (lumped C) 2. RC (distributed RC) 3. RCC (distributed RC + coupling) Introduction to Digital VLSI Slide 7

Layout formats • GDSII (stream) raw geometrical shapes • LEF / DEF geometric shapes + netlist Introduction to Digital VLSI Slide 8

GDSII format • Raw geometric shapes (polygons, paths) at diffrenet layers • Texts (net names, pin names) at different layers • Cell instances Available: • Always Connectivity: • Requires connectivity analysis and LVS Introduction to Digital VLSI Slide 9

LEF (abstract) • Cell boundary • Cell pins with names and locations • Obstructions (used routing area) Introduction to Digital VLSI Slide 10

DEF • Represents one level of layout • Netlist, pins locations, cells placement, routing annotated per net • Connectivity • All the information embedded inside the LEF/DEF; no need for special processing � Available from automatic P&R tools Introduction to Digital VLSI Slide 11

RC Formats • DSPF (= SPF) – most often used • SPEF • SPICE • SBPF (for PrimeTime only) Introduction to Digital VLSI Slide 12

DSPF • resistance and line capacitance of each segment in a net in a SPICE format Non SPICE statements: • *|NET NetName NetCap • *|I (InstancePinName InstanceName PinName PinType PinCap X Y) • *|P (PinName PinType PinCap X Y) • *|S (SubNodeName X Y) Introduction to Digital VLSI Slide 13

Net name and *|NET cpm_ips_rdata[2] 0.129244PF total capacitance Port node *|P (cpm_ips_rdata[2] O 0 834.39 -0.27) *|I (sba_env:cpm_ips_rdata[2] sba_env cpm_ips_rdata[2] B 0 317.67 90) Net nodes Instance pin *|I (sbs_env/sbs_top:sbs_ips_rdata[2] *+ sbs_env/sbs_top sbs_ips_rdata[2] B 0 156.51 90) *|S (cpm_ips_rdata[2]:9) Subnode Cg1540 sba_env:cpm_ips_rdata[2] 0 1.16035e-14 Cg1541 cpm_ips_rdata[2] 0 5.46695e-14 Capacitors Cg1542 cpm_ips_rdata[2]:9 0 1.1831e-14 Cg1543 sbs_env/sbs_top:sbs_ips_rdata[2] 0 5.114e-14 R1189 cpm_ips_rdata[2]:9 sbs_env/sbs_top:sbs_ips_rdata[2] 30.2 Resistors R1190 sba_env:cpm_ips_rdata[2] cpm_ips_rdata[2]:9 11.34 R1191 cpm_ips_rdata[2] cpm_ips_rdata[2]:9 25.8727 sba_env:cpm_ips_rdata[2] cpm_ips_rdata[2] sbs_env/sbs_top:sbs_ips_rdata[2] Introduction to Digital VLSI Slide 14

Extraction tools • xCalibre (GDSII) • Calibre2Star (GDSII) • StarXT (LEF / DEF) Introduction to Digital VLSI Slide 15

Target tools • Timing Analysis tools (Cell and Trasistor Level) • Noise • Power grid • Circuit Verification Tools Introduction to Digital VLSI Slide 16

The Flows – Cell Level • Transistor level extraction on GDSII • LVS required • Usually extract capacitance only • Used for characterization, or in transistor level analysis tool with cell level block extraction Introduction to Digital VLSI Slide 17

The Flows – Block Level Transistor Cell level level Transistor Transistor level level Introduction to Digital VLSI Slide 18

Chip level • extraction on LEF/DEF down to block boundaries • no LVS required • extract RC • extraction tool - StarXt • analysis tool - PrimeTime • backannotation - no need • reduction - done on-the-fly • need to define context to model inside blocks routing if obstructions do not exist Introduction to Digital VLSI Slide 19

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.