Objectives VLSI technology trend Design challenges Custom and - PowerPoint PPT Presentation

Objectives VLSI technology trend Design challenges Custom and semi-custom VLSI System-on-a-Chip and IPs Design domain and perspective Design tasks Design flow One of the most important indicators in measuring the

• Objectives – VLSI technology trend – Design challenges – Custom and semi-custom VLSI – System-on-a-Chip and IPs – Design domain and perspective – Design tasks – Design flow

• One of the most important indicators in measuring the level of VLSI advancement is the so-called feature size. – It indicates how fine a process can be achieved in producing a geometric component in a chip, for instance, the separation between two interconnects or the width of a wire segment. • A more proper measurement, half-pitch, is adopted on the roadmap of IC development. – Although this measurement is more specific for the layer or the type of the device, providing a more accurate measure of the technology, there is no fundamental difference from the traditional notion of the feature size.

• Definition of pitches (ITRS, 2009)

• Improvement trends for ICs enabled by feature size scaling (ITRS, 2009)

• Most of these trends have resulted from the industry’s ability to exponentially decrease the minimum feature size (or half-pitch) used to fabricate integrated circuits. • Another frequently cited trend is the level of integration, which is usually expressed as Moore’s Law (the number of components per chip doubles roughly every 18 months).

• The penetration of IC into our lives has brought many new varieties of applications, which cannot be encompassed by Moore’s Law. • Moore’s Law measures the number of devices in a chip, but it can hardly describe the variety of chips and systems built upon them. • In the past decade, the development of System-on-a-chip and System-in-Package ( SiP ) technologies has greatly increased the capability of integration, and further broadened the IC application.

• As far as the number of the devices integrated into a chip is concerned, the major enabler is CMOS technology, despite being considered a “die-hard” technology. • In the nanometer regime, such as with the 22 nm process, the accuracy of lithography has reached a fraction of the light wavelength. • Further improvement has been limited by the laws of physics. As such, there is a great concern about the situation “beyond CMOS”. • At the moment, the answer to this question is still unclear.

• The ITRS roadmap has been considered the most complete and accurate open source information for the research and development (R&D) of integrated circuits and the IC industry’s future trends. – ITRS updates its roadmap regularly and the roadmap can be found on its website. • People in this area should visit this site regularly to obtain information on state-of-the-art IC technology.

• VLSI design is no longer a pure hardware issue, and also involves software development.

• The previous figure shows the cost comparison between hardware and software development spent in each categories. • Hardware and software co-design has been necessary in most advanced digital system development, especially in the development of SoC where high level IPs, different type functional blocks, system protocols and operation systems need to be realized in a single chip. • SoC provides a platform for extending Moore’s law in the dimension of diversity.

• An SoC consists of not only a collection of hardware blocks, such as a microcontroller, microprocessor or DSP cores, peripherals and interfaces, but also the software which control these hardware blocks. • Most SoCs are developed from pre-qualified hardware blocks for the hardware elements along with the software drivers that control their operations. • The hardware blocks are put together using CAD tools; the software modules are integrated using a software development environment.

• Microcontroller- based system-on- a-chip

• SoC design flow is much more complicated than a traditional IC design process. – Hardware and software co-design is heavily involved. – In many cases the IPs come from different IC vendors and the model and interface protocols are often inconsistent with each other. – Signals usually have to pass through several clock domains, which in turn requires very cautious design.

• A custom designer in principle can end up designing most circuit blocks from scratch for a particular application. – Considering the work involved in logic, circuit, layout, and verification, this would easily result in a very long design cycle and high design cost. • To reduce the design cycle and cost, semi-custom design methodology was introduced. – With this method, some or all components are pre-designed or even pre-fabricated such that design effort for an application can be shifted to a higher level.

• Custom and semi-custom designs

• Gate Array – Gate array is a widely used approach for the design and manufacture of ASICs. – A gate array circuit is a prefabricated chip with no particular function, in which transistors, standard NAND or NOR logic gates, and other active devices are placed at regular predefined array positions and manufactured on a wafer, usually called a master slice. – Creation of a circuit for a specified function is accomplished by adding a few layers of metal interconnects on top of the master slice late in the manufacturing process, joining the elements in the array cells to allow the function of the chip to be customized as desired

– Gate array master slices, usually in several families containing different number of logic gates, are prefabricated in large quantities regardless of customer orders. – The design and fabrication according to the individual customer specifications may be finished in a shorter time compared with a full custom design, because there is no need to design the low level masks for the transistors. – The gate array approach reduces the mask costs because fewer custom masks need to be produced. – In addition, manufacturing test tooling lead time and costs are reduced since the same test fixtures may be used for all gate array products manufactured on the same die size.

• A view of gate array and its cells

• Standard Cell – When the adjacent gate array cells are pushed one against the other horizontally and the vertical channels between them diminish, the result is a standard cell technology. – Standard cell works very much the same way as the gate array, and currently it is not distinguished from gate array without specific need.

• A view of standard cell technology

• Cell library – ASIC foundries will provide a technology library of cells, which contains multiple implementations of the same logic function that differ in area and speed. – The cells in the library are characterized and modeled in detail in terms of speed, power consumption, fan-in and fan-out limit, geometric shape and size, etc. – The variety found in the cell library enhances the efficiency of automated synthesis, place and route (SPR) tools. It also gives the designer more freedom to perform implementation tradeoffs, such as area vs. speed vs. power consumption. – The technology library, along with a design netlist format, is the basis for exchanging design information between different phases of the SPR process.

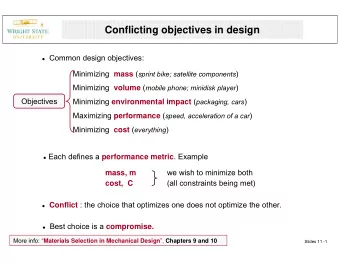

• Synthesis – The logic synthesis tool maps the ASIC's register-transfer level (RTL) description into a technology dependent netlist. – The netlist is the standard cell representation of the ASIC design at the logical view level. It consists of instances of the standard cell library gates and port-connectivity between gates. – Proper synthesis techniques ensure logical equivalency between the synthesized netlist and the original RTL description. – During the mapping process certain optimization objectives are considered, such as the signal delay constraint or usage of the minimal number of gates.

• Placement – The placement tool starts the physical implementation of the ASIC. • The placement tool assigns locations for each gate in the netlist. • The resulting placed gates netlist contains the physical location of each of the standard cells in the netlist, but retains an abstract description of how the gates’ terminals are wired to each other. – Typically the standard cells have a constant size in at least one dimension that allows them to be lined up in rows on the integrated circuit. • Such arrangement greatly eases the complexity of the layout, since the size difference of the cells are accommodated by the cell width and routing can be done in a simple rectangular channel.

• Technology mapping and placement of standard cells

• Routing – Using the placed gates netlist and the layout view of the library, the router adds both signal connect lines and power supply lines. – The fully routed physical netlist contains the listing of gates from synthesis, the placement of each gate from placement, and the drawn interconnects from routing.

• The following figure is a standard cell layout example, in which there are two metal layers indicated by pink and blue respectively.

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.