EE 109 Unit 10 MIPS Instruction Set MIPS INSTRUCTION OVERVIEW - PowerPoint PPT Presentation

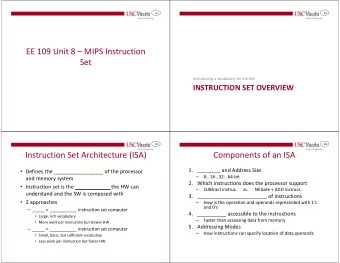

10.1 10.2 EE 109 Unit 10 MIPS Instruction Set MIPS INSTRUCTION OVERVIEW 10.3 10.4 Instruction Set Architecture (ISA) MIPS Processor and Bus Interface The MIPS processor can execute software instructions that will Defines the

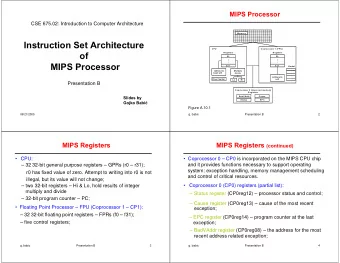

10.1 10.2 EE 109 Unit 10 – MIPS Instruction Set MIPS INSTRUCTION OVERVIEW 10.3 10.4 Instruction Set Architecture (ISA) MIPS Processor and Bus Interface • The MIPS processor can execute software instructions that will • Defines the _________________ of the processor cause it to: and memory system – Load (Read) and Store (Write) data to and from memory or I/O devices • Instruction set is the ____________ the HW can – Perform arithmetic and logic operations (add, sub, and, etc.) understand and the SW is composed with – Make decisions to move around in the code (loops, ifs, call a function, etc.) • 2 approaches MIPS Processor Memory – _____ = ___________ instruction set computer PC Addr (32-bits) instruc 0 • Large, rich vocabulary op. • More work per instruction but slower HW ALU ADD, out in1 – _____ = ___________ instruction set computer SUB, Data (32-bits) AND, • Small, basic, but sufficient vocabulary in2 OR • Less work per instruction but faster HW (32-bits ALU) $0-$31 Control (32-bits each) data

10.5 10.6 Which Instructions MIPS Instruction Set • __________-style • In this class we'll focus on assembly to do the following • ______________ internal / __________ external data size tasks (shown with the corresponding MIPS assembly – Registers and ALU are 32-bits wide mnemonics) – Memory bus is logically 32-bits wide (though may be physically – Load variables (data) from memory (or I/O) [LW,LH,LB] wider) • Registers – Perform arithmetic, logical, and shift instructions in the CPU – ______ General Purpose Registers (GPR’s) [ADD,SUB,AND,OR,SLL,SRL,SRA] • For integer and address values – Store variables (data) back to memory after computation is • A few are used for specific tasks/values complete [SW, SH, SB] • Fixed size instructions – Compare data [SLT] – All instructions encoded as a single ______-bit word – "Branch" to other code (to implement if and loops) – Three operand instruction format (dest, src1, src2) – Load/store architecture (all data operands must be in registers and [BEQ,BNE,J] thus loaded from and stored to memory explicitly) – Call subroutines/functions [JAL, JR] 10.7 10.8 MIPS GPR’s MIPS Programmer-Visible Registers Assembler Name Reg. Number Description • General Purpose Registers GPR’s (GPR’s) $zero $0 Constant 0 value $0 - $31 – Hold data operands or $at $1 Assembler temporary addresses (pointers) to data $v0-$v1 $2-$3 Procedure return values or expression stored in memory evaluation • Special Purpose Registers $a0-$a3 $4-$7 Arguments/parameters – ___: ____________ ___(32-bits) $t0-$t7 $8-$15 Temporaries • Holds the address of the next 32-bits $s0-$s7 $16-$23 Saved Temporaries instruction to be fetched from memory & executed $t8-$t9 $24-$25 Temporaries PC: – HI: Hi-Half Reg. (32-bits) $k0-$k1 $26-$27 Reserved for OS kernel • For MUL, holds 32 MSB’s of Recall multiplying two 32-bit result. For DIV, holds 32-bit numbers yields a 64-bit result $gp $28 Global Pointer (Global and static remainder HI: variables/data) – LO: Lo-Half Reg. (32-bits) $sp $29 Stack Pointer LO: • For MUL, holds 32 LSB’s of $fp $30 Frame Pointer result. For DIV, holds 32-bit MIPS Core quotient $ra $31 Return address for current procedure Special Purpose Registers Avoid using the yellow (highlighted) registers for anything other than its stated use

10.9 10.10 R-Type Arithmetic/Logic Instructions C operator Assembly Notes + ADD $d, $s, $t d=destination, s = src1, t = src2 - SUB $d, $s, $t Order: $s – $t. SUBU for unsigned * MUL $d, $s, $t If multiply won’t overflow 32-bit result & AND $d, $s, $t | OR $d, $s, $t ^ XO$ $d, $s, $t ~( | ) NOR $d, $s, $t Can be used for bitwise-NOT (~) << SLL $d, $s, shamt Shifts $s left by shamt (shift amount) SLLV $d, $s, $t or $t bits Performing Arithmetic, Logic, and Shift Operations >> (signed) SRA $d, $s, shamt Shifts $s right by shamt or $t bits IMPORTANT R-TYPE INSTRUCTIONS SRAV $d, $s, $t replicating sign bit to maintain sign >> (unsigned) SRL $d, $s, shamt Shifts $s left by shamt or $t bits SRLV $d, $s, $t shifting in 0’s <, >, <=, >= SLT $d, $s, $t Comparison. Order: $s – $t. Sets SLTU $d, $s, $t $d=1 if $s < $t, $d=0 otherwise * MULT $s, $t Result in HI/LO. Use mfhi and mflo MULTU $s, $t instruction to move results / DIV $s, $t $[s] / $[t]. DIVU $s, $t Remainder in HI, quotient in LO 10.11 10.12 R-Type Instructions R-Type Instructions • To perform arithmetic or logic operations in many processors (MIPS included) a copy of the operand MUST be loaded into a register first • Format • Consider the following operations C Code MIPS Assembly 6-bits 5-bits 5-bits 5-bits 5-bits 6-bits – F = X + Y – Z LOAD* $4, X # Get X from mem. F = X + Y – Z; – G = F | Z opcode rs (src1) rt (src2) rd (dest) shamt function LOAD _____ # Get Y from mem. G = F | Z; • Complete the assembly code LOAD _____ # Get Z from mem. ADD _______ # Tmp = X+Y to perform these operations – rs, rt, rd are 5-bit fields for register numbers SUB _______ # Tmp = Tmp - Z – Remember to load/store your STORE _______ # Store to F in mem – shamt = shift amount and is used for shift instructions operands to/from registers OR _______ # Tmp2 = F | Z STORE $8, G # Store to G in mem indicating # of places to shift bits * LOAD/STORE are not actual instructions. We will learn the actual syntax soon. – opcode and func identify actual operation (e.g. ADD, SUB) Memory Load 00400000 Load MIPS Processor 00400004 • Example: op. … ALU $4 PC Store – ADD $5, $24, $17 $5 ADD, out in1 Addr (32-bits) SUB, $6 X (e.g. 12) 10010000 AND, $7 opcode rs rt rd shamt func Y (e.g. 7) 10010004 Data (32-bits) in2 OR $8 Z (e.g. 3) 000000 00000 100000 (32-bits ALU) $0-$31 F Control Arith. Inst. $24 $17 $5 unused ADD (32-bits each) G

10.13 10.14 Logical Operations Logical Operations • Should already be familiar with (sick of) these! ☺ ☺ ☺ ☺ • Logic operations on numbers means performing the operation on each pair of bits • Logic operations are usually performed on a pair of bits Initial Conditions: $1 = 0xF0, $2 = 0x3C X1 X2 AND X1 X2 OR X1 X2 XOR X1 NOT 0 0 0 0 0 0 0 0 0 0 1 1 AND $2,$1,$2 0xF0 1111 0000 AND 0x3C AND 0011 1100 0 1 0 0 1 1 0 1 1 1 0 R[2] = 0x30 0x30 0011 0000 1 0 0 1 0 1 1 0 1 1 1 1 1 1 1 1 1 0 2 OR $2,$1,$2 0xF0 1111 0000 OR 0x3C OR 0011 1100 OR – Output is true XOR – Output is NOT – Output AND – Output is R[2] = 0xFC 0xFC 1111 1100 true if both inputs if any input is true true if exactly one is inverse of input is true input are true XOR $2,$1,$2 0xF0 1111 0000 3 0 AND x = 0 0 OR x = x 0 XOR x = x XOR 0x3C XOR 0011 1100 1 AND x = x 1 OR x = 1 1 XOR x = NOT x R[2] = 0xCC 0xCC 1100 1100 x AND x = x x OR x = x x XOR x = 0 Tip: Unless you're very good w/ hex, convert to binary then perform these operations! 10.15 10.16 Logical Operations Shift Operations • Shifts data bits either left or right • Logic operations on numbers means performing the – Bits shifted out and dropped on one side operation on each pair of bits – Usually (but not always) 0’s are shifted in on the other side • In addition to just moving bits around, shifting is a fast way to Initial Conditions: $1= 0xF0, $2 = 0x3C multiply or divide a number by ____________(see next slides) 4 NOR $2,$1,$2 0xF0 1111 0000 • 2 kinds of shifts NOR 0x3C NOR 0011 1100 – Logical shifts (used for __________________ numbers) R[2] = 0x03 0x03 0000 0011 – Arithmetic shifts (used for _________________ numbers) Bitwise NOT operation can be performed by NOR’ing register with itself Right Shift by 2 bits: Left Shift by 2 bits: 0 0 0 0 1 1 0 0 0 0 0 0 1 0 1 0 NOR $2,$1,$1 0xF0 1111 0000 NOR 0xF0 NOR 1111 0000 Original Data Original Data R[2] = 0x0F 0x0F 0000 1111 0’s shifted in… 0’s shifted in… 0 0 0 0 0 0 1 0 1 0 0 0 0 0 0 0 0 0 1 1 Shifted by 2 bits Shifted by 2 bits

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.