Digital Logic CombinaAonal Circuits 2 Homework Notes - PowerPoint PPT Presentation

Computer Systems and Networks ECPE 170 Jeff Shafer University of the Pacific Digital Logic CombinaAonal Circuits 2 Homework Notes

ì ¡ Computer ¡Systems ¡and ¡Networks ¡ ECPE ¡170 ¡– ¡Jeff ¡Shafer ¡– ¡University ¡of ¡the ¡Pacific ¡ Digital ¡Logic ¡ CombinaAonal ¡Circuits ¡

2 ¡ Homework ¡Notes ¡ ì Homework ¡5 ¡and ¡6 ¡ ì Paper ¡submissions ¡accepted ¡for ¡these ¡assignments ¡ (since ¡it ¡involves ¡drawing ¡circuits ¡and ¡Karnaugh ¡ Maps…) ¡ Computer ¡Systems ¡and ¡Networks ¡ Spring ¡2012 ¡

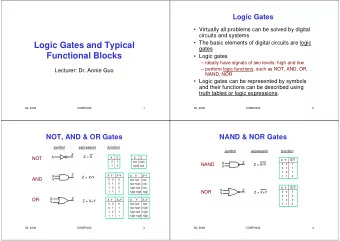

3 ¡ Implementing ¡Boolean ¡Functions ¡ ì How ¡do ¡we ¡ physically ¡implement ¡Boolean ¡funcAons? ¡ Using ¡digital ¡computer ¡circuits ¡called ¡ gates ¡ ì ì What ¡is ¡a ¡gate? ¡ Electronic ¡device ¡that ¡produces ¡a ¡result ¡based ¡on ¡two ¡or ¡ ì more ¡input ¡values ¡ Built ¡out ¡of ¡1-‑6 ¡transistors ¡(but ¡we’ll ¡treat ¡a ¡gate ¡as ¡a ¡ ì single ¡fundamental ¡unit ¡in ¡this ¡class) ¡ ì Integrated ¡circuits ¡contain ¡gates ¡organized ¡to ¡ accomplish ¡a ¡specific ¡task ¡ Computer ¡Systems ¡and ¡Networks ¡ Spring ¡2012 ¡

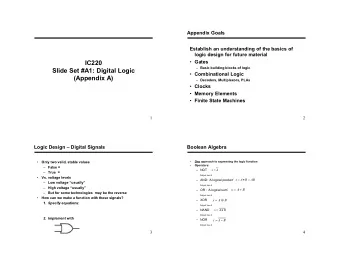

4 ¡ Gates: ¡AND, ¡OR, ¡NOT ¡ AND ¡Gate ¡ OR ¡Gate ¡ NOT ¡Gate ¡ Look ¡at ¡the ¡NOT ¡gate: ¡The ¡ ¢ ¢ ¡symbol ¡represents ¡“NOT”. ¡You’ll ¡see ¡it ¡on ¡other ¡gates ¡ Computer ¡Systems ¡and ¡Networks ¡ Spring ¡2012 ¡

5 ¡ Gates: ¡XOR ¡ Exclusive ¡OR ¡(XOR) ¡ ì The ¡output ¡of ¡the ¡XOR ¡ operaAon ¡is ¡ true ¡only ¡when ¡ the ¡values ¡of ¡the ¡ inputs ¡are ¡ different ¡ ì Note ¡the ¡special ¡symbol ¡ ⊕ ¡ for ¡the ¡XOR ¡operaAon. ¡ Computer ¡Systems ¡and ¡Networks ¡ Spring ¡2012 ¡

6 ¡ Gates: ¡NAND, ¡NOR ¡ NAND ¡(AND ¡w/NOT) ¡ NOR ¡(OR ¡w/NOT) ¡ ì AND ¡with ¡NOT ¡a_erwards ¡ ì OR ¡with ¡NOT ¡a_erwards ¡ Normal ¡form ¡ DeMorgan’s ¡Law ¡ enables ¡these ¡ alternate ¡forms ¡ Computer ¡Systems ¡and ¡Networks ¡ Spring ¡2012 ¡

7 ¡ Universal ¡Gates ¡ Example ¡using ¡only ¡NAND ¡gates: ¡ Why ¡bother ¡with ¡ ¡ ì NAND ¡and ¡NOR? ¡ Don’t ¡they ¡make ¡our ¡life ¡ ì more ¡difficult ¡compared ¡to ¡ the ¡obvious ¡AND, ¡OR, ¡NOT? ¡ NAND ¡and ¡NOR ¡are ¡ universal ¡ ì gates ¡ Easy ¡to ¡manufacture ¡ ì Any ¡Boolean ¡funcAon ¡can ¡be ¡ ì constructed ¡out ¡of ¡only ¡ NAND ¡or ¡only ¡NOR ¡gates ¡ Computer ¡Systems ¡and ¡Networks ¡ Spring ¡2012 ¡

8 ¡ Multiple ¡Input ¡/ ¡Multiple ¡Output ¡ ì We ¡can ¡physically ¡build ¡many ¡variaAons ¡of ¡these ¡ basic ¡gates ¡ ì Gates ¡with ¡many ¡inputs? ¡Yes! ¡ ì Gates ¡with ¡many ¡outputs? ¡Yes! ¡ ì Second ¡output ¡might ¡be ¡for ¡the ¡complement ¡of ¡the ¡ operaAon ¡ Computer ¡Systems ¡and ¡Networks ¡ Spring ¡2012 ¡

9 ¡ Combining ¡Gates ¡ ì Boolean ¡funcAons ¡can ¡be ¡implemented ¡by ¡combining ¡ many ¡gates ¡together ¡ ì Why ¡did ¡we ¡simplify ¡our ¡Boolean ¡expressions ¡ previously? ¡ ¡ So ¡we ¡can ¡build ¡simpler ¡circuits ¡with ¡fewer ¡gates! ¡ ì Computer ¡Systems ¡and ¡Networks ¡ Spring ¡2012 ¡

10 ¡ ì ¡ Combinational ¡Circuits ¡ Computer ¡Systems ¡and ¡Networks ¡ Spring ¡2012 ¡

11 ¡ Combinational ¡Circuits ¡ ì Two ¡general ¡classificaAons ¡of ¡circuits ¡ CombinaXonal ¡logic ¡circuits ¡ ì SequenXal ¡logic ¡circuits ¡ ì ì CombinaAonal ¡logic ¡circuits ¡ Produce ¡a ¡specified ¡output ¡(almost) ¡at ¡the ¡instant ¡when ¡ ì input ¡values ¡are ¡applied ¡ Also ¡known ¡as: ¡“Combinatorial ¡circuits” ¡ ì ì SequenAal ¡logic ¡circuits ¡ Incorporate ¡delay/“memory” ¡elements ¡ ì Will ¡discuss ¡later ¡ ì Computer ¡Systems ¡and ¡Networks ¡ Spring ¡2012 ¡

12 ¡ Combinational ¡Circuit ¡ ì In ¡teams ¡of ¡2, ¡write ¡the ¡truth ¡table ¡for ¡this ¡circuit ¡ Computer ¡Systems ¡and ¡Networks ¡ Spring ¡2012 ¡

13 ¡ Combinational ¡Circuit ¡ A D B C x ¡ y ¡ z ¡ A ¡ B ¡ C ¡ D ¡ F(x,y,z) ¡ 0 ¡ 0 ¡ 0 ¡ 1 ¡ 0 ¡ 0 ¡ 0 ¡ 0 ¡ 0 ¡ 0 ¡ 1 ¡ 1 ¡ 0 ¡ 1 ¡ 0 ¡ 1 ¡ 0 ¡ 1 ¡ 0 ¡ 1 ¡ 1 ¡ 0 ¡ 1 ¡ 1 ¡ 0 ¡ 1 ¡ 1 ¡ 1 ¡ 1 ¡ 1 ¡ 1 ¡ 0 ¡ 1 ¡ 0 ¡ 0 ¡ 0 ¡ 0 ¡ 0 ¡ 1 ¡ 1 ¡ 1 ¡ 0 ¡ 1 ¡ 0 ¡ 0 ¡ 0 ¡ 1 ¡ 1 ¡ 1 ¡ 1 ¡ 0 ¡ 0 ¡ 0 ¡ 0 ¡ 1 ¡ 1 ¡ 1 ¡ 1 ¡ 1 ¡ 0 ¡ 0 ¡ 0 ¡ 1 ¡ 1 ¡ Computer ¡Systems ¡and ¡Networks ¡ Spring ¡2012 ¡

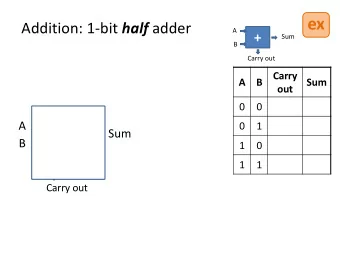

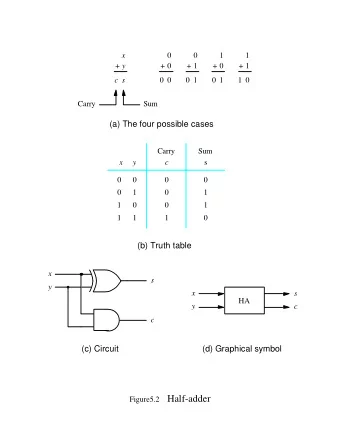

14 ¡ Combinational ¡Circuit ¡– ¡Half ¡Adder ¡ ì Half ¡Adder ¡ Finds ¡the ¡sum ¡of ¡two ¡bits ¡ ì ì How ¡can ¡I ¡implement ¡the ¡ truth ¡table? ¡ Sum ¡= ¡x ¡ ⊕ ¡y ¡ ¡ ¡ ¡ ¡ ¡(XOR) ¡ ì Carry ¡= ¡x ¡AND ¡y ¡ ì Computer ¡Systems ¡and ¡Networks ¡ Spring ¡2012 ¡

15 ¡ Combinational ¡Circuit ¡– ¡Full ¡Adder ¡ ì A ¡ full ¡adder ¡ is ¡a ¡half ¡adder ¡ plus ¡the ¡ability ¡to ¡process ¡a ¡ carry-‑input ¡ bit ¡ New ¡input: ¡ Computer ¡Systems ¡and ¡Networks ¡ Spring ¡2012 ¡

16 ¡ Combinational ¡Circuit ¡– ¡Full ¡Adder ¡ ì What ¡do ¡we ¡need ¡to ¡add ¡to ¡ the ¡half ¡adder ¡(shown ¡ below) ¡to ¡make ¡it ¡a ¡full ¡ adder? ¡ Half ¡ ¡ Adder ¡ Computer ¡Systems ¡and ¡Networks ¡ Spring ¡2012 ¡

17 ¡ Combinational ¡Circuit ¡– ¡Full ¡Adder ¡ A ¡Full ¡Adder ¡is ¡really ¡just ¡two ¡Half ¡Adders ¡in ¡ series ¡ Computer ¡Systems ¡and ¡Networks ¡ Spring ¡2012 ¡

18 ¡ Ripple ¡Carry ¡Adder ¡ ì Full ¡adders ¡can ¡be ¡connected ¡in ¡series ¡to ¡form ¡a ¡ ripple ¡carry ¡adder ¡ ì The ¡carry ¡bit ¡“ripples” ¡from ¡one ¡adder ¡to ¡the ¡next ¡ ì Why ¡is ¡the ¡performance ¡of ¡this ¡approach ¡slow? ¡ ì Slow ¡due ¡to ¡long ¡propagaAon ¡paths ¡ ì Modern ¡systems ¡use ¡more ¡efficient ¡adders ¡ Computer ¡Systems ¡and ¡Networks ¡ Spring ¡2012 ¡

19 ¡ Combinational ¡Circuit ¡– ¡Decoder ¡ ì Selects ¡one ¡(of ¡many) ¡outputs ¡from ¡a ¡single ¡input ¡ Decoder ¡block ¡diagram ¡ (black ¡box) ¡ Computer ¡Systems ¡and ¡Networks ¡ Spring ¡2012 ¡

20 ¡ Combinational ¡Circuit ¡– ¡Decoder ¡ ì ImplementaAon ¡of ¡a ¡2 ¡input ¡to ¡4 ¡output ¡decoder ¡ If ¡x ¡= ¡0 ¡and ¡y ¡= ¡1, ¡ which ¡output ¡line ¡ is ¡enabled? ¡ ¡ ¡ ¡ Computer ¡Systems ¡and ¡Networks ¡ Spring ¡2012 ¡

21 ¡ Memory ¡ ì Common ¡ decoder ¡applicaAon: ¡ Memory ¡address ¡ decoders ¡ ì n ¡inputs ¡can ¡select ¡any ¡of ¡2 n ¡locaAons. ¡ ¡ ì Example: ¡Suppose ¡we ¡build ¡a ¡memory ¡that ¡stores ¡ 2048 ¡bytes ¡using ¡several ¡64x4 ¡RAM ¡chips ¡ ì How ¡do ¡we ¡determine ¡ which ¡RAM ¡chip ¡to ¡use ¡ when ¡ reading/wriAng ¡a ¡parAcular ¡address? ¡ Computer ¡Systems ¡and ¡Networks ¡ Spring ¡2012 ¡

22 ¡ Memory ¡ Build ¡this: ¡ With ¡many ¡of ¡these: ¡ Full ¡Memory ¡ 2048 ¡total ¡bytes ¡ 64x4 ¡RAM ¡Chip ¡ (or ¡2048 ¡= ¡2 11 ¡addresses, ¡ 64 ¡(or ¡2 6 ) ¡locaAons ¡ ¡1 ¡byte ¡per ¡address) ¡ 4 ¡bits ¡per ¡locaAon ¡ Data ¡wires ¡ Data ¡wires ¡ Address ¡wires ¡ Address ¡wires ¡ (8) ¡ (4) ¡ (11) ¡ (6) ¡ Computer ¡Systems ¡and ¡Networks ¡ Spring ¡2012 ¡

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.