Unit 12 Adders & Arithmetic Circuits 12.2 Learning Outcomes I - PowerPoint PPT Presentation

12.1 Unit 12 Adders & Arithmetic Circuits 12.2 Learning Outcomes I understand what gates are used to design half and full adders I can build larger arithmetic circuits from smaller building blocks 12.3 ADDERS 12.4 Adder Intro

12.1 Unit 12 Adders & Arithmetic Circuits

12.2 Learning Outcomes • I understand what gates are used to design half and full adders • I can build larger arithmetic circuits from smaller building blocks

12.3 ADDERS

12.4 Adder Intro • Addition is one of the most common operations performed by computer systems Adder (+) • We can use adders to build larger Q Register 1 components like the counter to the right • Every clock cycle, the value Q (let's RESET say 4-bits: Q[3:0]), feeds back to the adder circuit which adds 1 to the CLK value and the register captures that new value on the next clock edge 0111 = curr Q • The sequence on Q on each clock cycle would be: 0, 1, 2, 3, 4… + 1 • Could you design what's inside the 1000 = next Q adder block? How would you do it?

12.5 Adder Intro • What if we had to add ANY two 4-bit numbers, X[3:0] and Y[3:0]? Do we have the 0110 = X techniques to build such a circuit directly? + 0111 = Y • Yes and no 1101 – No. Not with K-maps since there are 8-inputs – Yes. We could use sum of minterms but that would take a long time, but it could be done

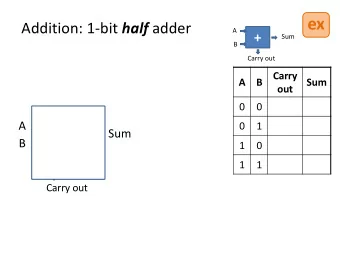

12.6 Adder Intro • Idea : Build a circuit that performs one column of addition and then use 4 instances of those circuits to perform the overall 4-bit addition 0110 = X • Let's start by designing a circuit + 0111 = Y that adds 2-bits: X and Y that are 1101 in the same column of addition X Y Half C out Adder S

12.7 Addition – Half Adders C out • Addition is done in columns 110 – Inputs are a bit from X and bit from Y, both 0110 = X from the same column – Outputs are the Sum Bit and Carry-Out + 0111 = Y (C out ) • Design a Half-Adder (HA) circuit that 1101 takes in X and Y and outputs S and C out Sum • Use the truth table to find the gate 0 1 implementation X Y X Y C out S Half C out 0 Adder 0 0 0 0 S 0 1 0 1 1 0 0 1 1 1 1 1 0

12.8 Problem With Half Adders • We’d like to use one 110 adder circuit for each 0110 = X column of addition + 0111 = Y • Problem: 1101 – No place for Carry-out of half adder to connect to the next 0 1 1 1 • Solution X Y X Y Half Half – Redesign adder circuit to C out C out 0 1 Adder Adder include an additional S S input for the carry 1 0

12.9 Addition – Full Adders C out C in • Add a Carry-In input(C in ) 110 • New circuit is called a 0110 = X Full Adder (FA) + 0111 = Y 1101 X Y C in C out S 0 1 0 0 0 0 0 X Y 0 0 1 0 1 0 1 0 0 1 Full 1 C out C in 0 Adder 0 1 1 1 0 S 1 0 0 0 1 1 0 1 1 0 0 1 1 0 1 0 1 1 1 1 1

12.10 Addition – Full Adders • Find the minimal 2- level implementations for Cout and S… X Y C in C out S 0 0 0 0 0 0 0 1 0 1 0 1 0 0 1 0 1 1 1 0 1 0 0 0 1 1 0 1 1 0 1 1 0 1 0 1 1 1 1 1 Recall a 2-input XOR can be written in SOP as F = x'y + xy'

12.11 XOR and XNOR Gates • Recall a 2-input XOR can be written in SOP as F = x'y + xy' • A 2-input XNOR can be written in SOP as F = x'y' + xy X X F F Y Y Z Z True if an odd # of inputs are true True if an even # of inputs are true XY X Y Z F X Y Z F XY 00 01 11 10 00 01 11 10 Z Z 0 0 0 0 0 0 0 1 0 2 6 4 0 2 6 4 0 1 0 1 0 0 1 1 0 0 1 0 1 0 1 0 0 0 0 1 0 1 0 1 0 0 1 3 7 5 1 3 7 5 0 1 1 0 0 1 1 1 1 0 1 0 0 1 0 1 1 1 1 0 0 1 1 0 0 0 1 0 1 0 1 0 1 1 F = X xor Y xor Z F = X xor Y xor Z 1 1 0 0 1 1 0 1 1 1 1 1 1 1 1 0 A checkerboard K-map corresponds to either an XOR or XNOR

12.12 Full Adder Logic • S = X Ꚛ Y Ꚛ Cin – Recall: XOR is defined as true when ODD number of inputs are true…exactly when the sum bit should be 1 • Cout = X∙Y + X∙Cin + Y∙Cin – Carry when sum is 2 or more (i.e. when at least 2 inputs are 1) – Circuit is just checking all combinations of 2 inputs

12.13 Addition – Full Adders (1) • Use 1 Full Adder for each column of addition 0110 + 0111 X Y X Y X Y X Y Full Full Full Full C out C in C out C in C out C in C out C in Adder Adder Adder Adder S S S S

12.14 Addition – Full Adders (2) • Connect bits of top number to X inputs 0110 + 0111 0 1 1 0 X Y X Y X Y X Y Full Full Full Full C out C in C out C in C out C in C out C in Adder Adder Adder Adder S S S S

12.15 Addition – Full Adders (3) • Connect bits of bottom number to Y inputs 0110 = X + 0111 = Y 0 0 1 1 1 1 0 1 X Y X Y X Y X Y Full Full Full Full C out C in C out C in C out C in C out C in Adder Adder Adder Adder S S S S

12.16 Addition – Full Adders (4) • Be sure to connect first C in to 0 0110 = X + 0111 = Y 0 0 1 1 1 1 0 1 X Y X Y X Y X Y Full Full Full Full C out C in C out C in C out C in C out C in 0 Adder Adder Adder Adder S S S S

12.17 Addition – Full Adders (5) • Use 1 Full Adder for each column of addition 00 0110 = X + 0111 = Y 1 0 0 1 1 1 1 0 1 X Y X Y X Y X Y 0 Full Full Full Full C out C in C out C in C out C in C out C in 0 Adder Adder Adder Adder S S S S 1

12.18 Addition – Full Adders (6) • Use 1 Full Adder for each column of addition 100 0110 = X + 0111 = Y 01 0 0 1 1 1 1 0 1 X Y X Y X Y X Y 1 0 Full Full Full Full C out C in C out C in C out C in C out C in 0 Adder Adder Adder Adder S S S S 0 1

12.19 Addition – Full Adders (7) • Use 1 Full Adder for each column of addition 1100 0110 = X + 0111 = Y 101 0 0 1 1 1 1 0 1 X Y X Y X Y X Y 1 1 0 Full Full Full Full C out C in C out C in C out C in C out C in 0 Adder Adder Adder Adder S S S S 1 0 1

12.20 Addition – Full Adders (8) • Use 1 Full Adder for each column of addition 01100 0110 = X + 0111 = Y 1101 0 0 1 1 1 1 0 1 X Y X Y X Y X Y 0 1 1 0 Full Full Full Full C out C in C out C in C out C in C out C in 0 Adder Adder Adder Adder S S S S 1 1 0 1

12.21 Performing Subtraction 0101 • To subtract 0101 = X + 1100 - 0011 = Y – Flip bits of Y 1 0010 0010 – Add 1 0 0 1 1 0 1 0 1 1 1 0 0 X Y X Y X Y X Y 1 1 0 1 Full Full Full Full C out C in C out C in C out C in C out C in 1 Adder Adder Adder Adder S S S S 0 0 1 0

12.22 4-bit Adders • We can create a component to perform 4-bit addition A 3 A 2 A 1 A 0 = A + B 3 B 2 B 1 B 0 = B S 4 S 3 S 2 S 1 S 0 = S A 3 B 3 A 2 B 2 A 1 B 1 A 0 B 0 C out C in 4-bit Adder S 3 S 2 S 1 S 0

12.23 Device vs. System Labels • When using hierarchy (i.e. building blocks) to design a circuit be sure to show both device and system labels – Device Labels: Signal names used inside the block • Placeholder names the designer/manufacturer of the block uses to indicate which input/output is which to the outside user (Names may vary; read the manual) – System labels: Signal names used outside the block • Actual signals from the circuit being built and given by the designer • Can have the same name as the device label if such a signal name exists at the outside level Analogy: Formal and Actual parameters 1. a and b are like device labels and X3 X2 X1 X0 Y3 Y2 Y1 Y0 indicate the names used inside a block. Device Labels: 2. x and y are like system labels and Indicate which represent the actual values to be used. input/output is B3 B2 B1 B0 A3 A2 A1 A0 which inside int div(int a, int b) { int s = a/b; the bock. 4-bit Adder 0 (GND) C4 C0 return s; } System Labels: int main() S3 S2 S1 S0 { Actual signals from int x=10, y=2; the circuit being built int s = div(x,y); S3 S2 S1 S0 }

12.24 EXERCISES

12.25 Building an 8-bit Adder • Use (2) 4-bit adders to build an 8-bit adder to add X=X[7:0] and Y= Y[7:0] and produce a sum, S=[7:0] and a carry-out, C8. – Label the inputs and outputs and make appropriate connections X7 X6 X5 X4 Y7 Y6 Y5 Y4 X3 X2 X1 X0 Y3 Y2 Y1 Y0 B3 B2 B1 B0 A3 A2 A1 A0 B3 B2 B1 B0 A3 A2 A1 A0 4-bit Binary Adder 4-bit Binary Adder C8 C4 C4 0 C0 C0 S3 S2 S1 S3 S2 S1 S0 S0 S3 S2 S0 S5 S4 S1 S7 S6

12.26 Adding Many Bits • You know that an FA adds X + Y + Ci A B • Use FA and/or HA X Y components to add 4 C in C out C Full Adder individual bits: S A + B + C + D D • Solution: X Y X Y – 4 bits could yield sums from C out 000 – 100 2 . So we need 3 C out Half Adder Half Adder bits of output (S2,S1,S0) S S – Be sure that bits you connect S0 S2 S1 to a HA or FA are all from the same column (weight)

12.27 Adding 3 Numbers Y3 Y2 Y1 Y0 • Add X[3:0] + Y[3:0] + Z[3:0] X1 X0 X3 X2 0 to produce F[?:0] using the adders shown plus any FA 4-bit Adder and HA components you need • Solution: Adding (3) 4-bit CA numbers yields a sum of at most 45 = 15 + 15 + 15 Z3 Z0 0 Z2 Z1 CA CB which requires 6 bits of X Y output (F[5:0]) C out 4-bit Adder – Be sure the bits you connect Half Adder to the same adder column S have the same CB significance/weight F5 F4 F3 F2 F1 F0

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.