Lecture 2 Review Path Intergrals over Complex Plane Let : ( * - PowerPoint PPT Presentation

Lecture 2 Review Path Intergrals over Complex Plane Let : ( * = ? ( ) Lecture 2 Review Question #1: Express XOR using only NAND and NOT gates A A B B Y Y A A B B rgans&theorem!&

Lecture 2 Review

Path Intergrals over Complex Plane § Let 𝑔 𝑨 : ℂ → ℝ ( * 𝑔 𝑨 𝑒𝑨 = ? § ∫ ( )

Lecture 2 Review § Question #1: ú Express XOR using only NAND and NOT gates A A B B Y Y A A B B rgan’s&theorem!&

Lecture 2 Review § Question #1b: ú Implement XOR using only NAND gates ú HINT: Implement NOT using NAND gates A B Y A B rgan’s&theorem!& A A’ A A’ OR A A’ 1

Lecture 2 Review § Question #2a: ú Construct the truth table for the following requirement When A is off, I want the A B C Y 0 0 0 0 output to be high 0 0 1 1 whenever one of B or C 0 1 0 1 are 1, but low when 0 1 1 0 they’re both 1 or both 0. 1 0 0 1 When A is on, I want the 1 0 1 0 output to be high when B 1 1 0 0 1 1 1 1 and C are both 0 or both 1, and low otherwise.

Lecture 2 Review § Question #2a: ú Construct the truth table for the following requirement When A is off, I want the A B C Y 0 0 0 0 output to be high 0 0 1 1 whenever one of B or C 0 1 0 1 are 1, but low when 0 1 1 0 they’re both 1 or both 0. 1 0 0 1 When A is on, I want the 1 0 1 0 output to be high when B 1 1 0 0 1 1 1 1 and C are both 0 or both 1, and low otherwise.

Lecture 2 Review § Question #2b: ú What are the minterms for the following table? ú What is the SOM expression (non reduced) A B C Y Y = m 1 + m 2 + m 4 + m 7 0 0 0 0 0 0 1 1 0 1 0 1 Y = ABC + ABC + 0 1 1 0 ABC + ABC 1 0 0 1 1 0 1 0 1 1 0 0 1 1 1 1

Lecture 2 Review X A B C D § Question #3a 0 0 0 0 1 ú Complete the truth table 0 0 0 1 1 0 0 1 0 1 0 0 1 1 0 0 1 0 0 0 Y = m 0 + m 1 + m 2 + m 5 + 0 1 0 1 1 A m 7 + m 8 + m 9 + m 10 + 0 1 1 0 0 m 13 + m 15 0 1 1 1 1 1 0 0 0 1 1 0 0 1 1 1 0 1 0 1 1 0 1 1 0 1 1 0 0 0 1 1 0 1 1 1 1 1 0 0 1 1 1 1 1

Lecture 2 Review X A B C D 0 0 0 0 1 § Question #3b 0 0 0 1 1 0 0 1 0 1 ú Construct the K-Map 0 0 1 1 0 0 1 0 0 0 0 1 0 1 1 0 1 1 0 0 C · D C · D C · D C · D 0 1 1 1 1 1 0 0 0 1 A · B 1 1 0 1 1 0 0 1 1 1 0 1 0 1 A · B 0 1 1 0 1 0 1 1 0 A · B 0 1 1 0 1 1 0 0 0 1 1 0 1 1 A · B 1 1 0 1 1 1 1 0 0 1 1 1 1 1

Lecture 2 Review § Question #3c: ú Find the groupings and reduce the expression C · D C · D C · D C · D Y = BD + CD + BD A · B 1 1 0 1 A · B 0 1 1 0 A · B 0 1 1 0 A · B 1 1 0 1

Lecture 3 review

Question #1 a) How do you write the number 78 as an 8-bit binary number? 128 64 32 16 8 4 2 1 0 1 0 0 1 1 1 0 b) What is the two’s complement of 01101101 ? 10010011 c) What is 11001010 In decimal? - 54 202 Unsigned Signed (2’s complement) 128 64 32 16 8 4 2 1 -128 64 32 16 8 4 2 1 1 1 0 0 1 0 1 0 1 1 0 0 1 0 1 0

Question #1 d) What is the sum of 01101101 and 01101101 ? 011011010 Don’t forget to add the extra 0 to the front § Adding a number to itself à multiply by 2 § Multiply by 2 à shift bits to the left

Question #2 C · D C · D C · D C · D § What groupings A · B 1 1 X 1 are in the K-map A · B X 0 X 1 on the right? A · B 1 X X 1 A · B 1 X 0 X § What logic equations do these groupings represent? A · B + C

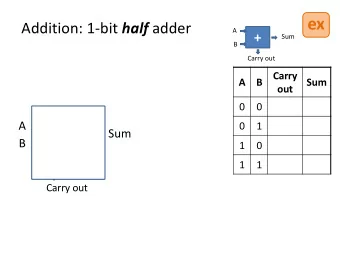

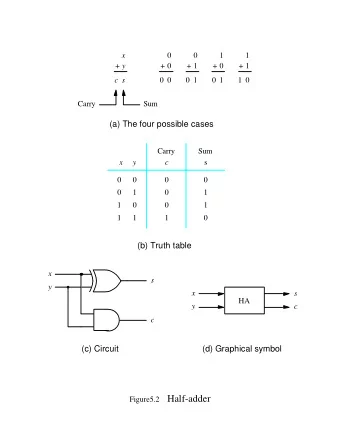

X Y Question #3 C HA § Implement a half adder in Verilog. S § Step 1:What is the half adder logic equation? C = X · Y S = X · Y + X · Y = X Å Y § Step 2: Equivalent Verilog components. assign C = X & Y; assign S = X & ~Y | ~X & Y;

X Y Question #3 (cont’d) HA C § Step 3: What is the complete Verilog code for this device? S module half_adder(X, Y, C, S); input X, Y; output C, S; assign C = X & Y; assign S = X & ~Y | ~X & Y; endmodule

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.

![[9] Orthogonalization Finding the closest point in a plane Goal: Given a point b and a plane, find](https://c.sambuz.com/1004577/9-orthogonalization-finding-the-closest-point-in-a-plane-s.webp)