Analog/Mixed-Signal Design Challenges in 7-nm CMOS and Beyond - PowerPoint PPT Presentation

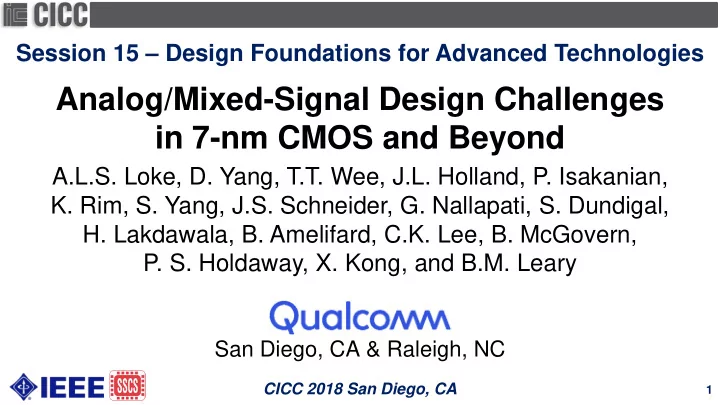

Session 15 Design Foundations for Advanced Technologies Analog/Mixed-Signal Design Challenges in 7-nm CMOS and Beyond A.L.S. Loke, D. Yang, T.T. Wee, J.L. Holland, P. Isakanian, K. Rim, S. Yang, J.S. Schneider, G. Nallapati, S. Dundigal, H.

Session 15 – Design Foundations for Advanced Technologies Analog/Mixed-Signal Design Challenges in 7-nm CMOS and Beyond A.L.S. Loke, D. Yang, T.T. Wee, J.L. Holland, P. Isakanian, K. Rim, S. Yang, J.S. Schneider, G. Nallapati, S. Dundigal, H. Lakdawala, B. Amelifard, C.K. Lee, B. McGovern, P. S. Holdaway, X. Kong, and B.M. Leary San Diego, CA & Raleigh, NC CICC 2018 San Diego, CA 1 CICC 2018 San Diego, CA

Mobile SoC – Main Driver for CMOS Scaling • 7nm smartphone products imminent 40 Logic cell • SoC technology driven by economics 1 SRAM cell of logic & SRAM scaling 28 Normalized Area 20 • New node feasible with enough PPAC 14 (Power/Performance/Area/Cost) benefit 10nm • Incremental feature size reduction 0.1 • Extensive logic & SRAM DTCO • AMS (Analog/Mixed-Signal) ubiquitous • PLLs, wireline I/Os, ESD, regulators, data converters, bandgap references 0.01 • AMS device palette slaved to logic 2010 2012 2014 2016 2018 Yang, Qualcomm [22] 2 CICC 2018 San Diego, CA

Outline • Introduction • Technology Scaling Enablers • AMS Device Palette • AMS Design Impact • Concurrent Technology/Design Development • Conclusion CICC 2018 San Diego, CA 3

Outline • Introduction • Technology Scaling Enablers • FinFET • Lithography & Self-Aligned Patterning • High- K Gate Dielectric & Metal Gate (HKMG) • Mechanical Stressors • Middle-End-Of-Line (MEOL) • AMS Device Palette • AMS Design Impact • Concurrent Technology/Design Development • Conclusion CICC 2018 San Diego, CA 4

Stronger Short-Channel Gate Control log ( I D ) gate V GS I Dsat I Dlin C ox S V DS lower supply ϕ s drain & power for source I off C D C B given I on & I off DIBL V GS body V BS V Tsat V Tlin V DD • Subthreshold controlled by C ox vs. ( C B + C D ) • Fully-depleted finFET weakens C B & C D less S , DIBL & body effect 5 CICC 2018 San Diego, CA

Fully Depleted Tri-Gate FinFET • More I on & g m per area fully • Quantized channel width depleted body • Less DIBL higher r out , 3 × intrinsic gain drain well tie • Negligible body effect ( Δ V T < 10mV) • Less RDF mismatch source • Parasitics STI • High S/D resistance big deal well • High S/D coupling to gate p-substrate • Fin width << fin pitch low C j , high R well CICC 2018 San Diego, CA 6

Foundry Pitch Scaling 200 40 28 20 16/14 10 7nm Minimum Pitch (nm) 160 120 gate (CGP) 193i single 80 exposure limit metal 40 fin 0 2008 2010 2012 2014 2016 2018 2020 • Scaling rate slower than 0.7x per node node name = PPAC marketing • EUV late, only started at 7nm process complexity for sub-80nm pitch Yang, Qualcomm [10] CICC 2018 San Diego, CA 7

Lithography Innovations Pitch splitting (LELE) Orthogonal cutting • Interleave single exposures • Extra mask(s) to break line patterns • Mask color decomposition & balance • Reduced end-to-end spacing • Extendible to LELELE • Limited by overlay in very tight pitch • Limited by overlay between masks cut mask pattern Mask A Mask B Arnold et al ., ASML [11] Auth et al ., Intel [12] CICC 2018 San Diego, CA 8

Spacer-Based Patterning • Pattern fins; now common for gate, MEOL & lower BEOL • Conformal spacer correlated LER less width variation • Mandrel & spacer width control critical to minimize pitch walking • Only one feature width, but can be trimmed with extra mask Spacer 1 mandrel SADP Spacer 2 SAQP Choi et al ., UC Berkeley [13] CICC 2018 San Diego, CA 9

Self-Aligned Metal Patterning Self-aligned via SADP/SAQP + block mask • Dual-damascene metal integration • Block mask to bridge several spacers • Adjust mandrel width/space for more • Conceptually similar to cuts flexible metal width/space • Via etch only at intersection of trench & via masks metal trench via mask hard mask block mask ILD via etch Brain et al ., Intel [16] Woo et al ., Globalfoundries [15] CICC 2018 San Diego, CA 10

High- K + Metal-Gate (HKMG) Higher C ox • Less I gate , no poly depletion HKMG gate cap gate S/D trench over fin • Replacement metal gate spacer contact (RMG) for stable V T with delicate HK/MG interface • V T tuning with ALD MG stack composition & HK dipoles less variation than implants fins with S/D • High gate resistance silicide only epitaxial fill metal fill at bottom • High S/D resistance of contact MG with silicide last HK dielectric Hou, TSMC [9] Auth et al. , Intel [14] CICC 2018 San Diego, CA 11

Mechanical Stressors Mobility Boost • Induce channel strain along L with surrounding stressors • Tensile for NMOS, compressive for PMOS (but reality very complicated) • Techniques: S/D fin recess & epitaxy, gate stress • More effective for PMOS, β ratio 1, not scaling well with CGP • Less effective for longer L NMOS PMOS Chan et al ., IBM [20] CICC 2018 San Diego, CA 12

Complex MEOL & Self-Aligned Contacts • Tight CGP tough to land diffusion & gate contacts without shorts • Dielectric caps protect gate & contact against etch • Self-aligned gate contacts over fins, not restricted to gate overhang • More interfaces high S/D, MEOL & lower BEOL resistance contact metal metal dielectric self-aligned self-aligned cap diffusion gate S/D via gate contact contact contact gate self- dielectric gate cap aligned gate contact Yang, Qualcomm [10] CICC 2018 San Diego, CA 13

Single vs. Double Diffusion Break • Dummy gates terminate OD to constrain S/D epitaxy • SDB eliminates dummy gate waste saves 10–20% logic area • Aggressive tensile dielectric isolation for SDB stress LDE dummy DDB SDB gates Yang et al ., Qualcomm [22] CICC 2018 San Diego, CA 14

Outline • Introduction • Technology Scaling Enablers • AMS Device Palette • Transistors • Passives • Diodes • AMS Design Impact • Concurrent Technology/Design Development • Conclusion CICC 2018 San Diego, CA 15

Stacked FET for Higher r out • L max limited by gate litho/etch loading & HKMG CMP • Short L has most µ boost potentially less area • Intermediate diffusions degrade HF r out (gain, CMRR, …) 1.2 DC i ac HF i ac 240nm Normalized r out 1.0 0.8 0.6 0.4 L min stack 0.2 0.0 0.01 0.10 1.00 10.00 Normalized Frequency CICC 2018 San Diego, CA 16

Thick-Oxide I/O FET • GPIOs still use 1.8V swing despite reduced core V DD • Talk to peripheral ICs made in lower cost nodes • Challenging to keep 1.8V I/O devices • Tighter fin pitch tough ALD gate fill • Complex level shifters to handle larger Δ V DD • Many links stopped supporting legacy modes to enable higher data rate & lower power • Improve power & area with thinner I/O oxide, e.g., 1.2V tighter fin pitch Wei et al ., Globalfoundries [25] CICC 2018 San Diego, CA 17

Passives ( RCL ) Resistors Capacitors • BEOL MOM (Metal-Oxide-Metal) • MEOL thin film resistor • HKMG poly resistor obsolete • High density with metal pitch scaling • Reduced AC coupling efficiency • Variation limits area scaling • Accumulation-mode varactor • Gate resistor – unusable, high variation • Steeper C-V transition • Upper-BEOL MIM – uncommon in mobile n+ n+ Inductors n-well • Upper BEOL layers p-substrate • Small impact from scaling, but more fill CICC 2018 San Diego, CA 18

Diodes • High R well stricter well tie, guard ring & latch-up rules • ESD & latch-up guidelines immature during technology development PNP-BJT (Analog Diode) STI ESD Diode base collector emitter p+ n+ p+ p+ n+ n-well p-well n-well p-substrate p-substrate CICC 2018 San Diego, CA 19

Outline • Introduction • Technology Scaling Enablers • AMS Device Palette • AMS Design Impact • Parasitics • Layout-Dependent Effects (LDEs) • Layout Considerations • Concurrent Technology/Design Development • Conclusion CICC 2018 San Diego, CA 20

Diffusion & MEOL Resistance • Challenging for high-current circuits, e.g., I/O drivers, clock buffers • Double-source layout halves S/D R contact (despite higher C ) • Extend SAC to land extra diffusion via extra self-aligned short together extended SAC diffusion via gate fin diffusion contact (SAC) CICC 2018 San Diego, CA 21

BEOL Resistance • Aggressive M1-M3 pitch scaling for dense Normalized Resistance logic routing less die area & cost 9 • Meticulous pitch optimization for PPAC 7 • High- ρ TaN barrier cladding Cu wire not 5 scaling with metal pitch 3 Cu 1 Co 80 64 48 • Barrier-less cobalt & ruthenium with Metal Pitch (nm) higher ρ are promising material enablers Auth et al. , Intel [14] Yang et al ., Qualcomm [22] CICC 2018 San Diego, CA 22

Low-Voltage Bandgap Reference Ideality higher I o I o AI o Factor, η series R D usable I o /N & I o range N 1 log( I D ) • Higher R D smaller N variation sensitivity • Higher V D from high well doping higher V DD (e.g., 1.2V) for headroom • Variation dominated by PMOS mirror mismatch trimming Banba et al ., Toshiba [26] CICC 2018 San Diego, CA 23

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.