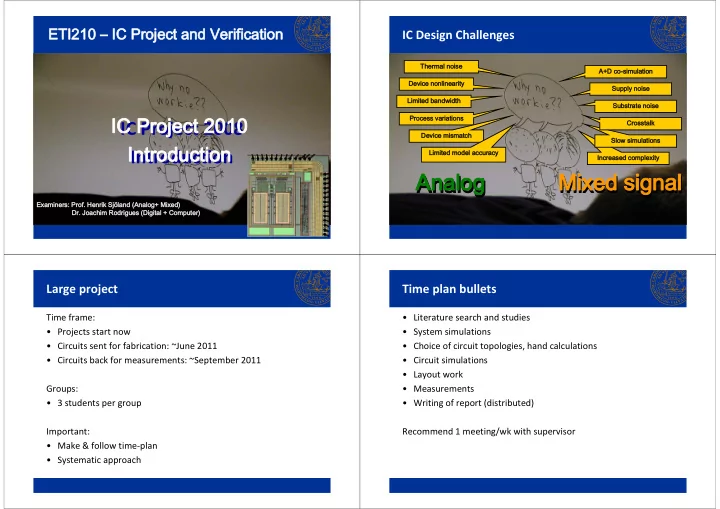

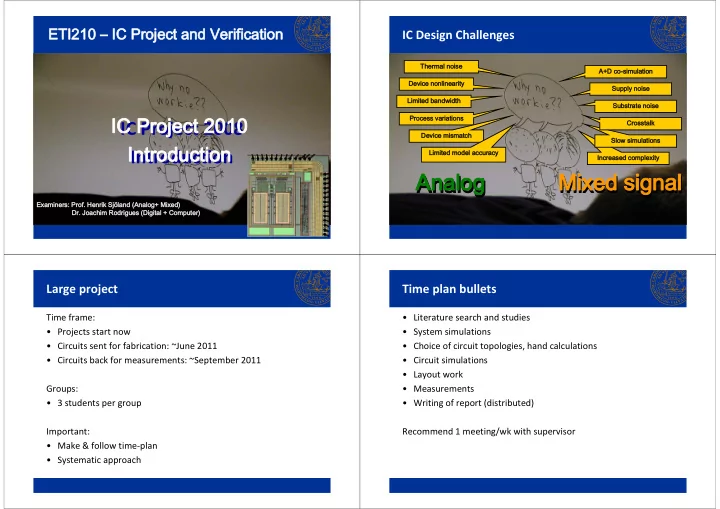

ETI210 – IC Project and Verification IC Design Challenges Thermal noise A+D co-simulation Device nonlinearity Supply noise Limited bandwidth Substrate noise IC Project 2010 Process variations Crosstalk IC Project 2008 Device mismatch Slow simulations Introduction Introduction Limited model accuracy Increased complexity Analog Mixed signal Analog Mixed signal Examiners: Prof. Henrik Sjöland (Analog+ Mixed) Dr. Joachim Rodrigues (Digital + Computer) Large project Time plan bullets Time frame: • Literature search and studies • Projects start now • System simulations • Circuits sent for fabrication: ~June 2011 • Choice of circuit topologies, hand calculations • Circuits back for measurements: ~September 2011 • Circuit simulations • Layout work Groups: • Measurements • 3 students per group • Writing of report (distributed) Important: Recommend 1 meeting/wk with supervisor • Make & follow time ‐ plan • Systematic approach

Teaching Top Down Design Methodology Analog & Mixed IC Projects 2010 Rough Timeplan through IC Design Projects • HT LP2 (15 December’10) – System model review. Project Study phase as well as designing and simulating input a structural system model. • VT LP1 (1 March’11) – Schematic design review. Schematic level design and simulations Project • VT LP2 (15 May’11) – Tape-Out design review. execution Layout and post layout simulations • HT LP1 (15 October’11) Measurement verification Project • Hand in design report examination Requirements IC Project 1: Audio Class D Amplifier • Switched mode amplifier • Passed Analog IC exam • Self oscillating with hysteresis • (Passed Digital IC exam) • High loop gain • Introduce dead time with comparator offset ‐ minimal delay ‐ > maximize loop gain • 9 credits: • Goals: High efficiency – Design and implementation of a circuit prototype low THD+N in UMC 130-nm CMOS – 3 Design reviews (project milestones) – Written design report • 3 credits: – Measurement verification & report • Completing the course, total 12 credits. Supervised by Carl Bryant

IC Project 2: PLL for Gbit Ethernet IC ‐ projects 3,4: Delta ‐ Sigma A/D ‐ Converters clk • Two projects: H(s) v c (t) v d [n] ∫ • Audio � Diff-control ring oscillator v a (t) – Hearing ‐ aid applications � Differential CP DAC – Supervisor: Dejan � Pulse sampled LPF clk � Continuous VCO tuning Delta-Sigma Analog/Digital Converter • Telecommunication (GSM) bank adjusting – 100kHz bandwidth Specification � 25MHz reference – Supervisor: Mattias � 1GHz output � <-110dBc/Hz@1MHz Supervised by Ping Lu and Andreas Axholt Supervised by Dejan Radjen & Mattias Andersson IC Project 5: FM radio receiver front ‐ end IC Project 6: Buck ‐ Boost DC ‐ DC Converter • Buck ‐ Boost DC ‐ DC Converter • LNA + Mixer + QLO generation • Off ‐ chip Inductor (L) • Specifications – Conv. Gain 20dB • Self Oscillating System LNA – NF < 4dB RF BB – S11 < ‐ 10dB 88-108 MHz Main Goals : – IIP3 < ‐ 5dBm QLO • High Efficiency – IRR > 40 dB 2xLO 87.5-107.5 MHz • High Output Power (V Out ≥ 2 ∙ V DD ) 175-215 MHz • Low Switching Noise @ Output Div 2 Supervised by Jonas Lindstrand Supervised by Martin Liliebladh

Apply for a project now! Talk to the supervisors: • Jonas Lindstrand • Carl Bryant • Dejan Radjen • Mattias Andersson • Ping Lu • Andreas Axholt • Martin Liliebladh or to the course manager Henrik Sjöland

Recommend

More recommend