VLSI Placement Sadiq M. Sait & Habib Youssef December 1995 - PDF document

King Fahd University of Petroleum & Minerals College of Computer Sciences & Engineering Department of Computer Engineering VLSI Placement Sadiq M. Sait & Habib Youssef December 1995 Placement Placement is the process of

King Fahd University of Petroleum & Minerals College of Computer Sciences & Engineering Department of Computer Engineering VLSI Placement Sadiq M. Sait & Habib Youssef December 1995

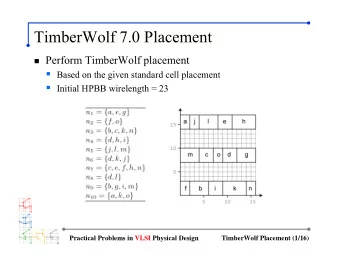

Placement • Placement is the process of arranging the cir- cuit components on a layout surface. • Example: (a) A tree circuit. (b) A 2-D placement of gates. (c) A 2-D symbolic placement. (d) A 2-D place- ment requiring 12 units (estimated) of wiring. (e) A 1-D placement requiring 10 units (estimated) of wiring.

1 5 2 7 8 3 6 4 (a) 2 3 1 2 1 1 5 6 5 3 3 5 4 6 8 4 6 4 2 7 8 7 7 8 (b) (d) (c) 1 8 3 2 7 5 6 4 (e) • The total wirelength ω is a widely used mea- sure of the quality of the placement (easy to compute). • Consider the symbolic placement of Figure (a) below.

• (a) Optimal placement with ω =12. (b) Alter- nate solution with ω =22. 2 3 9 1 1 2 6 8 6 5 4 5 7 4 3 7 8 9 (a) (b) • The area of a layout consists of two parts — the functional area, and the wiring area.

Definition & Complexity • Placement is NP-complete. • Even the simplest case (namely 1-D place- ment), is hard to solve; there are n ! 2 arrange- ments of n cells. • For n = 50, (a small design), n ! 2 = 1 . 5 × 10 64 . • Problem Statement Given: – A collection of cells or modules with ports on the boundaries. – The dimensions of these cells. – A collection of nets. Goal: Find suitable physical locations for each cell on the entire layout. Sometimes a subset of the modules are pre- assigned to locations.

Cost Functions and Constraints • Routability. • Wirelength. • Area. • Performance (timing, power, etc.) • Most widely used cost function is wirelength. • Performing actual routing to compare various placement solutions is impractical; therefore, estimates are used. • Various methods of estimation are: – Semi-perimeter Method – Complete Graph – Minimum Chain – Source to Sink Connection – Steiner Tree Approximation – Minimum Spanning Tree

Application of Different Estimation Methods 4 6 9 6 7 3 3 4 Complete graph length * 2/n= 16 Semi-perimeter length= 10 (b) (a) 7 9 3 3 3 4 Chain length= 13 Source to sink length= 16 (c) (d) 6 7 3 4 3 Spanning tree length= 12 Steiner tree length= 11 (e) (f)

Minimize Total Wirelength • The total weighted wirelength expressed as: � L ( P ) = w n · d n n ∈ N where, d n =estimated length of net n ; w n =weight of net n . H F A E B G C D Nets Weights N 1 = ( A 1 , B 1 , H ) w 1 = 2 N 2 = ( B 2 , C 1 ) w 2 = 4 N 3 = ( C 2 , D ) w 3 = 3 N 4 = ( E 1 , F ) w 4 = 1 N 5 = ( A 2 , E 2 , G ) w 5 = 3 L ( P ) = 2 · 2 + 4 · 1 + 3 · 1 + 1 · 1 + 3 · 2 = 18 .

Minimize Maximum Cut • Consider the Figure below. x = x i • Let Φ P ( x i ) and Φ P ( y i ) denote the number of nets for placement P cut by lines x i , and y i . • For a given placement P , let X ( P ) indicate the maximum value of Φ P ( x i ) over all i , that is, X ( P ) = max [Φ P ( x i )] i Y ( P ) = max [Φ P ( y j )] j • Φ P ( x i ) and Φ P ( y j ) are also related to L ( P ). � � L ( P ) = Φ P ( x i ) + Φ P ( y j ) i j • Reducing X ( P ) and Y ( P ) increases routability.

Minimize Maximum Density • An alternate measure for routability is the den- sity D ( P ) defined as follows. A A B (b) (a) – Let η P ( e i ) indicate the number of nets that must pass through each edge e i ; and – Let ψ P ( e i ) indicate the capacity of the edge e i , Then we define the density of edge e i as d P ( e i ) = η P ( e i ) ψ P ( e i ) • d P ( e i ) must be ≤ 1 for routability. The routabil- ity measure of the placement is given by D ( P ) = max [ d P ( e i )] i

Con Lin Plmt ( n, C, P ) Algorithm Begin . (* n is the number of cells.*) (* C [1 · · · n, 1 · · · n ] is the conn matrix.*) (* P [1 · · · n ] is the placement vector.*) (* P [ i ] is the slot in which m i is placed.*) For i = 1 to n P [ i ] = −∞ ; (* P [ i ] = −∞ means slot i is empty.*) EndFor S ← Seed( n, C ); (*Determine the Seed cell.*) P [ S ] ← n 2 ; (*Place the Seed cell in the center.*) Mark S as placed; For i = 1 to n − 1 Do sc ← Select Cell ( n, P, C ); ss ← Select Slot ( n, sc, P, C ); P [ sc ] ← ss ; Mark sc as placed; End ; End .

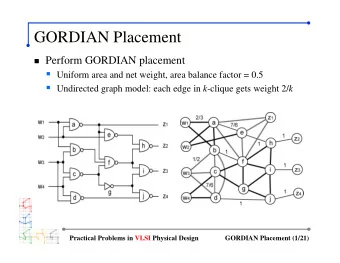

Popular Approaches to Placement • Partition-based method which is based on the min-cut heuristic. • Simulated Annealing based placement. • Mathematical Programming approach; (this has been covered in floorplanning). • Force-directed heuristic which is a numerical technique. • Other approaches: e.g., Genetic placement.

Partition-Based Methods • A partitioning algorithm – groups together closely connected modules – grouping reduces interconnection length and wiring congestion – is be applied repeatedly to generate a place- ment • Illustration A B B2 A1 A2 B1 c c c 2 c1 1 3 B1 A1 c c 2 3 A B A2 B2 c 1

• The procedure described above does not min- imize X ( P ), but minimizes Φ P ( c 2 ) subject to the constraint that Φ P ( c 1 ) is minimum. • We write this function as Φ P ( c 2 ) | Φ P ( c 1 ). • The procedure also minimizes Φ P ( c 3 ) | Φ P ( c 1 ). • A sequential objective function denoted by F ( P ) simplifies the problem. F ( P ) = min[Φ P ( c r )] | min[Φ P ( c r − 1 )] | . . . . . . | min[Φ P ( c 1 )] where c 1 , c 2 , . . . , c r , is an ordered sequence of vertical or horizontal cutlines.

The Min-Cut Placement Algorithm • Assumes the availability of an ordered sequence of cutlines. • These cutlines divide the layout into slots. Two key requirements of the algorithm are: (1) an efficient procedure to partition the cir- cuit, and (2) the selection of cutlines. • Greedy procedure, therefore solution obtained is not globally optimal. • Illustration of sequences of cutlines. 1 3a 3a 2a 2 3b 3 1 4 1 5 3c 3b 2b 6 3d 7 10a 9a 10b 8 10c 9b 10d 4a 6a 5a 6b 4 6c 5b 6d 2 4b (b) (c) (a) • Three schemes: 1. Quadrature Placement Procedure 2. Bisection Placement Procedure 3. Slice/Bisection

Min − cut ( ℵ , n, C ) Algorithm (* ℵ is the layout surface. n is the number of cells to be placed. n 0 is the number of cells in a slot. C is the connectivity matrix *). Begin If ( n ≤ n 0 ) Then place-cells ( ℵ , n, C ) Else Begin ( ℵ 1 , ℵ 2 ) ← cut - surface ( ℵ ); ( n 1 , c 1 ) , ( n 2 , c 2 ) ← partition ( n, C ); Call Min-cut ( ℵ 1 , n 1 , c 1 ); Call Min-cut ( ℵ 2 , n 2 , c 2 ); EndIf ; End .

Example 8 P 2 4 1 7 14 O Q 1 5 12 3 R 9 13 6 16 O 11 2 O 15 3 10 • Partitioning using the KL algorithm yields two sets of gates, namely L and R , where L = { 1,2,3,4,5,6,7,9 } and R = { 8,10,11,12,13,14,15,16 } . The cost of this cut is found to be 4. • Elements of subsets after second partition are: LT = { 2,4,5,7 } ; (* Top Left *) LB = { 1,3,6,9 } ; (* Bottom Left *) RT = { 8,12,13,14 } ; (* Top Right *) RB = { 10,11,15,16 } . (* Bottom Right *)

8,12,13,14 2,4,5,7 C 2 1,3,6,9 10,11,15,16 C 1 • The procedure is repeated again with two cut- lines running vertically/horizontally ( c 3 a and c 3 b )/( c 4 a and c 4 b ). • Final division of layout into slots and the as- signment of gates. P 2 4 8 14 O1 C4a C4a 5 12 13 7 C2 C2 Q 1 O2 16 11 9 C4b C4b 10 O 3 3 6 15 R C3b C3a C1

Limitation of the Min-cut Heuristic • Location of external pins not taken into ac- count. • The inclusion of these signals in partitioning- based placement is terminal propagation . • Cell x of a group connected to an external signal s . x s • Clearly cell x has to be nearest to the point where signal s enters. • At the outermost level, signal positions are typically fixed by pad positions. • What happens at an inner level of partitioning?

• (a) Partitioning of R following partitioning of L . (b) Propagating s to the axis of partition- ing. s p L1 L 1 R R L2 L 2 (b) (a) • First stage non-bias partition. p 2 p 1 R s L L R s p 3 G (a) (b)

• To do terminal propagation, the partitioning has to be done breadth first.

Example • The gates of the circuit shown in Figure below are to be assigned to slots of a 2 × 2 array. • (a) Circuit for Example. (b) Corresponding graph. s s a b a b c d c d (b) (a) • Solution. (a) Dividing the circuit into L and R . (b) Unbiased partition of R . (c) Biased partition of L producing P . (d) L partitioned without terminal propagation. C1 C1 C1 C1 c b a b p L R 1 L R 1 a b a b 1 1 1 L R R L c L d d c d 2 L R c d R 2 2 2 a (a) (b) (c) (d)

Simulated Annealing for Placement • We now adapt Simulated annealing for place- ment. The requirement are: 1. a suitable perturb function to generate a new placement configuration (cell assign- ment to slots), and 2. a suitable accept function. • A simple neighbor function is the pairwise in- terchange. • Other schemes to generate neighboring states include – displacing a randomly selected cell to a ran- dom location, – the rotation and mirroring of cells, etc. • In simulated annealing, the swap is accepted if – ∆ h < 0 (∆ h = ( Cost ( NewS ) − Cost ( S ))), or – if the acceptance function ( random < e − ∆ h/T ) is true.

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.