USCMS HCAL USCMS HCAL USCMS HCAL TriDAS Update Drew Baden - PowerPoint PPT Presentation

USCMS HCAL USCMS HCAL USCMS HCAL TriDAS Update Drew Baden University of Maryland http://www.physics.umd.edu/hep/HTR/hcal_june_2003.pdf 1 CMS June 2003 HTR Status HTR Status HTR Status Rev 1 run Summer 2002 testbeam Board worked

USCMS HCAL USCMS HCAL USCMS HCAL TriDAS Update Drew Baden University of Maryland http://www.physics.umd.edu/hep/HTR/hcal_june_2003.pdf 1 CMS June 2003

HTR Status HTR Status HTR Status • Rev 1 run Summer 2002 testbeam � Board worked well – all functional requirements met � Big concern on mechanical issues for production o Had a difficult experience with previous board manufacturing • Rev 2 produced March 2003 � Board production changes: o New assembler, in-house X-ray, DFM review, QC o Gold plated (Rev 1 was white-tin) for better QC � Changes to HTR: o Change from Virtex 1000E FBGA (1.00mm) to Virtex2 3000 BGA (1.27mm) o Added stiffeners o Moved all SLB/TPG output to front-panel daughterboards o Modified Rx refclk scheme (the usual TTC/refclk clocking concerns) � Full 48 channel capability (Rev 1 was “half HTR”) � As of this date, no issues – this board is functioning well 2 CMS June 2003

HTR Rev 3 (cont) HTR Rev 3 (cont) HTR Rev 3 (cont) Dual-LC O-to-E VME Stiffeners TTC mezzanine Deserializers 6 SLBs Xilinx XC2V3000-4 3 CMS June 2003

HTR Rev 3 HTR Rev 3 HTR Rev 3 • 30 boards delivered April 21 � Checkout consisted of o All systems except connectivity to SLB o Fiber links checked out at 1.7Gbaud bit rate (1.6Gbaud is CMS requirement) � Frame clock up to 2.0Gbaud bit rate and it stays synchronized � No BER yet…will do a lab measurement soon � 12 boards x 16 links ~200 links(~5% of total) with no problems � Used both onboard crystal oscillator and external clock for REFCLK � Minor adjustments will be needed for front panels, stiffeners, etc. � Will battle test these boards this year o May synchronous testbeam just completed o July testbeam o Vertical Slice tests to commence in the fall 4 CMS June 2003

Clocks and Synchronization Clocks and Synchronization Clocks and Synchronization • Clocking considerations can be divided into 2 parts: � Deserializers REFCLK: stability critical (80MHz frame rate) o Stability: must have a very low jitter – 30 to 40ps pkpk spec o Frequency: TI TLK2501 spec is 100ppm (8kHz) to lock � Measured ~350ppm (30kHz) needed to establish link � LHC variation expected to be few kHz � Once link is established, just needs to be stable (it’s a REFCLK!!!) o Phase: relationship to LHC clock totally irrelevant � Phase critical clock for pipeline synchronization o Must be in phase with LHC clock o Jitter spec is very lose – this clock is used inside FPGA for sequential logic 5 CMS June 2003

HCAL Clock Fanout Fanout HCAL Clock HCAL Clock Fanout • HTR clocks provided by a single 9U VME board � Chris Tully/Jeremy Mans from Princeton � Has fiber TTC input • Signals fanned out over Cat6 twisted pair: � TTC stream o To be used by each HTR and by DCC to decode commands & L1A � BC0 o To be used by SLBs to synchronize TPGs � “40MHz” clock o To be used by FPGA and SLBs to maintain pipeline � Comes from QPLL � “80MHz” clean clock o To be used for deserializer REFCLK � Comes from QPLL 6 CMS June 2003

Clock Distribution Clock Distribution Clock Distribution TTC fiber HTR HTR HTR O/E TTCrx TTC TTC TTC Brdcst<7:0>, BrcstStr, L1A TTC .. BC0 .. Cat6E BC0 .. or Cat7 .. distribution FPGA Cable TTCrx to 6 SLBs .. .. CLK40 CLK40 and to 2 Xilinx .. .. CLK80 QPLL CLK80 Princeton to Ref_CLK of Test Fanout SERDES 80.18 Points for .. (TLK2501) MHz Board RxCLK .. and RxBC0 7 CMS June 2003

TTC receiver - - TTCumd TTCumd TTC receiver TTC receiver - TTCumd • General purpose TTC receiver board (TTCumd) � TTCrx ASIC and associated PMC connectors • Will be used to receive TTC signal by HTR, DCC, and clock fanout boards • No signal receivers! � Copper/fiber receivers Princeton must be on the motherboard Fanout Card � Signal driven through TTC connectors • Tested successfully by Maryland, Princeton, BU groups 8 CMS June 2003

May Testbeam Testbeam Setup Setup May May Testbeam Setup • Lack of a QPLL or decent equivalent – had to improvise: � Front-end used commercial Cypress PLL o Matches GOL 100ps pkpk jitter spec � Fanout card o No clean 80MHz REFCLK, so provided 2 alternatives: � 2xLHC clock from crystal oscillator � High quality clock from HP signal and pulse generators � Jumper selectable on mezzanine cards o No clean 40MHz system clock � Just used 40MHz output from TTCrx chip anyway 9 CMS June 2003

May Testbeam Testbeam Experience Experience May May Testbeam Experience • To establish link: � FE o TTC 40MHz clock cleaned up by Cypress “roboclock” chip (Cy7B993) o FE reset signal to GOL � Fanout card o Fanout from onboard 80.1576MHz crystal oscillator for REFCLK o Fanout TTC 40MHz clock for system clock � HTR o TLK2501 link circuitry always enabled � Result: Fiber 1.6GHz link established ok o No problem locking – worked every time. 10 CMS June 2003

Testbeam Experience (cont) Experience (cont) Testbeam Testbeam Experience (cont) • Link stability - VERY PRILIMINARY, STILL STUDYING � Ran 10hr test on 48 fibers o 3 x 10 15 bits o 20% failed to maintain link o During synchronized beam running, sent reset between spills to ensure link � Similar tests at Maryland using TI eval board showed no link errors, similar number of bits sent • Curret plan � Study FE ? HTR link at FNAL this month o FNAL test stand setup this week � Investigate noise characteristics of H2 environment o H2 is clearly different than FNAL, Maryland and BU experience � Review of HTR and Fanout card o Will learn what we need to do from the above • Best guess � All tests in US indicate solid link, but experience in H2 disagree � Probably some kind of new noise component – figure out and correct. 11 CMS June 2003

HCAL TPG HCAL TPG HCAL TPG • Nothing new since May Electronics Week • TPG under development… � Preliminary FPGA code for TPGs done o LUT for linearization (downloadable), 0.5GeV steps, 255Gev max E T o E to E T and sums over as many as 7 channels � Not implemented in code yet…TBD o Muon window in E o BCID filter algorithm TBD from testbeams o Compression LUTs for output to SLBs � Utilization is ~50% of Virtex2 3000 o We are confident this chip will be sufficient � Simulation effort under way… • Latency issue � See below – we are working on this… 12 CMS June 2003

HTR TPG Commissioning HTR TPG Commissioning HTR TPG Commissioning • 2 Xilinx FPGAs per HTR � 3 SLBs per Xilinx � Each mounted on triPMC Xilinx connectors • Will test internal SLB connectivity to SLBs R SLB at UMD SLB C Xilinx � For signals and for SLB localbus connections T SLB • Need a scheme to test SLB HTR/RCT connectivity � Not just electrical! Also includes data integrity 13 CMS June 2003

HTR/RCT Testing HTR/RCT Testing HTR/RCT Testing • Will build PMC tester card to mount onto HTR � Host to 1 or more Wisconsin RCT Vitesse receiver boards Xilinx • Will run the signals from this RCT tester card back into Xilinx � Using 1 HTR, both FPGAs – SLB one source, one sink – to test Xilinx sending data from HTR to RCT RCT • Will try to engineer 3-SLB test to test single Xilinx ? SLB ? RCT 14 CMS June 2003

HTR Production HTR Production HTR Production • Full contingent of HTRs: 260 boards � Includes 10% spares, 20% spares for parts • Full production will begin after: � Testbeam demonstrates I/O works under battle conditions � Successful testing of the 6 SLB daughter card functions � Understanding of how to meet latency issues o We are still some clock ticks short, but firmware is still very immature for the TPG part of the HTR (see slides below) • Best guess: fall 2003 � There is no reason to hurry other than to finish with the R&D part of the project � Current board design will be final, perhaps some layout adjustments based on conclusion of testbeam effort 15 CMS June 2003

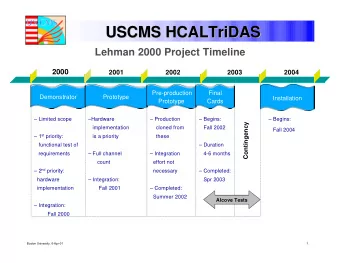

Overall Commissioning Schedule Overall Commissioning Schedule Overall Commissioning Schedule • Summer 2003 testbeam � Repeat previous test w/production prototype boards • Fall 2003 Slice tests � HCAL will join as schedule allows • 2003/2004 HCAL burn-in � Continue with firmware development/integration as needed • 2004/2005 Vertical Slice and magnet test � We will be ready � All HCAL TriDas production cards involved • October 05 beneficial occupancy of USC � Installation of all racks, crates, and cards � We do not anticipate any hardware integration o Should be all firmware / timing / troubleshooting 16 CMS June 2003

TPG Latency TPG Latency TPG Latency “ M inimizing the trigger latency” Item Latency • Current total 50 – 57 clocks TOF .5 � Very rough guesses HCAL Optics 1 o Many numbers have not been FE (CCA+QIE) 8-9 measured GOL 2 • Optimizations: Fiber Tx to HTRs 18 � Fiber cables need to be 90m? Deserializer 2-3 � HTR firmware needs optimization HTR Alignment 6 � Deserializer random latency fix HTR TPG path 5-10 � TPG cables changed to 15m will save SLB 3 1 tick TPG Cables 4 � Others…main efforts over next 6 TOTAL 50 - 57 months 17 CMS June 2003

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.