0.1 CMS HCAL T rigger and Readout Electronics Pro ject The - PDF document

0.1 CMS HCAL T rigger and Readout Electronics Pro ject The o v erall tec hnical co ordination for the HCAL trigger and readout electronics (T ri- D AS) pro ject will b e lo cated in the Maryland HEP group,

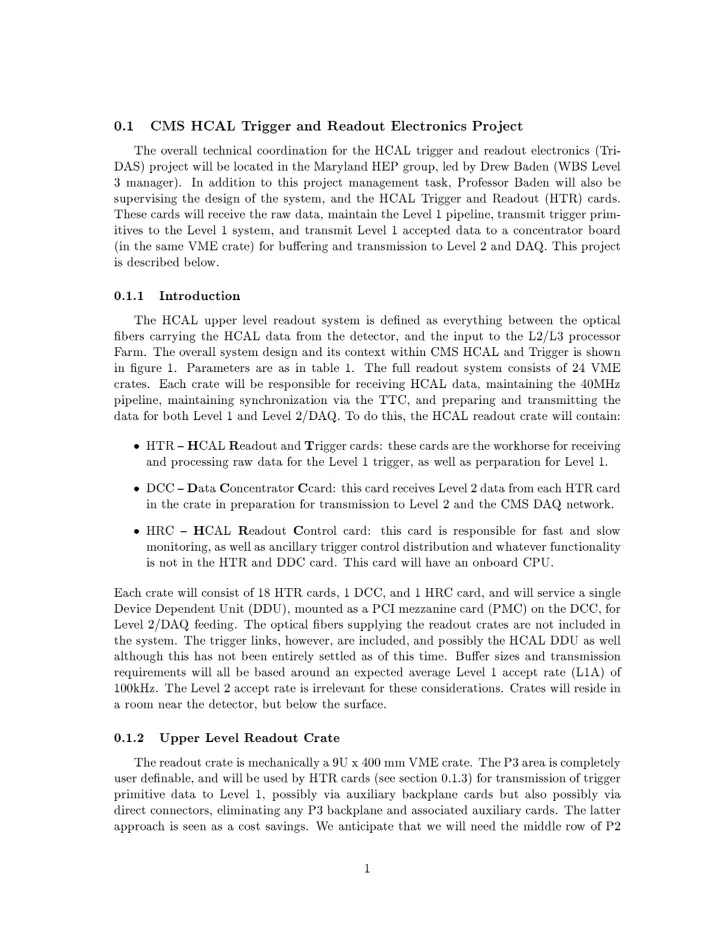

0.1 CMS HCAL T rigger and Readout Electronics Pro ject The o v erall tec hnical co ordination for the HCAL trigger and readout electronics (T ri- D AS) pro ject will b e lo cated in the Maryland HEP group, led b y Drew Baden (WBS Lev el 3 manager). In addition to this pro ject managemen t task, Professor Baden will also b e sup ervising the design of the system, and the HCAL T rigger and Readout (HTR) cards. These cards will receiv e the ra w data, main tain the Lev el 1 pip eline, transmit trigger prim- itiv es to the Lev el 1 system, and transmit Lev el 1 accepted data to a concen trator b oard (in the same VME crate) for bu�ering and transmission to Lev el 2 and D A Q. This pro ject is describ ed b elo w. 0.1.1 In tro duction The HCAL upp er lev el readout system is de�ned as ev erything b et w een the optical �b ers carrying the HCAL data from the detector, and the input to the L2/L3 pro cessor F arm. The o v erall system design and its con text within CMS HCAL and T rigger is sho wn in �gure 1. P arameters are as in table 1. The full readout system consists of 24 VME crates. Eac h crate will b e resp onsible for receiving HCAL data, main taining the 40MHz pip eline, main taining sync hronization via the TTC, and preparing and transmitting the data for b oth Lev el 1 and Lev el 2/D A Q. T o do this, the HCAL readout crate will con tain: HTR { H CAL R eadout and T rigger cards: these cards are the w orkhorse for receiving � and pro cessing ra w data for the Lev el 1 trigger, as w ell as p erparation for Lev el 1. DCC { D ata C oncen trator C card: this card receiv es Lev el 2 data from eac h HTR card � in the crate in preparation for transmission to Lev el 2 and the CMS D A Q net w ork. HR C { H CAL R eadout C on trol card: this card is resp onsible for fast and slo w � monitoring, as w ell as ancillary trigger con trol distribution and whatev er functionalit y is not in the HTR and DDC card. This card will ha v e an on b oard CPU. Eac h crate will consist of 18 HTR cards, 1 DCC, and 1 HR C card, and will service a single Device Dep enden t Unit (DDU), moun ted as a PCI mezzanine card (PMC) on the DCC, for Lev el 2/D A Q feeding. The optical �b ers supplying the readout crates are not included in the system. The trigger links, ho w ev er, are included, and p ossibly the HCAL DDU as w ell although this has not b een en tirely settled as of this time. Bu�er sizes and transmission requiremen ts will all b e based around an exp ected a v erage Lev el 1 accept rate (L1A) of 100kHz. The Lev el 2 accept rate is irrelev an t for these considerations. Crates will reside in a ro om near the detector, but b elo w the surface. 0.1.2 Upp er Lev el Readout Crate The readout crate is mec hanically a 9U x 400 mm VME crate. The P3 area is completely user de�nable, and will b e used b y HTR cards (see section 0.1.3) for transmission of trigger primitiv e data to Lev el 1, p ossibly via auxiliary bac kplane cards but also p ossibly via direct connectors, eliminating an y P3 bac kplane and asso ciated auxiliary cards. The latter approac h is seen as a cost sa vings. W e an ticipate that w e will need the middle ro w of P2 1

Front End Electronics FED Link to 1 Gbps fibers Level 2/DAQ (2 channels/fiber) 16 16 16 16 H D H H H H R C T T T T C C R R R R 18 HTR Cards T T C Level 2/Raw Data 200 Mbps per link Level 1 T rigger Data Vitesse,Copper Link, 20m cables, 1 Gbps Level 1 T rigger Figure 1: HCAL Readout and T rigger Crate. (for VME 32) for calibration and monitoring I/O, in v olving the particular implemen tation for the VME crate CPU card. HCAL data arriv es at eac h crate via optical �b er links whic h deliv ers data at appro x- imately 1 Gbps using the HP G-Links proto col. Eac h �b er will deliv er 2 or 3 c hannels w orth of data, to b e determined (it dep ends on whether w e run the �b ers at 800 Mbps or 1.6 Gbps). As describ ed ab o v e, there will b e a total of 18 HTR cards p er VME crate, and eac h HTR card is an ticipated to service 12 or 16 �b er inputs. Once arriv ed, the data is transformed, bu�ered, and pip elined in the HTR card. While in the pip eline, data is prepared (Lev el 1 \trigger primitiv es" are constructed) and transmitted to the Lev el 1 framew ork o v er copp er cables. These trigger primitiv e cables will carry appro ximately 2 \trigger to w ers" p er cable, with eac h trigger to w er constituting the signal in b oth the fron t and bac k section of an HCAL ph ysical to w er. This results in 8 cables p er HTR card, or 144 p er crate. The maxim um a v erage L1 accept rate is required to b e appro ximately 100kHz. If the L1 trigger passes the ev en t, the data stored in the pip eline bu�ers is collected, pro cessed and transmitted to the DCC for concen tration o v er simple c hannel-link copp er cables, one p er HTR card, where it w aits un til it can b e transferred to the D A Q system via DCC input cards. The DCC will hold appro ximately 1000 ev en ts in its in ternal bu�ers. The HR C card serv es as the in terface in the crates for b oth slo w and fast monitoring, as w ell as pro viding 2

HCAL readout crates 22-30 DCC cards p er crate 1 HR C cards p er crate 1 HTR cards p er crate 18 Input �b ers p er HTR 16 (12) HCAL c hannels p er �b er 2 (3) HCAL c hannels p er HTR 32 (36) HCAL c hannels p er crate 576 (648) TOT AL HCAL c hannels 13,824 TOT AL HTR cards 463 (413) TOT AL DCC cards 35 (26) T able 1: HCAL upp er lev el readout system parameters. a home for a TTC receiv er (TTCRx). TTC signals will b e deliv ered b y the HR C card to the 18 HTR cards in the crate, insuring sync hronization. 0.1.3 The HTR Card In this section w e discuss the HTR card, whic h consist of an input section for ra w data receiving, a Lev el 1 P ath con taining the Lev el 1 preparation and transmission capaibilit y to the Lev el 1 framew ork, and a Lev el 2/D A Q P ath consisting of the pip eline storage and Lev el 1 accept bu�ering used for transmission to the DCC. The HTR design tak es adv an tage of the curren t (and pro jected) a v ailabilit y of large a�ordable FPGA c hips with 6 3 10 gates and 10 I/O pins. This design (as opp osed to ha ving separate cards for � � the separate receiving and trigger functions) allo ws a merging of the readout and trigger prepro cessing functionalit y in to a single card, decreasing the engineering and pro duction costs (few er di�eren t cards) and allo wing for few er c hannels p er card (more cards with readout capabilit y). Input Section The HCAL calorimeter signals are digitized at eac h crossing (40 MHz). Eac h HCAL QIE c hannel will pro duce a 7-bit n um b er p er crossing as a measure of the energy in the HCAL elemen t. The digital 7-bit v alue is a v arian t �oating p oin t format, consisting of 2 bits of scale (exp onen t) and 5-bits of ADC digitization (man tissa). Since there are 4 capacitors p er QIE output, there will b e an additional 2 \CAP" bits transmitted with the QIE digital n um b er. The CAP bit will b e used to correct for the v ariation in eac h sample- and-hold capacitor. T ransmission will b e via �b er optics using the HP G-Links proto col running in enco ded mo de with 20 bit frames. Eac h frame will consist of the data from 2 QIE c hannels (2x7=14 bits) plus the 2 CAP bits for a total of 16 data bits p er frame. The rate of transmission will b e at 40 Mframes/sec for an total data transmission bandwidth of appro ximately 700Mbit/sec[1 ]. The �b ers whic h deliv er data to the HTR cards will plug in to the fron t panel. This sc heme alleviates engineering R&D necessary for successful input o v er the P3 bac kplane, 3

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.