Reconfigurable Computing Computing Reconfigurable Reconfigurable - PowerPoint PPT Presentation

Reconfigurable Computing Computing Reconfigurable Reconfigurable Architectures Architectures Reconfigurable Chapter 3.1 3.1 Chapter Prof. Dr.- -Ing. Jrgen Teich Ing. Jrgen Teich Prof. Dr. Lehrstuhl fr Hardware- -Software

Reconfigurable Computing Computing Reconfigurable Reconfigurable Architectures Architectures Reconfigurable Chapter 3.1 3.1 Chapter Prof. Dr.- -Ing. Jürgen Teich Ing. Jürgen Teich Prof. Dr. Lehrstuhl für Hardware- -Software Software- -Co Co- -Design Design Lehrstuhl für Hardware Reconfigurable Computing

2 Reconfigurable Computing Early Work Early Work

Gerald Estrin Fix- -Plus Machine Plus Machine Gerald Estrin Fix Vision of a restructurable computer system Pragmatic problem studies predict gains in computation speeds in a variety of computational tasks when executed on appropriate problem-oriented configurations of the variable structure computer. The economic feasibility of the system is based on utilization of essentially the same hardware in a variety of special purpose structures. This capability is achieved by programmed or physical restructuring of a part of the hardware. G. Estrin, B. Bussel, R. Turn, J Bibb (UCLA 1963) Reconfigurable Computing 3

Gerald Estrin Fix- -Plus Machine Plus Machine Gerald Estrin Fix Fixed plus Variable structure computer � Proposed by G. Estrin in 1959 � Consist of three parts � A high speed general purpose computer (the fix part F). � A variable part (V) consisting of various size high speed digital substructures which can be reorganized in problem- oriented special purpose configurations. � The supervisory control (SC) coordinates operations between the fix module and the variable module. � Speed gain over IBM7090 (2.5 to 1000) Reconfigurable Computing 4

Gerald Estrin Fix- -Plus Machine Plus Machine Gerald Estrin Fix The Fixed Part (F) � Was initially an IBM 7090, but could be any general purpose computer The Variable Part (V) � Made upon a set of problem-specific optimized functional units in the basic configuration (trigonometric functions, logarithm, exponentials, n-th power, roots, complex arithmetic, hyperbolic, matrix operation) � Two types of basic building blocks � The first basic element contains four The basic blocks amplifiers and associated input logic for signal inversion, amplification, or high- speed storage � The second basic block consists of ten diodes and four output drivers and is for combinatoric application Reconfigurable Computing 5

Gerald Estrin Fix- -Plus Machine Plus Machine Gerald Estrin Fix � The basic modules can be inserted into any of 36 positions on a mother board. � The connection between the modules is established through a wiring harness � Function Reconfiguration means changing some modules � Routing Reconfiguration means changing parts of the wiring harness The mother board The wiring harness Reconfigurable Computing 6

Gerald Estrin Fix- -Plus Machine Plus Machine Gerald Estrin Fix Estrin at work. Substantial effort on manual reconfiguration Reconfigurable Computing 7

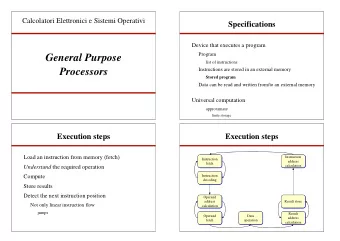

The Rammig Machine The Rammig Machine Goal Investigation of a system, which, with no manual or mechanical interference, permits the building, changing, processing and destruction of real (not simulated) digital Hardware Franz J. Rammig (University of Dortmund 1977) The concept resulted in the construction of a hardware editor Useful to observe a circuit under test (Hardware Emulation) Reconfigurable Computing 8

The Rammig Machine The Rammig Machine Implementation � Outputs of modules connected to selectors and selector outputs connected to module inputs. � Software-controlled module interconnection � Two main problems to solve: � Because the circuit is not hard-wired, a distortion of the behaviour is possible during reconfiguration � The timing is controlled by the circuit instead of being dictated by an observation mechanism. � A time-control must therefore be provided by delay circuits and inertial- delay circuits Reconfigurable Computing 9

Programmable Logic Programmable Logic Reconfigurable Computing 10

PALs and PLAs PALs and PLAs • Pre-fabricated building block of many AND/OR gates (or NOR, NAND) • "Personalized" by making or breaking connections between the gates Inputs Dense array of Dense array of AND gates Product OR gates terms Outputs Programmable Array Block Diagram for Sum of Products Form Reconfigurable Computing 11

PALs and PLAs PALs and PLAs Key to Success: Shared Product Terms Equations F0 = A + B C F1 = A C + A B Example: F2 = B C + A B F3 = B C + A Personality Matrix Input Side: Product Inputs Outputs 1 = asserted in term t erm F F F F A B C 0 1 2 3 0 = negated in term 0 1 1 0 A B 1 1 - - = does not participate Reuse 0 0 0 1 B C - 0 1 of Output Side: 0 1 0 0 A C 1 - 0 t erms 1 0 1 0 1 = term connected to output B C - 0 0 0 = no connection to output 1 0 0 1 A 1 - - Reconfigurable Computing 12

PALs and PLAs PALs and PLAs Example Continued - Unprogrammed device A B C All possible connections are available before programming F3 F0 F2 F1 Reconfigurable Computing 13

PALs and PLAs PALs and PLAs Example Continued - A B C Programmed part Unwanted connections are "blown" AB BC AC BC A Note: some array structures work by making connections rather than breaking them F3 F0 F2 F1 Reconfigurable Computing 14

PALs and PLAs PALs and PLAs Unprogrammed device Alternative representation for high fan-in structures Short-hand notation so we don't have to draw all the wires! X at junction indicates A B C D a connection AB AB CD Notation for implementation CD F0 = A B + A B Programmed device F1 = C D + C D CD+CD AB+AB Reconfigurable Computing 15

PALs and PLAs PALs and PLAs A B C Design Example ABC A Multiple functions of A, B, C B F1 = A B C C A F2 = A + B + C B F3 = A B C C ABC F4 = A + B + C ABC F5 = A ⊕ B ⊕ C ABC ABC F6 = A ⊕ B ⊕ C ABC ABC ABC F1 F2 F3 F4 F5 F6 Reconfigurable Computing 16

PALs and PLAs PALs and PLAs What is difference between Programmable Array Logic (PAL) and Programmable Logic Array (PLA)? PAL concept — implemented by Monolithic Memories AND array is programmable, OR array is fixed at fabrication A given column of the OR array has access to only a subset of the possible product terms PLA concept — Both AND and OR arrays are programmable Reconfigurable Computing 17

PALs and PLAs PALs and PLAs K-maps Design Example: BCD to Gray Code Converter Truth Table A A AB AB 00 01 11 10 00 01 11 10 CD CD A B C D W X Y Z 0 0 0 0 0 0 0 0 00 0 0 X 1 00 0 1 X 0 0 0 0 1 0 0 0 1 0 0 1 0 0 0 1 1 01 0 1 X 1 01 0 1 X 0 0 0 1 1 0 0 1 0 D D 0 1 0 0 0 1 1 0 0 1 X X 0 0 X X 11 11 0 1 0 1 1 1 1 0 C C 0 1 1 0 1 0 1 0 10 10 0 1 X X 0 0 X X 0 1 1 1 1 0 1 1 1 0 0 0 1 0 0 1 B B 1 0 0 1 1 0 0 0 K-map for W K-map for X X 1 0 1 0 X X X X 1 0 1 1 X X X X A A 1 1 0 0 X X X X AB AB 1 1 0 1 X X X X 00 01 11 10 00 01 11 10 CD CD 1 1 1 0 X X X X 00 0 1 X 0 00 0 0 X 1 1 1 1 1 X X X X 01 0 1 X 0 01 0 X 0 1 Minimized Functions: D D 1 1 X X 0 1 X X 11 11 C C W = A + B D + B C 10 10 1 1 X X 1 0 X X X = B C Y = B + C B B Z = A B C D + B C D + A D + B C D K-map for Y K-map for Z Reconfigurable Computing 18

PALs and PLAs PALs and PLAs Programmed PAL: A B C D A BD BC Minimized Functions: 0 W = A + B D + B C W = A + B D + B C BC X = B C X = B C 0 Y = B + C Y = B + C 0 Z = A B C D + B C D + A D + B C D Z = A B C D + B C D + A D + B C D 0 B C 0 0 A B C D BCD AD BCD 4 product terms per each OR gate W X Y Z Reconfigurable Computing 19

Complex Programmable Logic Devices Complex Programmable Logic Devices • Complex PLDs (CPLD) typically combine PAL combinational logic with Flip Flops – Organized into logic blocks connected in an interconnect matrix – Combinational or registered output • Usually enough logic for simple counters, state machines, decoders, etc. • CPLDs logic is not enough for complex operations • FPGAs have much more logic than CPLDs • e.g. Xilinx Coolrunner II, etc. Reconfigurable Computing 20

Xilinx Coolrunner CPLD Xilinx Coolrunner CPLD Function Block Interconnection matrix Interconnection matrix Macrocells for input Macrocells for output connection connection Reconfigurable Computing 21

Field Programmable Gate Arrays (FPGAs) Field Programmable Gate Arrays (FPGAs) Introduced in 1985 by Xilinx Programmable I/O Programmable I/O Roughly seen, an FPGA consists of: � A set of programmable macro cells � A programmable interconnection network � Programmable input/outputs � Subparts of a (complex) function are implemented in macro cells which are then connected to build the complete function � The I/O can be programmed to drive the macro cell's inputs or to be driven by the macro cell's outputs � Unlike traditional application-specific integrated Programmable Programmable Programmable routing Programmable routing macro cell macro cell circuit (ASIC), function is specified by the user after the device is manufactured � Physical structure and programming method is vendor-dependent Reconfigurable Computing 22

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.